### Altera's Avalon Interface

Stephen A. Edwards

**Columbia University**

Spring 2025

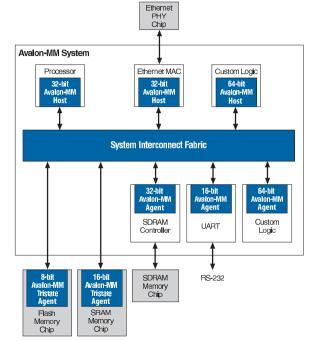

- Avalon Memory Mapped Host: Initiates transactions (e.g., processor)

Complex protocol requests access first

- Avalon Memory Mapped Agent: Responds to hosts (e.g., peripheral, memory)

Simpler protocol: just responds

Also manager/subordinate, M/S, initiator/target, requester/responder See Avalon Interface Specifications

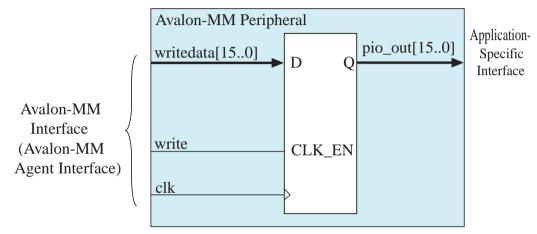

## The Simplest Agent Peripheral

Basically, "latch when I'm selected and written to."

## **Agent Signals**

For a 16-bit connection that spans 32 halfwords,

| Agent                      | Avalon            |   |            |

|----------------------------|-------------------|---|------------|

| $\leftarrow clk$           |                   | ( | Clock to A |

| $\leftarrow$ reset         |                   | I | Reset sig  |

| $\leftarrow$ chipselect    |                   | / | Asserted   |

| $\leftarrow address[4:0]$  |                   | I | Register a |

| $\leftarrow$ read          |                   | I | Bus is rea |

| $\leftarrow$ write         |                   | I | Bus is wri |

| $\Leftarrow$ writedata[15: | 0]                | I | Data fror  |

| $\leftarrow$ byteenable[1  | :0]               | ١ | Which by   |

| readdata[                  | 15:0] ⇒           | I | Data fror  |

|                            | $irq \rightarrow$ | I | nterrupt   |

|                            |                   |   |            |

Agent inal to Agent when bus accesses Agent address (in words) ading from Agent riting to Agent m bus to Agent vtes are being transferred m Agent to bus t request to processor

All are optional, as are many others for, e.g., flow-control and burst transfers.

# In SystemVerilog

| <pre>module myagent(input</pre> | logic |       | clk,        |

|---------------------------------|-------|-------|-------------|

|                                 | logic |       | reset,      |

|                                 | logic | [7:0] | writedata,  |

| -                               | logic |       | write,      |

| -                               | logic |       | chipselect, |

| input                           | logic | [2:0] | address);   |

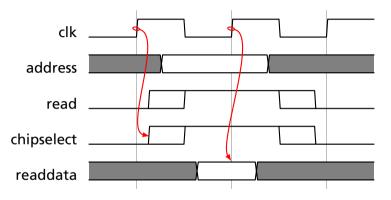

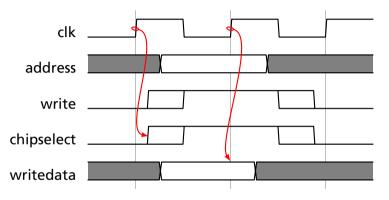

### **Basic Agent Read Transfer**

Bus cycle starts on rising clock edge

Data latched at next rising edge

Such a peripheral must be purely combinational

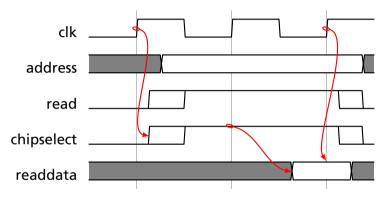

### Agent Read Transfer w/ 1 Wait State

Bus cycle starts on rising clock edge

Data latched two cycles later

Approach used for synchronous peripherals

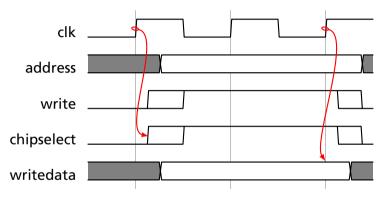

Basic Async. Agent Write Transfer

Bus cycle starts on rising clock edge Data available by next rising edge Peripheral may be synchronous, but must be fast Basic Async. Agent Write w/ 1 Wait State

Bus cycle starts on rising clock edge Peripheral latches data two cycles later For slower peripherals

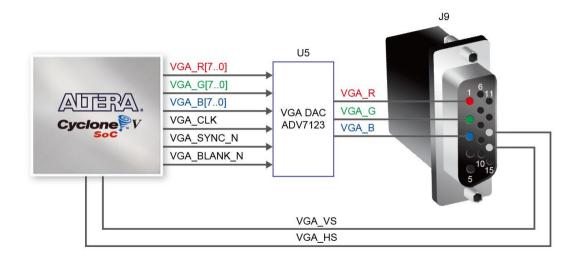

### VGA on the DE1-SoC

# The Vga\_ball Peripheral

| module vga_ball                           | input logic                                        | clk,<br>reset,<br>writedata,<br>write,<br>chipselect,<br>address,                |

|-------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|

|                                           | output logic [7:0]<br>output logic<br>output logic | VGA_R, VGA_G, VGA_B,<br>VGA_CLK, VGA_HS, VGA_VS,<br>VGA_BLANK_n,<br>VGA_SYNC_n); |

| <b>logic</b> [10:0]<br><b>logic</b> [9:0] | hcount;<br>vcount;                                 |                                                                                  |

| <b>logic</b> [7:0]                        | background_r, ba                                   | ackground_g, background_b;                                                       |

| vga_counters                              | <pre>counters(.clk50(cll</pre>                     | k), .*);                                                                         |

### **Register Map**

#### Offset 7 ··· 0 Meaning

| 0 | Red   |

|---|-------|

| 1 | Green |

| 2 | Blue  |

Red component of background color (0–255) Green component of background color (0–255) Blue component of background color (0–255)

### The Vga\_ball Peripheral

```

always ff @(posedge clk)

if (reset) begin

background_r <= 8'h0;

background_g <= 8'h0;

background_b <= 8'h80;</pre>

end else if (chipselect && write)

case (address)

3'h0 : background_r <= writedata;

3'h1 : background g <= writedata:

3'h2 : background_b <= writedata:

endcase

always comb begin

\{VGA_R, VGA_G, VGA_B\} = \{8'h0, 8'h0, 8'h0\};

if (VGA_BLANK_n)

if (hcount[10:6] == 5'd3 \&\& vcount[9:5] == 5'd3)

\{VGA_R, VGA_G, VGA_B\} = \{8'hff, 8'hff, 8'hff\}

else

{VGA_R, VGA_G, VGA_B} = {background_r, background_g, background_b};

end

```