### **CSEE W3827**

# Fundamentals of Computer Systems Homework Assignment 3 Solutions

Prof. Stephen A. Edwards

Columbia University

Due October 18th, 2011 at 10:35 AM

Show your work for each problem; we are more interested in how you get the answer than whether you get the right answer.

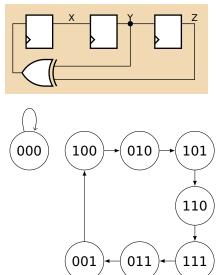

1. (10 pts.) The circuit below is called a linear-feedback shift register. Draw a bubble-and-arc diagram representing its behavior. Start from both the state X = 1, Y = 0, Z = 0 and the all-zeros state.

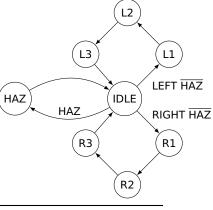

2. (15 pts.) The 1965 Ford Thunderbird had sequential turn signals that would light sequentially. Design an FSM that implements such signals.

Your machine has three inputs: LEFT, RIGHT, and HAZARD, and six light outputs, LA, LB, LC, RA, RB, and RC.

When HAZARD is active, your machine should alternate between all lights on and all lights off.

Otherwise, when LEFT is active, LA, then LA and LB, then all the L's should light, then all turn off, then repeat. RIGHT should do the same thing for the R outputs. Assume LEFT and RIGHT are mutually exclusive.

- (a) Draw a Moore-style bubble-and-arc diagram for your machine.

- (b) Draw a transition table for your machine with symbolic state names.

- (c) Draw an output table for your machine expressing the L's and the R's in terms of your states.

| S    | Н | L | R | S'   |

|------|---|---|---|------|

| IDLE | 0 | 0 | 0 | IDLE |

| IDLE | 1 | Χ | Χ | HAZ  |

| IDLE | 0 | 1 | Χ | L1   |

| IDLE | 0 | Χ | 1 | R1   |

| HAZ  | Χ | Χ | Χ | IDLE |

| L1   | Χ | Χ | Χ | L2   |

| L2   | Χ | Χ | Χ | L3   |

| L3   | Χ | Χ | Χ | IDLE |

| R1   | Χ | Χ | Χ | R2   |

| R2   | Χ | Χ | Χ | R3   |

| R3   | Χ | Χ | Χ | IDLE |

| S    | LC | LB | LA | RA | RB | R |

|------|----|----|----|----|----|---|

| IDLE | 0  | 0  | 0  | 0  | 0  | ( |

| HAZ  | 1  | 1  | 1  | 1  | 1  | 1 |

| L1   | 0  | 0  | 1  | 0  | 0  | ( |

| L2   | 0  | 1  | 1  | 0  | 0  | ( |

| L3   | 1  | 1  | 1  | 0  | 0  | ( |

| R1   | 0  | 0  | 0  | 1  | 0  | ( |

| R2   | 0  | 0  | 0  | 1  | 1  | ( |

| R3   | 0  | 0  | 0  | 1  | 1  | - |

|      |    |    |    |    |    |   |

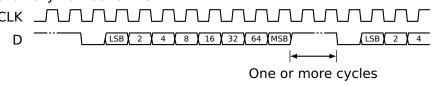

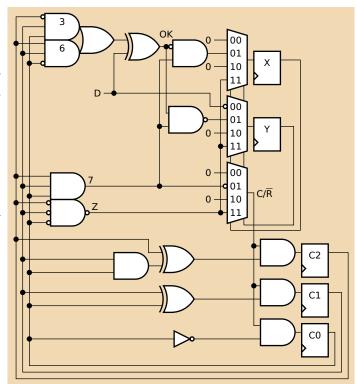

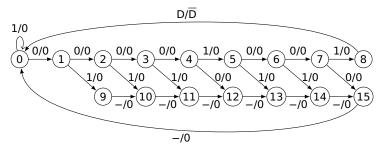

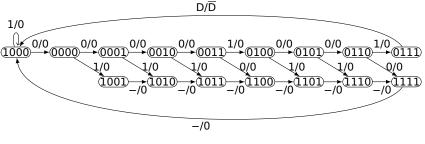

3. (20 pts.) Design a circuit for part of an HTML parser that signals when an ASCII character "H" (01001000 in binary) has arrived on a serial link. The rising edge of the clock indicates when the next bit is present on the input. Between bytes, the input stays high and the clock continues running. A byte starts with a single 0 start bit followed by the bits, LSB first, followed by a single 1 stop bit. The next byte could start immediately after the stop bit, or after an arbitrary number of 1's.

Assume the data stream starts in the idle state (i.e., not in the middle of a byte), then start looking for a start bit followed by the bit pattern, followed by a stop bit. Make sure your machine stays synchronized, i.e., so it will not erroneously report an H that crosses a stop/start bit boundary.

Consider modifying a shift register for part of your circuit.

Trick: use the start bit to indicate when a complete byte has passed

| State      | Comment                           |

|------------|-----------------------------------|

| 1111111111 | Reset state                       |

| 0111111111 | Start bit received                |

| 0011111111 | 0 (LSB)                           |

| 0001111111 | 0                                 |

| 0000111111 | 0                                 |

| 1000011111 | 1                                 |

| 0100001111 | 0                                 |

| 0010000111 | 0                                 |

| 1001000011 | 1                                 |

| 0100100001 | 0 (MSB)                           |

| 1010010000 | Stop bit: check inner 8 and reset |

| 0111111111 | Start bit received                |

|            |                                   |

Needs to reset in the all-1's state.

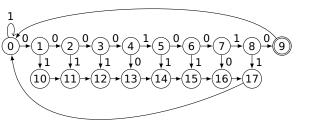

## Moore Machine

|    |        | _  |   |    | _ |   |    |     |

|----|--------|----|---|----|---|---|----|-----|

|    |        |    |   |    |   |   |    |     |

|    |        |    |   |    |   |   |    |     |

| S  | XY ccc |    |   |    |   |   |    |     |

| 0  | 00     |    |   |    |   |   |    |     |

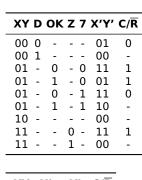

| 1  | 01000  | XY | D | OK | Z | 7 | ΧΎ | C/R |

| 2  | 01001  | 00 | 0 |    |   |   | 01 | 0   |

| 3  | 01010  |    | • | -  | - | - |    | U   |

|    |        | 00 | 1 | -  | - | - | 00 | -   |

| :  |        | 01 | - | 0  | - | 0 | 11 | 1   |

| 8  | 01111  | 01 | - | 1  |   | 0 | 01 | 1   |

| 9  | 10     | 01 | - | 0  | - | 1 | 11 | 0   |

| 10 | 11 001 | 01 | - | 1  | - | 1 | 10 | -   |

|    |        | 10 | _ | _  | _ | _ | 00 | _   |

| 11 | 11010  | 11 | _ | _  | 0 | _ | 11 | 1   |

| :  | :      | 11 | _ | _  | 1 | _ | 00 | -   |

|    |        |    |   |    | _ |   |    |     |

| 16 | 11 111 |    |   |    |   |   |    |     |

| 0                          | -                                                  |

|----------------------------|----------------------------------------------------|

| 1                          | (                                                  |

| 0<br>1<br>0<br>1           |                                                    |

| 1                          | 10                                                 |

| 1                          | Τ.                                                 |

| 0                          |                                                    |

| 1                          | 1.                                                 |

| 0                          | 4                                                  |

| 1                          | 12                                                 |

| 0<br>1<br>0<br>1<br>0<br>1 | 13                                                 |

| 1                          |                                                    |

| 0                          | (                                                  |

| 1                          | 14                                                 |

| 0<br>1<br>0                | 10<br>10<br>11<br>12<br>13<br>14<br>14<br>16<br>16 |

| 1                          | 1                                                  |

| 7                          | 14                                                 |

| 1<br>0<br>1                | Τ.                                                 |

| 1                          | Č                                                  |

| 0                          |                                                    |

| 1                          | 17                                                 |

| -                          | (                                                  |

| 0<br>1<br>-<br>-           | 11                                                 |

| -                          | 12                                                 |

| -                          | 13                                                 |

| _                          | 14                                                 |

| _                          | 15                                                 |

| -                          | 16                                                 |

| -                          | 17                                                 |

| -                          | 13<br>12<br>13<br>14<br>15<br>16<br>17             |

|                            |                                                    |

S

D

s'

| XY | Χ'                  | Y'                       | C/R            |

|----|---------------------|--------------------------|----------------|

| 00 | 0                   | $\overline{D}$           | 0              |

| 01 | $7 \ \overline{OK}$ | $\overline{\text{OK 7}}$ | 7              |

| 10 | 0                   | 0                        | 0              |

| 11 | Z                   | $\overline{Z}$           | $\overline{Z}$ |

|    |                     |                          |                |

## Mealy Machine

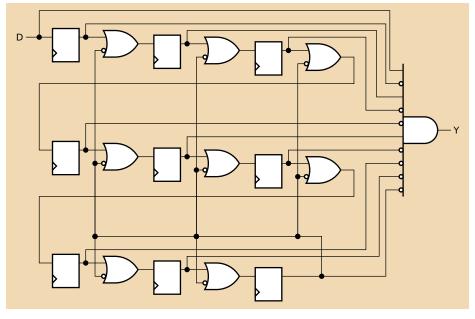

$$Y = \overline{DQ_3}Q_2Q_1Q_0$$

$$D_3 = Q_3(D + Q_2 + Q_1 + Q_0) + \overline{Q_3}Q_2Q_1Q_0 + \overline{Q_3}Q_2\overline{Q_1}Q_0 + \overline{Q_3}Q_2\overline{Q_1}Q_$$

$$D_{1} = Q_{1} \oplus Q_{0}$$

$$D_{0} = \overline{Q_{0}}(\overline{Q_{3}} + Q_{2} + Q_{1})$$

(30 pts.) Design a synchronous 7-bit counter that counts 0-59 in BCD, i.e., the seconds digits of a "binary clock." There are seven outputs,  $Q_1$ ,  $Q_2$ ,  $Q_4$ ,  $Q_8$ ,  $Q_{10}$ ,  $Q_{20}$ , and  $Q_{40}$ , each driven by a D flip-flop.

(a) Write Boolean expressions of the form  $D_i = Q_i \oplus (\cdots)$  for each flip-flop's input.  $(\oplus \text{ is XOR})$

$$\begin{array}{rcl} D_1 & = & \overline{Q_1} \\ D_2 & = & Q_2 \oplus (\overline{Q_8}Q_1) \\ D_4 & = & Q_4 \oplus (Q_2Q_1) \\ D_8 & = & Q_8 \oplus (Q_4Q_2Q_1 + Q_8Q_1) \\ D_{10} & = & Q_{10} \oplus (Q_8Q_1) \\ D_{20} & = & Q_{20} \oplus (\overline{Q_{40}}Q_{10}Q_8Q_1) \\ D_{40} & = & Q_{40} \oplus ((Q_{40} + Q_{20})Q_{10}Q_8Q_1) \end{array}$$

(b) Write a small program to test your expressions and attach both it and its output. I wrote a C program like the one below, but you may use any language.

```

#include <stdio.h>

```

```

The output:

int main()

0 000 0000

int i, q1, q2, q4, q8, q10, q20, q40,

1 000 0001

d1, d2, d4, d8, d10, d20, d40;

2 000 0010

q1 = q2 = q4 = q8 = q10 = q20 = q40 = 0;

3 000 0011

for (i = 0 : i < 121 : ++i) {

4 000 0100

printf("%2d %c%c%c %c%c%c\n", i, ... );

5 000 0101

d1 = -a1:

6 000 0110

d2 = q2 ^ (q1 \& ~q8);

7 000 0111

d4 = q4 ^ (q1 \& q2);

8 000 1000

d8 = q8 ^ (q4 & q2 & q1 | q8 & q1);

9 000 1001

d10 = q10 ^ (q8 \& q1);

10 001 0000

d20 = q20 ^ (q10 & ~q40 & q8 & q1);

d40 = q40 ^ ((q20 | q40) & q10 & q8 & q1);

19 001 1001

q1 = d1; q2 = d2; q4 = d4;

20 010 0000

q8 = d8; q10 = d10; q20 = d20;

q40 = d40:

59 101 1001

60 000 0000

return 0:

```

#### 5. (10 pts.)

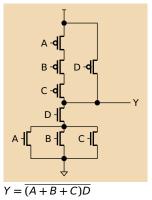

(a) Write a Boolean expression for the function of the following static CMOS gate.

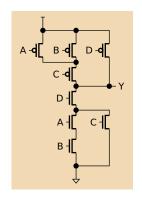

(b) Draw the schematic for a static CMOS gate that implements  $Y = \overline{(AB + C)D}$

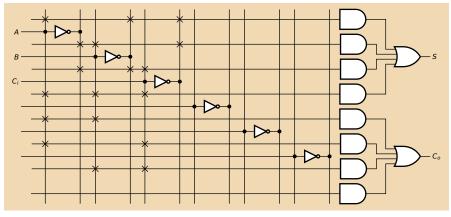

6. (15 pts.) Show how to implement a full adder using the following PLA. The inputs should be A, B, and  $C_i$  and the outputs S and  $C_o$  Hint: write the functions for the sum and carry in sum-of-products form then draw crosses to indicate connections on the AND plane.

$$S = A \oplus B \oplus C_i = A\overline{B}\overline{C_i} + \overline{A}B\overline{C_i} + \overline{A}\overline{B}C_i + ABC_i$$

$$C_0 = AB + AC_i + BC_i$$