# Why ESP?

Heterogeneous systems are pervasive Integrating accelerators into a SoC is hard Doing so in a scalable way is very hard Keeping the system **simple to program** is even harder

### ESP makes it easy

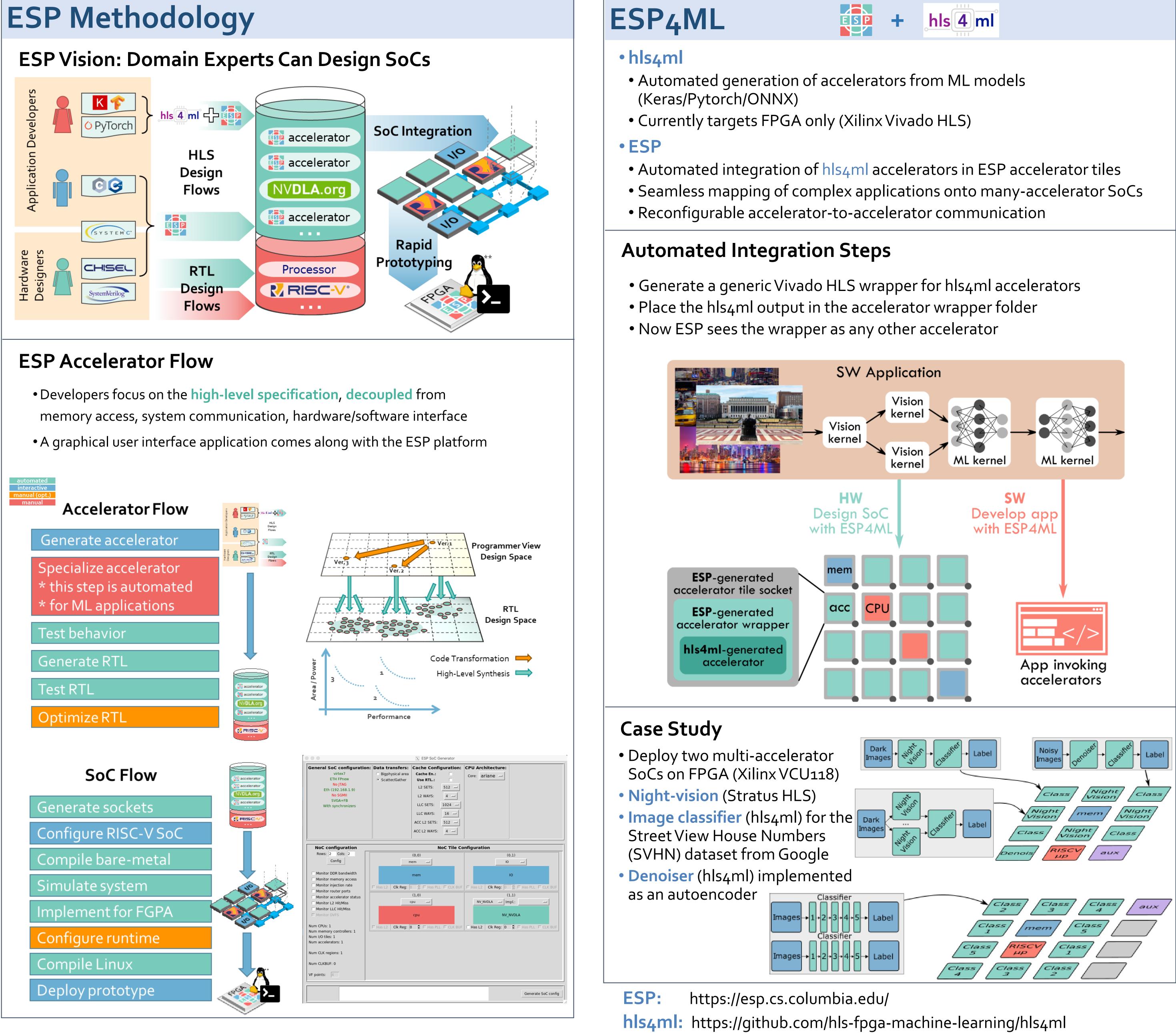

ESP combines a scalable architecture with a flexible methodology ESP enables several accelerator design flows and takes care of the SW/HW integration

We hope that ESP will serve the OSH community as a Platform to develop software for RISC-V and accelerators for any application domain

## **ESP** Architecture

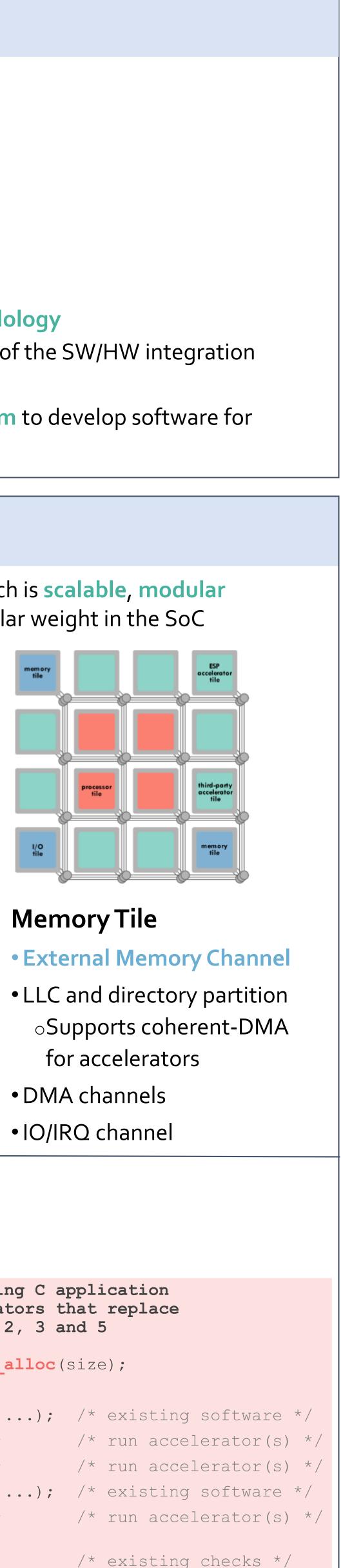

The ESP architecture implements a **distributed** system, which is **scalable**, **modular** and heterogeneous, giving processors and accelerators similar weight in the SoC

- RISC-V Processors

- Many-Accelerator

- Distributed Memory

- Multi-Plane NoC

### **Processor Tile**

- Processor off-the-shelf • RISC-V Ariane (64 bit) SPARC V8 Leon<sub>3</sub> (32 bit) L1 private cache

- L2 private cache

- IO/IRQ channel

- Accelerator config. registers, interrupts, flush, UART, ...

### Accelerator Tile

### Accelerator Socket w/ Platform Services

Direct-memory-access Run-time selection of coherence model:

- Fully coherent

- LLC coherent

- Non coherent

- User-defined registers • Distributed interrupt

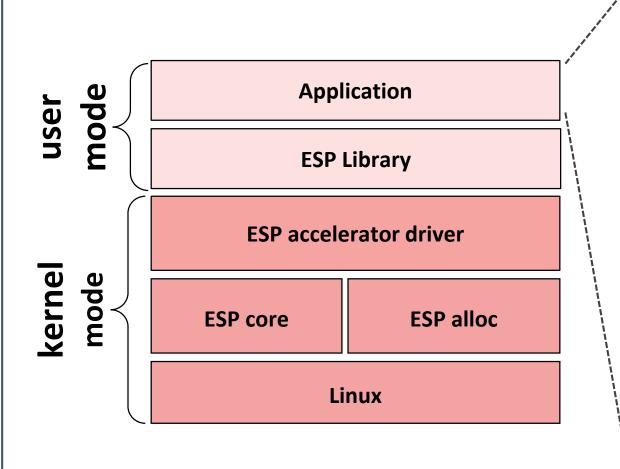

### ESP Software API

- Generation of device driver and unit-test application

- Seamless shared memory

| , | <pre>// Example of existing C appli // with ESP accelerators that // software kernels 2, 3 and 5 {</pre> | rep |

|---|----------------------------------------------------------------------------------------------------------|-----|

|   | <b>int *</b> buffer = <b>esp_alloc</b> (size                                                             | );  |

|   | <b>for</b> () {                                                                                          |     |

|   | kernel_1(buffer,); /*                                                                                    | exi |

|   | <b>esp_run</b> (cfg_k2); /*                                                                              | rur |

|   | <pre>esp_run(cfg_k3); /*</pre>                                                                           | rur |

|   | <pre>kernel_4(buffer,); /*</pre>                                                                         | exi |

|   | <b>esp_run</b> (cfg_k5); /*                                                                              | rur |

|   | <pre>validate(buffer); /*</pre>                                                                          | exi |

|   | esp_cleanup(); /*                                                                                        | fre |

| 1 | }                                                                                                        |     |

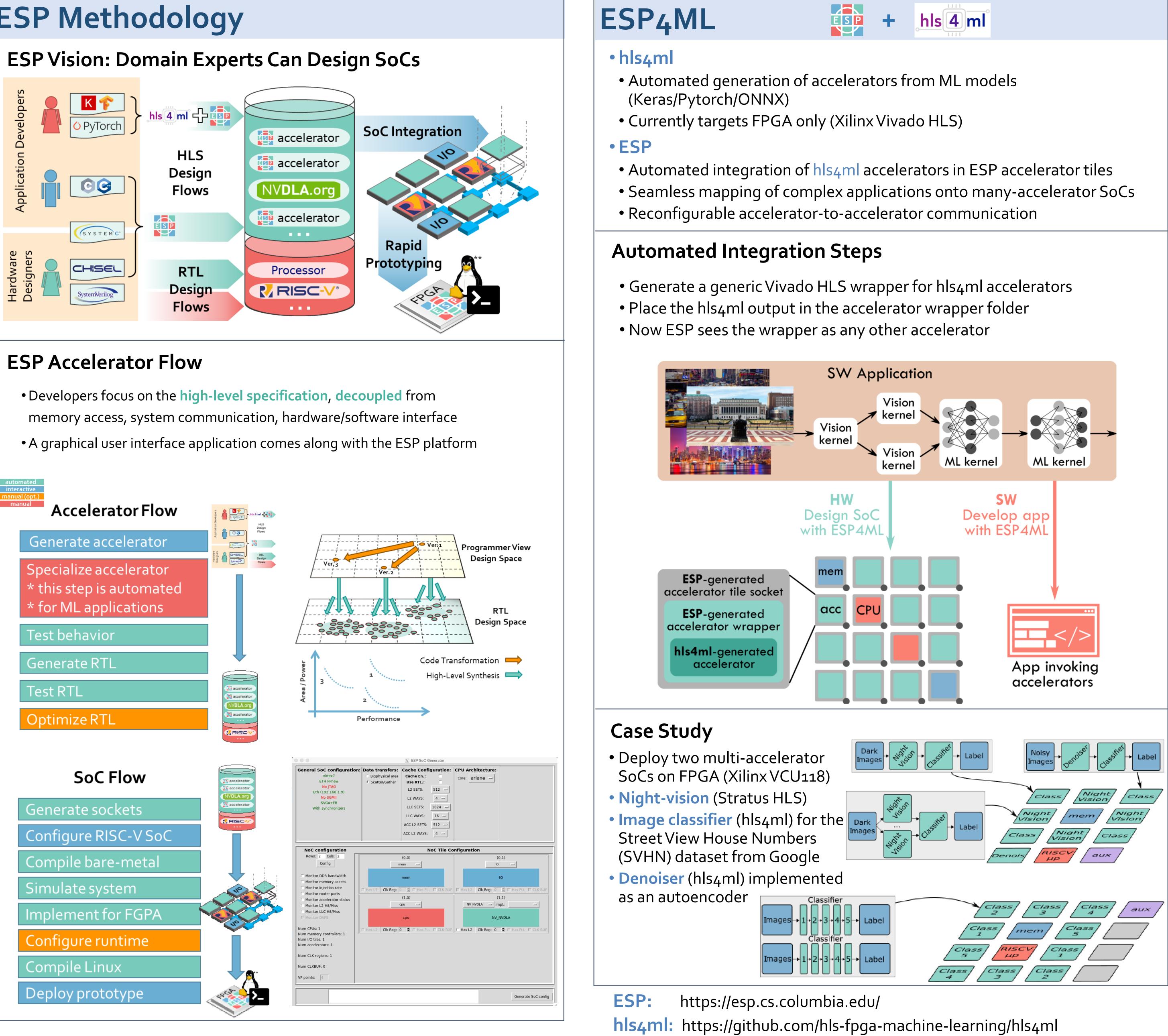

# **ESP for Machine Learning**

Davide Giri, Kuan-Lin Chiu, Giuseppe Di Guglielmo, Paolo Mantovani, and Luca P. Carloni Department of Computer Science · Columbia University, New York

ee memory \*/