# User Core Templates Reference Guide

April 2003

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, Logi-BLOX, Logic Cell, LogiCORE, LogicProfessor, MicroBlaze, MicroVia, MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMART-Switch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACT*step*, XACT*step* Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418;

4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068;5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5.821,772; 5.821,774; 5.825,202; 5.825,662; 5.825,787; 5.828,230; 5.828,231; 5.828,236; 5.828,608; 5.831,448; 5.831,460; 5.831,845; 5.831,907; 5.835,402; 5.838,167; 5.838,901; 5.838,954; 5.841,296; 5.841,867; 5.844,422; 5.844,424; 5.844,829; 5.844,844; 5.847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2003 Xilinx, Inc. All Rights Reserved.

# **User Core Templates Reference Guide**

The following table shows the revision history for this document.

|          | Version | Revision                |

|----------|---------|-------------------------|

| 11/19/02 | 1.0     | Initial release.        |

| 1/17/03  | 1.1     | Updated for EDK SP3     |

| 4/1/03   | 1.2     | Updated for EDK 3.2 SP1 |

# Chapter 1

# Adding User Cores to Your Embedded System

# **Overview**

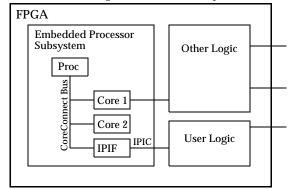

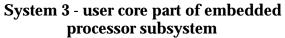

There are several types of user logic associated with FPGA designs that incorporate an embedded processor subsystem. User logic may be unrelated to the embedded processor subsystem, it may have a weak coupling to the processor, or it may be included as an integral part of the processor subsystem. There are also several configurations that can be used to connect user cores and user logic to an embedded subsystem. Some of these configurations are shown below in Figure 1-1. This document deals primarily with the creation and use of a user core that is intended to be included as part of the embedded processor subsystem. This configuration is shown as System 3 in Figure 1-1.

Definitions of the terms used in the document are:

- FPGA the entire design to be loaded into the FPGA, consisting of an embedded processor subsystem (created by the platform generation tools) and other logic (created by the user).

- Embedded processor subsystem a design described in an MHS (Microprocessor Hardware Specification) file and generated with the platform generation tools. This typically consists of one or more processors, bus peripherals, bus arbiters, bridges, support logic (such as reset circuitry), and user cores.

- User core a core designed to attach to an embedded processor bus, such as OPB or PLB. From the viewpoint of the platform generation tools, the user core looks just like the Xilinx-supplied embedded system cores.

- User logic to simplify the process of attaching a user core to a CoreConnect bus, the user core can make use of a portable, predesigned bus interface (called the IP Interface, IPIF) that takes care of the bus interface signals, bus protocol, and other interface issues. The IPIF presents an interface to the user logic called the IP InterConnect (IPIC). User logic is logic that has been designed with an IPIC interface to make use of the IPIF bus attachment and other services. User logic that is designed with an IPIC has the advantage that it is portable and can be easily reused on different processor buses by changing the IPIF to which it is attached.

- User core template the user core template simplifies the task of attaching the IPIF to user logic. The user core template is a VHDL file that instantiates the IPIF and provides most of the VHDL code required to create a user core. The template provides a place to instantiate the user logic, which can be VHDL or a black box created from verilog, schematic, etc. There are a total of nine user core templates that address specific bus attachment needs. They will be described in greater detail below.

- Other logic logic that is not included as part of the embedded processor subsystem. It may have some connection to the embedded subsystem, but it typically does not have a bus interface such as an IPIC and it is not considered a bus peripheral, although a bus peripheral may provide an interface from the embedded system to the other logic.

FPGA Embedded Processor Subsystem Proc Subsystem Core 1 Core 2 Core 3

System 1 - no user core

# System 2 - user logic external to embedded processor subsystem

# **OPB User Core Templates**

The user core templates provide a convenient way to get your user logic attached to the OPB bus. These templates are provided as VHDL source and provide a framework into which user logic can be instantiated. Each user core template contains an instantiation of an IPIF (IP Interface). The IPIF instantiated in each template is customized so that only the features and services required by the template are used. For example, the user core template that provides a simple OPB slave interface uses only the slave signal set and bus attachment logic required for a slave interface.

The user core templates are provided as starting points for building custom OPB peripherals. Each template has some degree of parameterization as well, so the best way to use the templates is to find a template that is closest to the features and services required by your core and customize from there.

Templates are named according to the features that are provided by the template. For OPB slaves, there are four templates that provide varying degrees of services for the user. OPB slave templates are denoted by the ssp < n > (Slave Services Package *n*) suffix, where in general the higher number indicates inclusion of more services. Table 1-1 below shows the OPB slave templates available and the services provided by each.

Table 1-1: OPB User Core Templates (Slave)

|               | OPB Slave<br>Attach-<br>ment | Address<br>Decode | Module<br>Identifica-<br>tion<br>Register | Reset<br>Register | Device<br>Interrupt<br>Controller | R/W FIFOs | R/W Packet<br>FIFOs |

|---------------|------------------------------|-------------------|-------------------------------------------|-------------------|-----------------------------------|-----------|---------------------|

| opb_core_ssp0 | •                            | ٠                 | •                                         | ٠                 |                                   |           |                     |

| opb_core_ssp1 | •                            | ٠                 | •                                         | •                 | •                                 |           |                     |

| opb_core_ssp2 | •                            | ٠                 | •                                         | ٠                 | •                                 | •         |                     |

| opb_core_ssp3 | •                            | •                 | •                                         | •                 | •                                 |           | •                   |

For OPB masters, there are five templates that provide varying degrees of services for the user. OPB master templates are denoted by the msp < n > (Master Services Package *n*) suffix, where in general the higher number indicates inclusion of more services. Table 1-2 below shows the OPB master templates available and the services provided by each.

Table 1-2: OPB User Core Templates (Master)

|               | OPB<br>Slave<br>Attach-<br>ment | Address<br>Decode | Module<br>Identif-<br>cation<br>Register | Reset<br>Register | Device<br>Interrupt<br>Control-<br>Ier | R/W<br>FIFOs | R/W<br>Packet<br>FIFOs | OPB<br>Master<br>Attach-<br>ment | Simple<br>DMA | DMA with<br>scatter/<br>gather |

|---------------|---------------------------------|-------------------|------------------------------------------|-------------------|----------------------------------------|--------------|------------------------|----------------------------------|---------------|--------------------------------|

| opb_core_msp0 |                                 |                   |                                          |                   |                                        |              |                        | •                                |               |                                |

| opb_core_msp1 | •                               | •                 | •                                        | •                 |                                        |              |                        | •                                |               |                                |

| opb_core_msp2 | •                               | •                 | •                                        | •                 | •                                      |              |                        | •                                |               |                                |

| opb_core_msp3 | •                               | •                 | •                                        | •                 | •                                      | ●            |                        | •                                | •             |                                |

| opb_core_msp4 | •                               | •                 | •                                        | •                 | •                                      |              | •                      | •                                |               | •                              |

# **Creating a User Core**

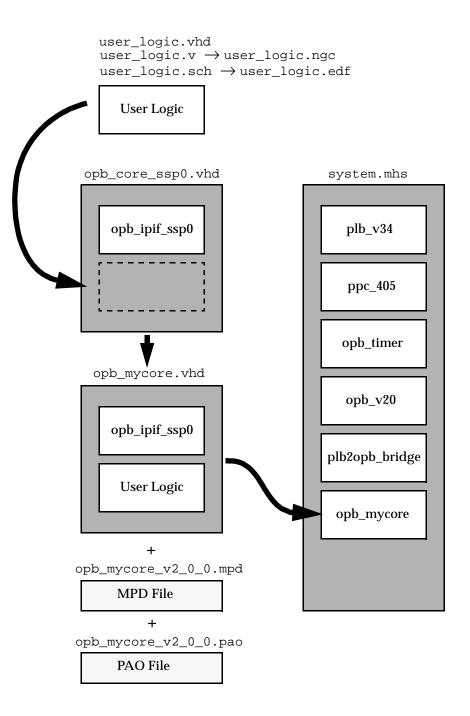

The process of creating a user core from the OPB user core templates is shown in Figure 1-2. First, an appropriate template is selected based on the level of services required. Then, the user logic is inserted into the template and the template file names and entities

are renamed if desired. Finally, the template MPD and PAO files are modified as necessary and the user core is instantiated in the system's MHS file. For definitions of the MPD, PAO, and MHS file formats, see the *Embedded System Tools Guide* document (est\_guide.pdf) in the \$EDK/doc directory. Some important points about this process are:

Figure 1-2: OPB User Core Process

- The User Logic can either be a VHDL entity or any type of black box (fixed netlist) recognized by the Xilinx implementation tools. Black boxes are either NGC files created by XST (Xilinx Synthesis Technology) or EDIF files created by a variety of sources.

- Each template directory contains a VHDL source template, an MPD template, and a

PAO template. These files are located in the following directories (the template for Slave Services Package 0 is used for this example): - opb\_core\_ssp0.vhd is in: \$EDK/hw/user\_core\_templates/myip/opb\_core\_ssp0\_v1\_00\_a/hdl/vhdl/ - opb\_core\_ssp0\_v2\_0\_0.mpd is in: \$EDK/hw/user\_core\_templates/myip/opb\_core\_ssp0\_v1\_00\_a/data/ - opb\_core\_ssp0\_v2\_0\_0.pao is in: \$EDK/hw/user\_core\_templates/myip/opb\_core\_ssp0\_v1\_00\_a/data/

- Note that the version number in the MPD and PAO file names are the Platform Specification File (PSF) format version, not the core version number. The current PSF format version is v2.0.0.

- Lines in the templates that can be customized by the user (to change the peripheral name, for example) contain the comment --USER--. Searching for --USER-- in the VHDL, MPD, and PAO will guide the user to all lines that may require modification.

- For detailed instructions on how to use a particular template, refer to the chapter on that template.

# IPIC Interface (v3.00a)

To effectively use the OPB user core templates, the user logic should be designed with an IP Interconnect (IPIC). The IPIC is a simple set of signals that connect the user logic to the IPIF logic. The IPIC is common to all Xilinx IPIFs, so user logic that is designed with an IPIC can be easily ported to a different bus simply by using the appropriate IPIF (and user core template). IPIFs currently exist for the two Xilinx-supported CoreConnect buses, OPB and PLB. The IPIC is designed so that only the subset required in a particular application can be used. For simple slaves, only the slave interface signals are used, while for simple masters, only the master signals are used. This simplifies use of the IPIC and reduces the complexity of interfacing to simple peripherals.

# **IPIC Signal Set**

The signal set for slave and master peripherals is shown below in.

| Signal Name   | Range                       | I/O | Description                                    | Page |

|---------------|-----------------------------|-----|------------------------------------------------|------|

| Bus2IP_Addr   | 0:C_ <bus>_AWIDTH-1</bus>   | Ι   | Address to User Logic                          |      |

| Bus2IP_BE     | 0:C_ <bus>_DWIDTH/8-1</bus> | Ι   | Byte enables to User Logic                     |      |

| Bus2IP_Burst  | none                        | Ι   | Burst-mode qualifier to User Logic             |      |

| Bus2IP_Clk    | none                        | Ι   | IPIC clock. Identical to the <bus> clock</bus> |      |

| Bus2IP_CE     | 0:C_NUM_CE-1                | Ι   | "chip" enable to User Logic                    |      |

| Bus2IP_CS     | 0:C_NUM_CS-1                | Ι   | "chip" select to User Logic                    |      |

| Bus2IP_Data   | 0:C_ <bus>_DWIDTH-1</bus>   | Ι   | Data to User Logic                             |      |

| Bus2IP_Freeze | none                        | Ι   | Tells the User Logic to freeze                 |      |

| Bus2IP_RdCE   | 0:C_NUM_CE-1                | Ι   | Read enables to User Logic                     |      |

| Bus2IP_Reset  | none                        | Ι   | Signal to reset the User Logic                 |      |

| Bus2IP_RNW    | none                        | Ι   | Read/Not Write Signal to User Logic            |      |

| Bus2IP_WrCE   | 0:C_NUM_CE-1                | Ι   | Write enables to User Logic                    |      |

| IP2Bus_Ack    | none                        | 0   | Acknowledgement from User Logic                |      |

| IP2Bus_Data   | 0:C_ <bus>_DWIDTH-1</bus>   | 0   | Data from IP                                   |      |

| IP2Bus_Error  | none                        | 0   | Error response                                 |      |

#### Table 2: IPIC I/O Signals

| Signal Name        | Range                       | I/O | Description                                                                    | Page |

|--------------------|-----------------------------|-----|--------------------------------------------------------------------------------|------|

| IP2Bus_Intr        | 0:C_IP_INTR_NUM-1           | 0   | Interrupt event signals from User Logic                                        |      |

| IP2Bus_PostedWrInh | none                        | 0   | Posted write inhibit from User Logic                                           |      |

| IP2Bus_Retry       | none                        | 0   | Retry response from User Logic                                                 |      |

| IP2Bus_ToutSup     | none                        | 0   | Timeout suppress from User Logic                                               |      |

| Bus2IP_MstError    | none                        | Ι   | Master Error from IPIF                                                         |      |

| Bus2IP_MstLastAck  | none                        | Ι   | Master Last Acknowledge from IPIF                                              |      |

| Bus2IP_MstAck      | none                        | Ι   | Master Acknowledge from IPIF                                                   |      |

| Bus2IP_MstRetry    | none                        | Ι   | Master Retry from IPIF                                                         |      |

| Bus2IP_MstTimeOut  | none                        | Ι   | Master Timeout from IPIF                                                       |      |

| IP2Bus_Addr        | 0:C_ <bus>_AWIDTH-1</bus>   | 0   | <bus> address for the master transaction</bus>                                 |      |

| IP2Bus_Clk         | none                        | 0   | Possible future signal to allow for dual-<br>clock-domain (asynchronous) FIFOs |      |

| IP2Bus_MstBE       | 0:C_ <bus>_DWIDTH/8-1</bus> | 0   | Byte-enables qualifiers from User Logic                                        |      |

| IP2Bus_MstBurst    | none                        | 0   | Burst qualifier from User Logic                                                |      |

| IP2Bus_MstBusLock  | none                        | 0   | Bus-lock qualifier from User Logic                                             |      |

| IP2Bus_MstNum      | 0:3                         | 0   | Burst size indicator from User Logic                                           |      |

| IP2Bus_MstReq      | none                        | 0   | Master request from User Logic                                                 |      |

| IP2Bus_MstRNW      | none                        | 0   | Read/Not Write from User Logic                                                 |      |

| IP2IP_Addr         | 0:C_ <bus>_AWIDTH-1</bus>   | 0   | Local device address for the master transaction                                |      |

#### Table 2: IPIC I/O Signals (Continued)

# Slave Interface Signal Descriptions

These signals listed below are primarily associated with the slave interface of the IPIC; however, some of the signals are shared with the master interface and IPIFs that contain a master (such as DMA) may make use of the slave signals to complete local transactions. These transactions are described in the chapters on the user templates that provide master services in the IPIF.

#### Bus2IP\_Addr

This is the address bus from the IPIF to the user logic. This bus is the same width as the host bus address bus. The Bus2IP\_Addr bus can be used for additional address decoding or as input to addressable memory devices.

#### Bus2IP\_BE

The Bus2IP\_BE is a bus of Byte Enable qualifiers from the IPIF to the user logic. A bit in the Bus2IP\_BE set to '1' indicates that the associated byte lane contains valid data. For example, if Bus2IP\_BE = 0011, this indicates that byte lanes 2 and 3 contain valid data.

#### Bus2IP\_Burst

The Bus2IP\_Burst signal from the IPIF to the user logic indicates that the current transaction is a burst transaction.

#### Bus2IP\_Clk

This is the clock input to the user logic. All IPIC signals are synchronous to this clock. It is identical to the <bus>\_Clk signal that is an input to the user core. In an OPB core,

www.xilinx.com

1-800-255-7778

Bus2IP\_Clk is the same as OPB\_Clk, and in a PLB core, it is the same as PLB\_Clk. No additional buffering is provided on the clock; it is passed through as is.

#### Bus2IP\_CE

Bus2IP\_CE is a bus of "chip" enables from the IPIF to the user core. In the general case, there can be an arbitrary number of CE signals for each Bus2IP\_CS signal, but the number of CE signals is fixed in some of the user core templates. The assertion of a bit in Bus2IP\_CE indicates that a point address associated with the CE has been decoded. For example, the Bus2IP\_CS signal indicates a decode of a block of addresses, and the Bus2IP\_CE signal indicates a decode of a particular register or address within the block of addresses.

#### Bus2IP\_CS

Bus2IP\_CS is a bus of "chip" select signals from the IPIF to the user core. It indicates a decode within a block of addresses defined by a base address and a high address. In the simplest templates, there is only one Bus2IP\_CS signal.

#### Bus2IP\_Data

This is the data bus from the IPIF to the user logic; it is used for both master and slave transactions. It is the same width as the host bus data bus.

#### Bus2IP\_Freeze

The Bus2IP\_Freeze signal is an input to the user logic that indicates a freeze has been requested. A freeze is typically used in a debugging situation in which the core should gracefully stop it's internal operations but remain active on the bus. An example is a watchdog timer which should be stopped when a software breakpoint is reached so that spurious system resets are not generated. It is up to the user core to define the action caused by the Bus2IP\_Freeze input.

#### Bus2IP\_RdCE

The Bus2IP\_RdCE bus is an input to the user logic. It is Bus2IP\_CE qualified by a read transaction.

#### Bus2IP\_Reset

Signal to reset the User Logic; asserts whenever the <bus>\_Rst signal does and, if the Reset block is included, whenever there is a software-programmed reset.

#### Bus2IP\_RNW

Bus2IP\_RNW is an input to the user logic that indicates the transaction type (read or write). Bus2IP\_RNW = 1 indicates a read transaction and Bus2IP\_RNW = 0 indicates a write transaction. It is valid whenever at least one Bus2IP\_CS is active.

#### Bus2IP\_WrCE

The Bus2IP\_WrCE bus is an input to the user logic. It is Bus2IP\_CE qualified by a write transaction.

#### IP2Bus\_Ack

IP2Bus\_Ack is the read/write acknowledgement from the user logic to the IPIF. For writes, it indicates the data has been taken by the user logic. For reads, it indicates that valid data is available. For immediate acknowledgement (such as for a register read/write), this signal can be tied to '1'. Wait states can be inserted in the transaction by delaying the assertion of IP2Bus\_Ack. If the IP2Bus\_Ack will be delayed more than 8 clocks, then the IP2Bus\_ToutSup (timeout suppress) signal must also be asserted to prevent a timeout on the host bus.

#### IP2Bus\_Data

This is the data bus from the user logic to the IPIF; it is used for both master and slave transactions. It is the same width as the host bus data bus.

#### IP2Bus\_Error

This signal from the user logic to the IPIF indicates an error has occurred during the current transaction. It is valid when IP2Bus\_Ack is asserted.

#### IP2Bus\_Intr

The IP2Bus\_Intr bus is an output from the user logic to the IPIF that consists of interrupt event signals to be detected and latched inside the IPIF.

#### IP2Bus\_PostedWrInh

This signal from the user logic to the IPIF indicates that posted writes should be inhibited. Normally burst write operations are treated as posted writes to improve performance, but assertion of the IP2Bus\_PostedWrInh signal indicates that all writes should be treated as single-beat write transactions.

#### IP2Bus\_Retry

IP2Bus\_Retry is a response from the user logic to the IPIF that indicates the currently requested transaction cannot be completed at this time and that the requesting master should retry the operation. If the IP2Bus\_Retry signal will be delayed more than 8 clocks, then the IP2Bus\_ToutSup (timeout suppress) signal must also be asserted to prevent a timeout on the host bus.

#### IP2Bus\_ToutSup

The IP2Bus\_ToutSup must be asserted by the user logic whenever its acknowledgement or retry response will take longer than 8 clock cycles.

### Master Interface Signal Descriptions

These signals listed below are primarily associated with the master interface of the IPIC; however, some of the master signals are shared with the slave interface and IPIFs that contain a master (such as DMA) may make use if the slave signals to complete local transactions. These transactions are described in the chapters on the user templates that provide master services in the IPIF.

#### Bus2IP\_MstError

The Bus2IP\_MstError signal from the IPIF to the user logic indicates whether the transfer has an error. The signal is valid during the cycle that Bus2IP\_MstLastAck is active. Note: a burst transaction reporting an error may have terminated prematurely.

#### Bus2IP\_MstLastAck

Bus2IP\_MstLastAck is a one-cycle acknowledgement of a master transaction from the IPIF to the user logic. A transaction may consist of multiple transfers (burst transaction); Bus2IP\_MstLastAck will always accompany the last Bus2IP\_MstAck for the transaction.

#### Bus2IP\_MstAck

Bus2IP\_MstAck is a one-cycle acknowledgement of a master transfer from the IPIF to the user logic. For writes it indicates that the IPIF has accepted the current data and is ready for the next data; for reads it indicates that valid data is present on the Bus2IP\_Data bus.

### Bus2IP\_MstRetry

Bus2IP\_MstRetry is a one-cycle alternative completion signal to Bus2IP\_MstLastAck. It indicates that the requested transaction could not be performed but may succeed if retried; if IP2Bus\_MstReq remains asserted in the following cycle, the IPIF will retry the transaction and may reuse any state that it has built up in support of the transaction (the user logic must leave addresses and transaction qualification signals unchanged). If otherwise the request signal is deasserted on the following cycle and the transaction is considered abandoned from the point of view of the IPIF.

#### Bus2IP\_MstTimeOut

Bus2IP\_MstTimeOut (from the IPIF to the user logic) is a one-cycle alternative completion signal to Bus2IP\_MstLastAck. It indicates that the requested transaction could not be performed within the timeout interval associated with the host bus.

#### IP2Bus\_Addr

IP2Bus\_Addr is an output from the user logic to the IPIF. It is the address bus for the current master transaction. It is valid when IP2Bus\_Req is active.

#### IP2Bus\_Clk

Possible future signal from the user logic to the IPIF to allow for dual-clock-domain (asynchronous) FIFOs. Not currently used.

#### IP2Bus\_MstBE

IP2Bus\_MstBE is a bus of Byte Enables qualifiers from the user logic to the IPIF for a master transaction. A bit in the IP2Bus\_MstBE set to '1' indicates that the associated byte lane contains valid data. For example, if IP2Bus\_MstBE = 0011, this indicates that byte lanes 2 and 3 contain valid data.

#### IP2Bus\_MstBurst

The IP2Bus\_MstBurst qualifier from the user logic to the IPIC indicates the master transaction is a burst operation.

#### IP2Bus\_MstBusLock

The IP2Bus\_MstBusLock qualifier from the user logic to the IPIC indicates the master is requesting that the host bus be locked until IP2Bus\_MstBusLock is deasserted. The assertion of IP2Bus\_MstBusLock must accompany a master request, and can be deasserted at any time.

#### IP2Bus\_MstNum

The IP2Bus\_MstNum bus indicates the burst length for burst transfers. The number of transfers for the burst is IP2Bus\_MstNum+1, so that a value of 0000 indicates a burst length of one, and a value of 1111 indicates a burst length of 16. Bursts may be from 1 to 16 words, halfwords, or bytes.

#### IP2Bus\_MstReq

This signal from the user logic to the IPIF indicates that the user logic is requesting a master transaction. This request signal must remain asserted until acknowledged by Bus2IP\_MstLastAck, Bus2IP\_Retry, or Bus2IP\_TimeOut.

#### IP2Bus\_MstRNW

$IP2Bus_MstRNW$  is an input to the IPIF from the user logic that indicates the transaction type (read or write).  $IP2Bus_MstRNW = 1$  indicates a read transaction and

$IP2Bus\_MstRNW = 0 \ indicates \ a \ write \ transaction. \ It \ is \ valid \ when \ IP2Bus\_MstReq \ is \ active.$

#### IP2IP\_Addr

The IP2IP\_Addr signal is an output from the user logic that indicates the local device address for the master transaction. This address will be the source for a master write transaction and the sink for a master read transaction. This is used only in bus peripherals that are both master and slave and the master requires access to the slave devices to perform master operations. An example is a master that must read from a local memory and then write that data to the host bus. In this case IP2IP\_Addr is used to address the local memory that provides the data for the write.

# **Example IPIC transactions**

The timing diagrams shown below are intended to illustrate example IPIC transactions to clarify the timing relationships between signals. These timing diagrams do not completely define the behaviour of all signals and are intended to supplement the textual descriptions given above.

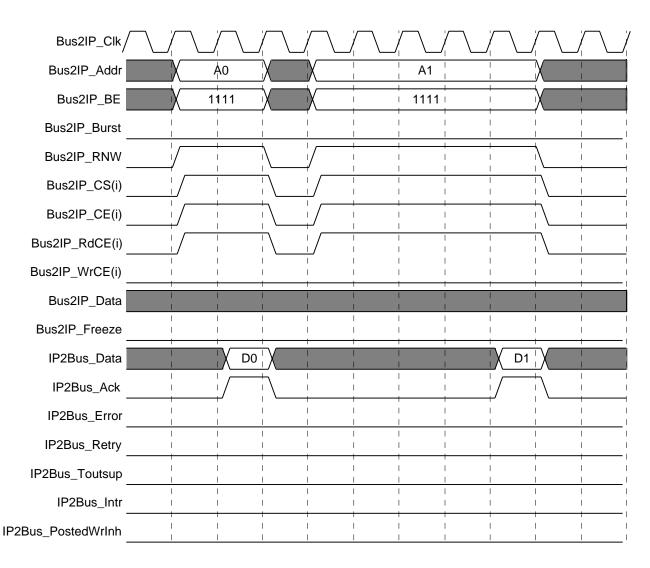

## Slave Read – Single Beat

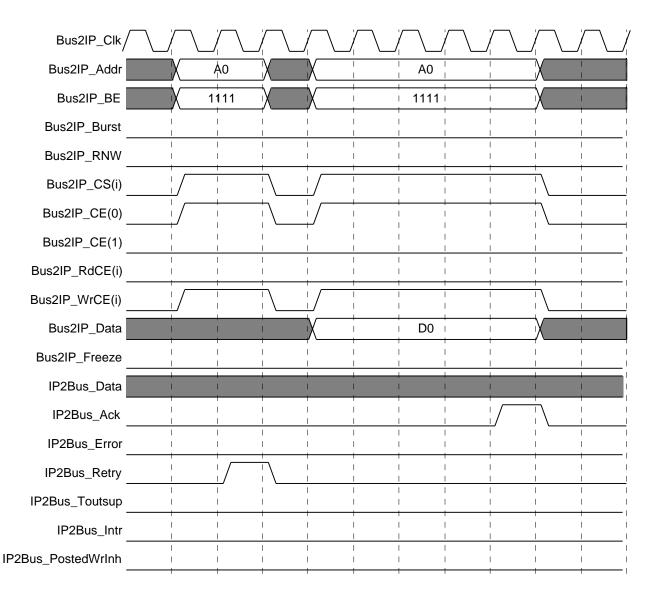

The timing diagram shows two typical IPIC read transactions, each started with the assertion of Bus2IP\_CS and terminated with assertion of the single-cyle IP2Bus\_Ack signal.

Figure 1-3: Slave Read – Single Beat

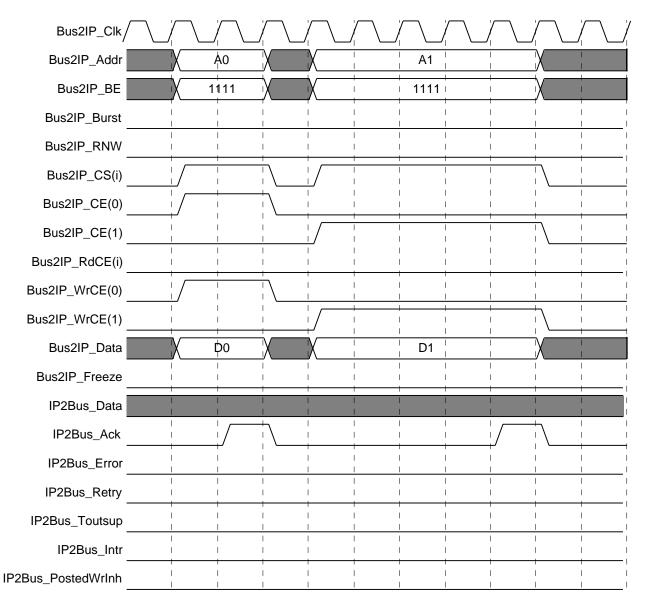

#### Slave Write – Single Beat

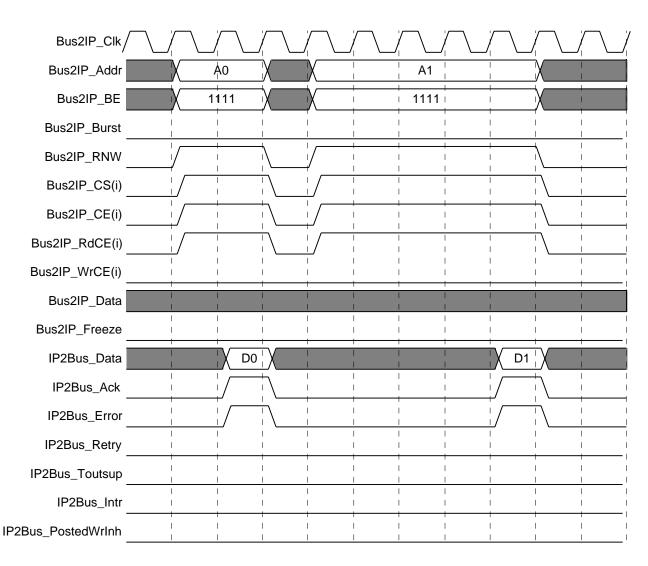

This example shows two typical single-beat write transactions, each starting with assertion of Bus2IP\_CS and ending with assertion of the the single-cycle IP2Bus\_Ack signal. Note that two Bus2IP\_CE signals are shown, indicating A0 and A1 are in the same Bus2IP\_CS space but are accessing different chip enables (Bus2IP\_CE). This could represent writing to two sequential registers within the same device. The empty cycle between the two transactions is not required but is typical due to pipelining of the acknowledge signal to the host bus.

Figure 1-4: Slave Write – Single Beat

#### Slave Read – Single Beat Back to Back

Single-cycle, back to back reads are possible if supported by the host bus, the IP, and the pipelining within the IPIF is turned off (this is an advanced feature of the IPIF and is not currently accessible from the user core template; it will be available in future user core templates). The operation of the interface is the same: one data and acknowledge for each assertion of Bus2IP\_CS.

| Bus2IP_Clk/        |           | //   |           |      |            | $\frown$     |  |      |           |

|--------------------|-----------|------|-----------|------|------------|--------------|--|------|-----------|

| Bus2IP_Addr        |           | X A1 | A2        | A3   | A4         |              |  |      |           |

| Bus2IP_BE          | X 1111    | 1100 | 1111      | 0001 | 1111       | X            |  |      |           |

| Bus2IP_Burst       | <br>      |      | <br>      |      |            |              |  |      |           |

| Bus2IP_RNW         |           |      | <br> <br> |      | i<br>      | \            |  |      |           |

| Bus2IP_CS(i)       |           |      |           |      |            |              |  |      |           |

| Bus2IP_CE(i)       |           |      |           |      |            | $\mathbb{Z}$ |  |      | <br> <br> |

| Bus2IP_RdCE(i)     |           |      | <br> <br> |      |            | $\mathbb{Z}$ |  |      |           |

| Bus2IP_WrCE(i)     | <br> <br> |      | <br> <br> |      | <br> <br>  |              |  |      | <br>      |

| Bus2IP_Data        |           |      |           |      |            |              |  |      |           |

| Bus2IP_Freeze      | <br> <br> |      |           |      |            |              |  |      | <br> <br> |

| IP2Bus_Data        |           |      | D2        | D3   | <b>D</b> 4 | X            |  |      |           |

| IP2Bus_Ack         |           |      |           |      |            | $\mathbb{Z}$ |  |      |           |

| IP2Bus_Error       |           |      | <br>      |      |            |              |  |      | <br>      |

| IP2Bus_Retry       | <br> <br> |      | <br> <br> |      | <br> <br>  |              |  |      | <br>      |

| IP2Bus_Toutsup     | <br>      |      | <br>      |      | <br>       |              |  |      |           |

| IP2Bus_Intr        |           |      | <br> <br> |      | <br> <br>  |              |  |      | <br> <br> |

| IP2Bus_PostedWrInh | <br>      |      |           |      | <br>       |              |  | <br> |           |

Figure 1-5: Slave Read – Single Beat Back to Back

#### Slave Write – Single Beat Back to Back

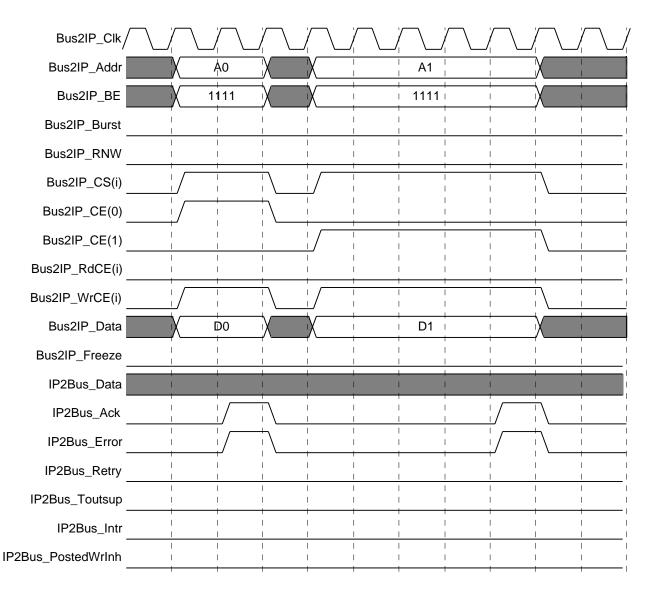

Single-cycle, back to back writes are possible if supported by the host bus, the IP, and the pipelining within the IPIF is turned off (this is an advanced feature of the IPIF and is not currently accessible from the user core template; it will be available in future user core templates). The operation of the interface is the same: one data and acknowledge for each assertion of Bus2IP\_CS.

| Bus2IP_Clk/        |      |           |      |      |            |      |      |           |      |           |

|--------------------|------|-----------|------|------|------------|------|------|-----------|------|-----------|

| Bus2IP_Addr        | A0   | X A1      | X A2 | X A3 | X A4       | Х    |      |           |      |           |

| Bus2IP_BE          | 1111 | 1100      | 1111 | 0001 | 1111       | X    |      |           |      |           |

| Bus2IP_Burst       |      |           |      |      |            |      | <br> | <br>      | <br> |           |

| Bus2IP_RNW         |      |           |      |      |            |      |      | <br> <br> |      | <br> <br> |

| Bus2IP_CS(i)       |      |           |      |      |            | ī\   |      |           |      |           |

| Bus2IP_CE(i)       |      |           | <br> |      |            |      |      | <br>      |      | <br>      |

| Bus2IP_RdCE(i)     |      | 1         |      |      |            | 1    | 1    |           |      | <br>      |

| Bus2IP_WrCE(i)     |      | <br> <br> | <br> |      |            |      |      | <br> <br> |      | <br>      |

| Bus2IP_Data        | D0   | χ D1      | D2   | X D3 | <b>D</b> 4 | X    |      |           |      | I         |

| Bus2IP_Freeze      |      |           |      |      |            |      |      | <br> <br> |      | <br> <br> |

| IP2Bus_Data        |      |           |      |      |            |      |      |           |      |           |

| IP2Bus_Ack         |      | <br> <br> | <br> |      |            |      |      | <br> <br> |      |           |

| IP2Bus_Error       |      |           | <br> |      |            |      |      |           | <br> |           |

| IP2Bus_Retry       |      |           |      |      |            |      |      | <br>      |      | <br> <br> |

| IP2Bus_Toutsup     |      |           |      |      |            |      |      |           |      | <br>      |

| IP2Bus_Intr        |      |           |      |      |            |      |      | <br> <br> |      | <br> <br> |

| IP2Bus_PostedWrInh |      | <br>      |      |      |            | <br> | <br> | <br>      | <br> |           |

Figure 1-6: Slave Write – Single Beat Back to Back

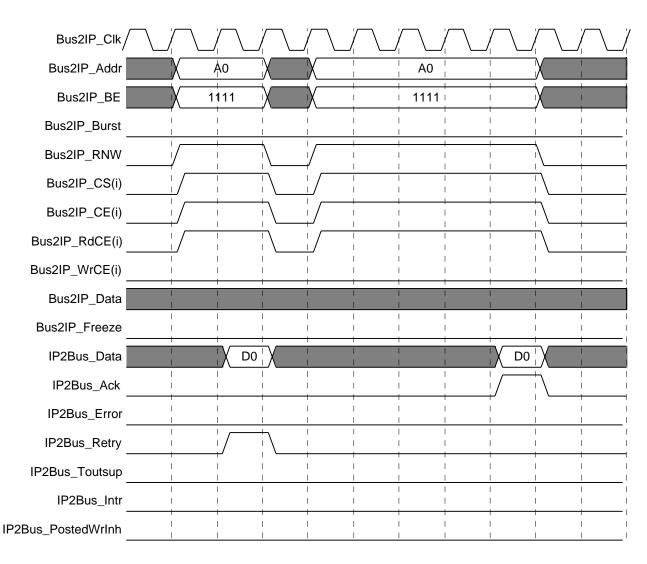

## Slave Read – Single Beat with Retry

Retry is an alternate transaction completion that may be used in place of IP2Bus\_Ack. Assertion of IP2Bus\_Retry indicates to the bus master that the transaction could not be completed but will succeed at some time in the future if retried. Retry transactions are identical to normally completed transactions except no data is returned and IP2Bus\_Retry is asserted in place of IP2Bus\_Ack.

Figure 1-7: Slave Read – Single Beat with Retry

### Slave Write – Single Beat with Retry

Retry is an alternate transaction completion that may be used in place of IP2Bus\_Ack. Assertion of IP2Bus\_Retry indicates to the bus master that the transaction could not be completed but will succeed at some time in the future if retried. Retry transactions are identical to normally completed transactions except no data is written and IP2Bus\_Retry is asserted in place of IP2Bus\_Ack.

Figure 1-8: Slave Write – Single Beat with Retry

### **Slave Read – Single Beat with Timeout Suppress**

IP2Bus\_Toutsup must be asserted if the assertion of IP2Bus\_Ack will be delayed by more than 8 clocks from Bus2IP\_CS. If more than 8 clocks elapse from assertion of Bus2IP\_CS without assertion of either IP2Bus\_Ack or IP2Bus\_Toutsup, a timeout error may occur on the host bus.

| Bus2IP_Clk/        |      | /         | /         |                  |            |      |           |    |           |

|--------------------|------|-----------|-----------|------------------|------------|------|-----------|----|-----------|

| Bus2IP_Addr        | X    |           |           |                  | A0         |      |           |    | X         |

| Bus2IP_BE          | X    |           | <br> <br> | <br>             | 1111       |      |           |    |           |

| Bus2IP_Burst       |      | <br>      | <br>      |                  | <br>       |      |           |    | <br> <br> |

| Bus2IP_RNW         |      |           | <br> <br> |                  |            |      |           |    |           |

| Bus2IP_CS(i)       |      |           |           |                  | <br> <br>  |      |           |    |           |

| Bus2IP_CE(i)       |      |           | <br> <br> |                  |            |      |           |    |           |

| Bus2IP_RdCE(i)     |      |           |           |                  |            |      |           |    |           |

| Bus2IP_WrCE(i)     |      |           | <br> <br> |                  | 1          |      |           |    | <br> <br> |

| Bus2IP_Data        |      |           |           |                  |            |      |           |    |           |

| Bus2IP_Freeze      |      |           | <br> <br> |                  |            |      |           |    |           |

| IP2Bus_Data        | 1    |           |           |                  |            |      |           | D0 | X         |

| IP2Bus_Ack         |      | 1         | <br> <br> |                  |            |      |           |    |           |

| IP2Bus_Error       | <br> | <br>      | <br>      | <br>             |            |      |           |    | <br>      |

| IP2Bus_Retry       |      | <br>      | <br> <br> |                  |            |      |           |    | <br> <br> |

| IP2Bus_Toutsup     | <br> |           | <br>      | . '<br>   <br>   | <br> <br>  | <br> | <br> <br> |    |           |

| IP2Bus_Intr        | 1    | <br> <br> | <br> <br> | <br>             | <br> <br>  |      |           |    | <br> <br> |

| IP2Bus_PostedWrInh | <br> | <br>      | <br>      | . '<br>     <br> | ,<br> <br> |      | <br>      |    |           |

Figure 1-9: Slave Read – Single Beat with Timeout Suppress

# Slave Write – Single Beat with Timeout Suppress

IP2Bus\_Toutsup must be asserted if the assertion of IP2Bus\_Ack will be delayed by more than 8 clocks from Bus2IP\_CS. If more than 8 clocks elapse from assertion of Bus2IP\_CS without assertion of either IP2Bus\_Ack or IP2Bus\_Toutsup, a timeout error may occur on the host bus.

| Bus2IP_Clk/        |      |              |            |      |  |            |      |           |

|--------------------|------|--------------|------------|------|--|------------|------|-----------|

| Bus2IP_Addr        | X    | <br>         |            | A0   |  |            |      |           |

| Bus2IP_BE          | X    |              |            | 1111 |  |            |      |           |

| Bus2IP_Burst       |      |              | '<br> <br> |      |  | '<br> <br> |      |           |

| Bus2IP_RNW         |      |              |            |      |  | <br>       |      |           |

| Bus2IP_CS(i)       |      | <br>   <br>  | <br> <br>  |      |  | <br> <br>  |      |           |

| Bus2IP_CE(i)       |      | + + +<br>1 1 |            |      |  | <br> <br>  | <br> |           |

| Bus2IP_RdCE(i)     |      |              | י<br> <br> |      |  | <br> <br>  |      |           |

| Bus2IP_WrCE(i)     |      | + + +<br>1 1 |            | <br> |  | <br> <br>  | <br> |           |

| Bus2IP_Data        |      |              |            | D0   |  |            |      |           |

| Bus2IP_Freeze      |      |              |            |      |  | <br> <br>  |      |           |

| IP2Bus_Data        |      |              |            |      |  |            |      |           |

| IP2Bus_Ack         |      |              | <br> <br>  |      |  | <br>       |      |           |

| IP2Bus_Error       |      |              | <br>       |      |  | <br>       | <br> |           |

| IP2Bus_Retry       |      |              | <br> <br>  |      |  | <br>       |      | <br> <br> |

| IP2Bus_Toutsup     |      |              | <br> <br>  |      |  | <br>       |      |           |

| IP2Bus_Intr        |      |              | <br> <br>  |      |  | <br> <br>  | <br> | <br> <br> |

| IP2Bus_PostedWrInh | <br> |              | <br>       |      |  | <br>       |      |           |

Figure 1-10: Slave Write – Single Beat with Timeout Suppress

# Slave Read – Single Beat with Error

The IP2Bus\_Error signal is a qualifier for IP2Bus\_Ack (not an alternate completion) and indicates that an error occurred during the transaction.

Figure 1-11: Slave Read – Single Beat with Error

# Slave Write – Single Beat with Error

The IP2Bus\_Error signal is a qualifier for IP2Bus\_Ack (not an alternate completion) and indicates that an error occurred during the transaction.

Figure 1-12: Slave Write – Single Beat with Error

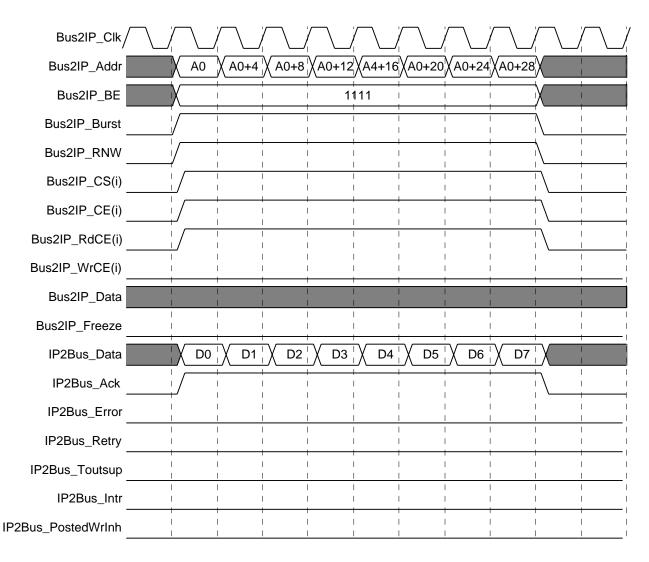

#### Slave Read – Burst Operation

In burst operation, assertion of Bus2IP\_Burst indicates that a burst is in progress and the addresses follow sequential order. Bus2IP\_BE must be consistent throughout the burst and indicate sequential accesses. For example, a burst of words must have a constant Bus2IP\_BE of 1111, while a burst of bytes must sequence as 1000, 0100, 0010, 0001, 1000, etc. Slaves may throttle the burst by negating IP2Bus\_Ack during the burst, but the host bus master is not allowed to throttle the burst. A burst may be any length and is terminated by deassertion of the Bus2IP\_Burst signal.

Figure 1-13: Slave Read – Burst Operation

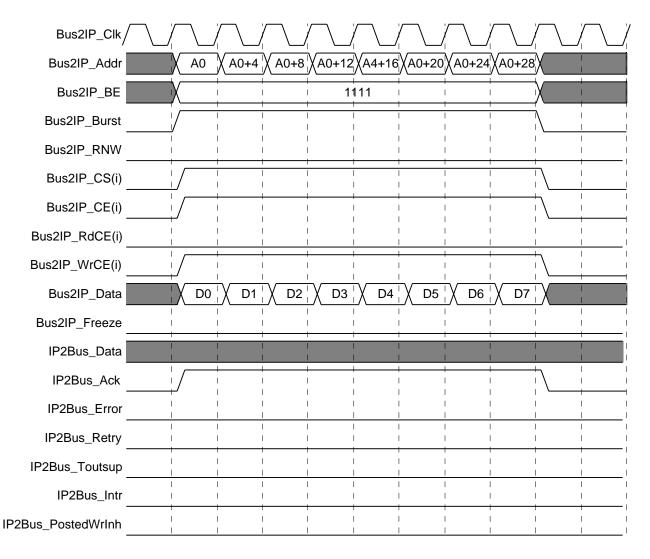

#### **Slave Write – Burst Operation**

In burst operation, assertion of Bus2IP\_Burst indicates that a burst is in progress and the addresses follow sequential order. Bus2IP\_BE must be consistent throughout the burst and indicate sequential accesses. For example, a burst of words must have a constant Bus2IP\_BE of 1111, while a burst of bytes must sequence as 1000, 0100, 0010, 0001, 1000, etc. Slaves may throttle the burst by negating IP2Bus\_Ack during the burst, but the host bus master is not allowed to throttle the burst. A burst may be any length and is terminated by deassertion of the Bus2IP\_Burst signal.

Figure 1-14: Slave Write – Burst Operations

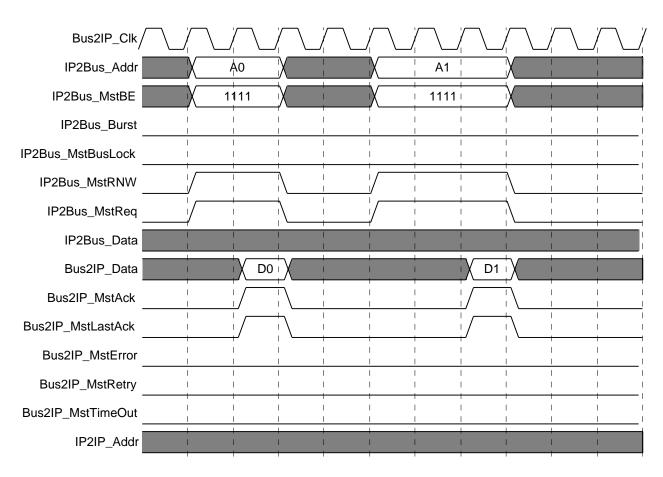

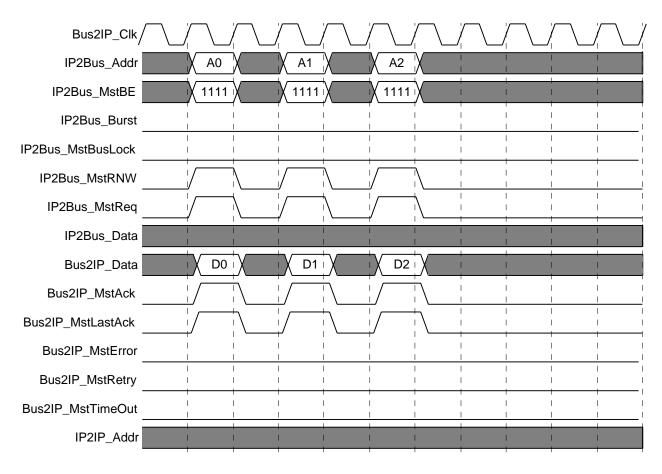

## Master Read – Single Beat

A single-beat master read is initiated with assertion of IP2Bus\_MstReq and terminated with assertion of Bus2IP\_MstAck and Bus2IP\_MstLastAck. Bus2IP\_MstLastAck is used to indicate the last acknowledge of a transfer and hence must be asserted concurrently with Bus2IP\_MstAck for single-beat transfers; it is asserted only on the last data transfer of a burst transfer.

Figure 1-15: Master Read – Single Beat

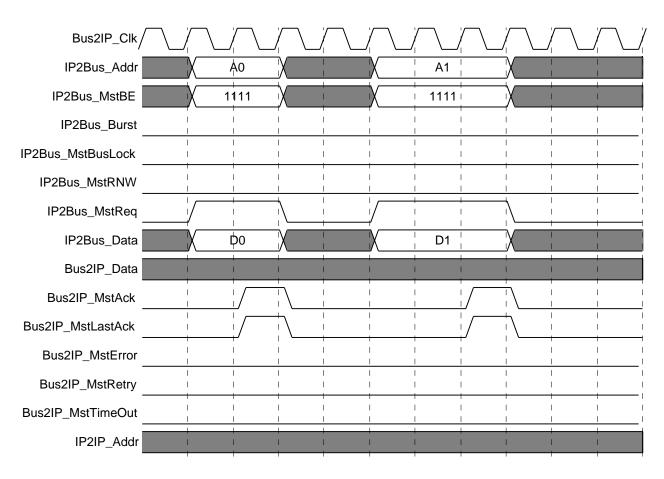

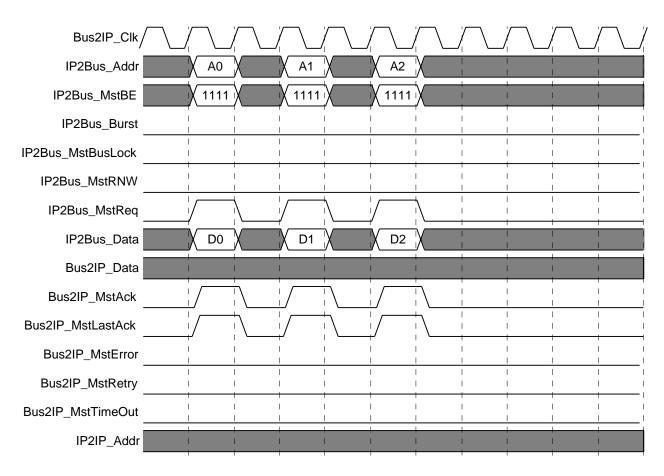

### Master Write - Single Beat

A single-beat master write is initiated with assertion of IP2Bus\_MstReq and terminated with assertion of Bus2IP\_MstAck and Bus2IP\_MstLastAck. Bus2IP\_MstLastAck is used to indicate the last acknowledge of a transfer and hence must be asserted concurrently with Bus2IP\_MstAck for single-beat transfers; it is asserted only on the last data transfer of a burst transfer.

#### Master Read – Single Beat Back to Back

This example illustrates single-cycle completion of single-beat master read transactions. The unused cycle between transfers is not required but is typical due to pipeline delays in the master logic.

Figure 1-17: Master Read – Single Beat Back to Back

## Master Write – Single Beat Back to Back

This example illustrates single-cycle completion of single-beat master write transactions. The unused cycle between transfers is not required but is typical due to pipeline delays in the master logic.

Figure 1-18: Master Write – Single Beat Back to Back

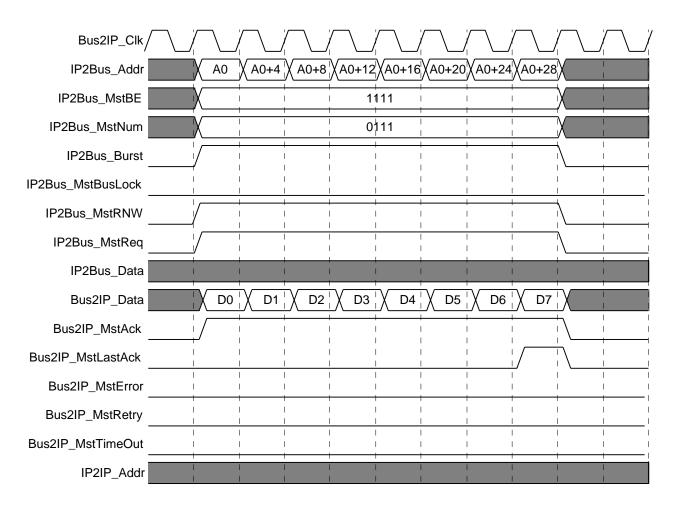

#### **Master Read – Burst Operation**

During master burst operation, the master must provide sequential addresses on IP2Bus\_Addr, with the address increment determined by the transaction size. For example, the address must increment by 4 for fullword bursts, 2 for halfword bursts and 1 for byte bursts. The IP2Bus\_MstBE must be consistent with the address presented on IP2Bus\_Addr. A burst is indicated by the assertion of IP2Bus\_Burst, and the length of the burst is defined by the IP2Bus\_MstNum bus. The burst length is IP2Bus\_MstNum+1. Each transfer is terminated with assertion of Bus2IP\_MstAck, and the last transfer of the burst must be terminated by Bus2IP\_MstLstAck.

Figure 1-19: Master Read – Burst Operation

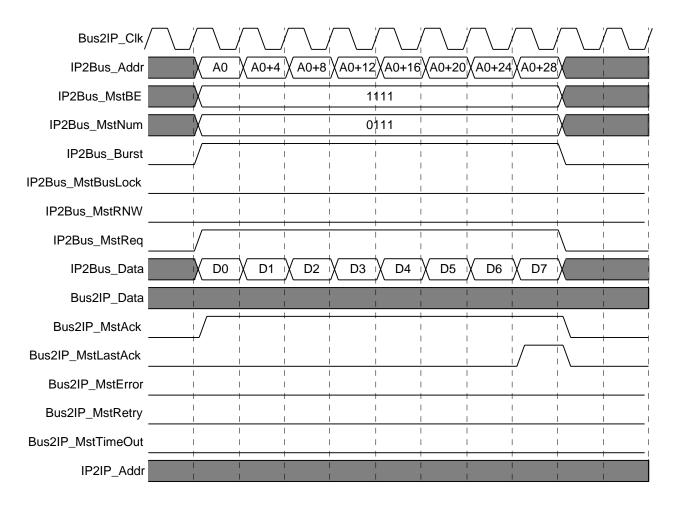

#### Master Write – Burst Operation

During master burst operation, the master must provide sequential addresses on IP2Bus\_Addr, with the address increment determined by the transaction size. For example, the address must increment by 4 for fullword bursts, 2 for halfword bursts and 1 for byte bursts. The IP2Bus\_MstBE must be consistent with the address presented on IP2Bus\_Addr. A burst is indicated by the assertion of IP2Bus\_Burst, and the length of the burst is defined by the IP2Bus\_MstNum bus. The burst length is IP2Bus\_MstNum+1. Each transfer is terminated with assertion of Bus2IP\_MstAck, and the last transfer of the burst must be terminated by Bus2IP\_MstLstAck.

Figure 1-20: Master Write – Burst Operation

# **Revision History**

The following table shows the revision history for this document.

|    | Date    | Version | Revision                              |

|----|---------|---------|---------------------------------------|

| 11 | 1/15/02 | 1.0     | Initial Xilinx version for EDK3.1 SP2 |

| 4  | 4/1/03  | 1.1     | Added IPIC timing diagrams            |

# User Core Template for OPB (Slave Services Package 0)

DS458 (v1.1) Jan. 17, 2003

**Product Specification**

## Summary

This document provides the specification for a VHDL template that can be used to create a simple OPB slave. The design template also includes an MPD file template and a PAO file template that can be modified as needed for the user core. The set of features and services provided in this template is called the Slave Services Package 0 (SSP0). It can be used to simplify creation of user cores that require only an OPB slave attachment.

| opb_core_ssp0 | v1.00b |

|---------------|--------|

|---------------|--------|

# Introduction

The SSP0 OPB user core template consists of the following files:

- A VHDL file, opb\_core\_ssp0.vhd, that provides the core's entity and architectural sections, instantiates an IP Interface (IPIF) for connection to the host bus, and provides an example instantiation of user logic.

- An MPD (Microprocessor Peripheral Definition) file that provides all of the required MPD contents except for the additional ports required by the user logic.

- A PAO (Peripheral Analyze Order) file that provides all of the required PAO entries except for the files required by the user logic.

- An example user logic design which consists of a quad LED brightness control based on four OPB-controlled Pulse Width Modulation (PWM) blocks.

The services provided by the SSP0 OPB user core template are:

- Slave-only attachment to the OPB bus.

- Support for burst transfers.

- Support for delayed bus acknowledge controlled by user logic.

- Module Identification Register (MIR) for software identification of the user core.

- Reset Register for generating a core reset via software.

- Address decode for one address range (any size) and one MIR/Reset register.

- Connection to user logic with a simplified set of IPIC (IP Interconnect) signals.

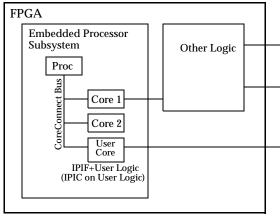

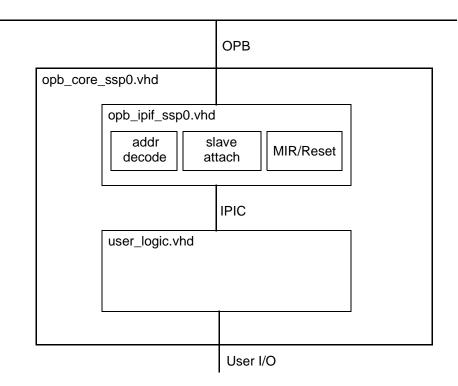

# **Block Diagram**

The block diagram of the SSP0 user core template is shown below in Figure 1. The VHDL template supplies two components: a component for the user logic and a component for an IPIF (IP Interface). The IPIF used in the template is a simplified IPIF that uses only the services and ports required by the capabilities provided with the template. The opb\_core\_ssp0.vhd file uses a similarly named IPIF called opb\_ipif\_ssp0.vhd. It is important to understand that the IPIF used in the SSP0 user core template is not a full IPIF but only provides the parts of the full IPIF

© 2002 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice. NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this fea-

ture, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and so the posterior and the source of the implementation. Source of the implementation is claims of infringement and any implicit warranties of merchantability or fitness for a particular purpose.

required for a simple slave. This simplifies the use of the IPIF, reduces the complexity of interfacing to it, and insures that FPGA resources are used efficiently.

Figure 1: SSP0 User Core Template Block Diagram

**Base Address** The SSP0 user core template provides two regions of memory that must be specified. The C BASEADDR/C HIGHADDR pair specifies the address range for the user logic portion of the **Specification** design. The other address range that appears in the template, C\_MIR\_BASEADDR/ C MIR HIGHADDR, specifies the address range for the Software Reset Register and Module Identification Register (MIR) within the IPIF. The C MIR BASEADDR and C MIR HIGHADDR must be set to a valid address range because the Software Reset Register is always present in the IPIF. The MIR may or may not be included, depending on the value of the C\_MIR\_INCLUDE generic. Even if a MIR is not included, the Software Reset Register uses the C MIR BASEADDR and C MIR HIGHADDR generics. These generics are typically set to define a small address range, such as 256 bytes. The address range size must be a power of 2.

# Using the Template

The basic steps for using the OPB core template are as follows. A detailed example follows this listing.

- Create a directory under the "myip" directory in your project directory with the name and version of the user core (example: opb\_mycore\_v1\_00\_a).

- Create a user logic design that uses the IPIC signal set described below.

- Rename the opb\_core\_ssp0.vhd template file to the same name as the user core (example: rename opb\_core\_ssp0.vhd to opb\_mycore.vhd)

- In the renamed template file, edit the entity name and library statements as required for the user core. In the template file, lines that may require editing are marked with a --USER-- comment.

- Remove the example user logic component declaration and instantiation and replace them with the user logic component declaration and instantiation.

- Add the ports required by the user logic to the entity declaration.

- In the "data" directory, change the name of the .mpd and .pao files to be the same as the user core name (example: rename opb\_core\_ssp0\_v2\_0\_0.mpd to opb\_mycore\_v2\_0\_0.mpd and rename opb\_core\_ssp0\_v2\_0\_0.pao to opb\_mycore\_v2\_0\_0.pao). Note that the \_v2\_0\_0 suffix is required to identify the PSF format version. Use the same version suffix as the supplied template.

- In the renamed MPD file, edit the core name and add any user ports. Lines that may require editing are identified by the # --USER-- comment.

- In the renamed PAO file, add the source files required by the user core. The library name for the user core is the user core name plus the version suffix. Lines that may require editing are identified by the # --USER-- comment.

# **IPIC Signal Set**

The following IPIC signals are used in the SSP0 OPB user core template. These signals are required to be present as ports on the user logic or they must be handled appropriately in the opb\_core\_ssp0 template. All signals are active high. See the chapter "Adding User Cores to Your Embedded System" for more details on the IPIC signals.

```

: std_logic_vector(0 to C_OPB_AWIDTH-1);

signal Bus2IP_Addr

signal Bus2IP_BE

: std_logic_vector(0 to C_OPB_DWIDTH/8-1);

signal Bus2IP_Burst

: std_logic;

signal Bus2IP_Clk

: std_logic;

signal Bus2IP_CS

: std_logic;

signal Bus2IP_Data : std_logic_vector(0 to C_OPB_DWIDTH-1);

signal Bus2IP_RdCE : std_logic;

signal Bus2IP_Reset : std_logic;

signal Bus2IP_RNW : std_logic;

signal Bus2IP_WrCE : std_logic;

signal IP2Bus_Ack : std_logic;

signal IP2Bus_Clk : std_logic;

signal IP2Bus_Data : std_logic;

signal IP2Bus_Error : std_logic;

signal IP2Bus_Error : std_logic;

signal Bus2IP_Data

: std_logic_vector(0 to C_OPB_DWIDTH-1);

signal IP2Bus_PostedWrInh : std_logic;

signal IP2Bus_Retry : std_logic;

signal IP2Bus_ToutSup : std_logic;

```

# **Example: Creating an OPB User Core**

This example goes through the entire process of creating an OPB user core from the template. The example creates a core called "opb\_mycore" and uses it in an MHS file. This example assumes you have a project directory called "system\_example" in which your MHS, MSS, and other system files are placed, and that your EDK install directory is C:/EDK. This example also assumes that you have your user logic in a directory called C:/user\_logic and that the user logic consists of two files, mycore\_user\_logic.vhd and my\_subblock.vhd.

**Step 1.** In the system\_example directory, create a directory called myip if it doesn't already exist:

\$ mkdir myip

**Step 2.** Copy the OPB user core template from the install area to the myip directory that you just created (this assumes you are creating version v1.00a of your user core; change the destination name as required for a different user core version):

```

$ cp -r c:/EDK/hw/user_core_templates/opb_core_ssp0_v1_00_b

myip/opb_mycore_v1_00_a

```

**Step 3.** Go into the myip/opb\_mycore\_v1\_00\_a/data directory and rename the .mpd and .pao files to opb\_mycore:

- \$ cd myip/opb\_mycore\_v1\_00\_a/data

- \$ mv opb\_core\_ssp0\_v2\_0\_0.mpd opb\_mycore\_v2\_0\_0.mpd

- \$ mv opb\_core\_ssp0\_v2\_0\_0.pao opb\_mycore\_v2\_0\_0.pao

**Step 4.** Go into the VHDL source directory and rename the opb\_core\_ssp0.vhd file to opb\_mycore.vhd:

```

$ cd ../hdl/vhdl

```

\$ mv opb\_core\_ssp0.vhd opb\_mycore.vhd

Step 5. Copy your user logic files into the VHDL directory where opb\_mycore.vhd resides.

\$ cp c:/user\_logic/\*.vhd .

**Step 6.** Edit the opb\_mycore.vhd file, modifying the comment line at the top, library name if needed, entity declaration, and architecture statement. These lines are all marked by the --USER-- comment. What you are accomplishing in this step is to replace all occurrences of opb\_core\_ssp0 with opb\_mycore. When you are finished, the beginning of the file should look like this:

```

-- $Id: opb_mycore.vhd,v 1.1 2002/11/08 22:56:56 tise Exp $

--USER-- Add comment with name of this source file

-- opb_mycore.vhd

library ieee;

use ieee.std_logic_1164.all;

library opb_ipif_ssp0_v1_00_a;

use opb_ipif_ssp0_v1_00_a.all;

-- Add user library if this source file uses

-- entities from the user library

library opb_mycore_v1_00_a; --USER-- library name

use opb_mycore_v1_00_a.all; --USER-- use statement

-- entity

_____

entity OPB_Mycore is --USER-- change entity name

generic

(

C_BASEADDR : std_logic_vector(0 to 31) := X"FFFFFFFF;;

C_HIGHADDR

: std_logic_vector(0 to 31) := X"00000000";

C_MIR_BASEADDR : std_logic_vector(0 to 31) := X"FFFFFFFF;

C_MIR_HIGHADDR : std_logic_vector(0 to 31) := X"00000000";

C_USER_ID_CODE

: integer

:= 3;

C_INCLUDE_MIR

: integer

:= 0;

C_OPB_AWIDTH

C_OPB_DWIDTH

: integer

:= 32;

: integer

:= 32;

: string := "virtex2" -- not used

C_FAMILY

);

port

(

--Required OPB bus ports, do not add to or delete

OPB_ABus : in std_logic_vector(0 to C_OPB_AWIDTH-1);

OPB BE

: in std_logic_vector(0 to C_OPB_DWIDTH/8-1);

OPB Clk

: in std logic;

OPB DBus

: in std_logic_vector(0 to C_OPB_DWIDTH-1);

: in std_logic;

OPB_RNW

: in std_logic;

OPB_Rst

OPB_select : in std_logic;

OPB_seqAddr : in std_logic;

Sln DBus

: out std_logic_vector(0 to C_OPB_DWIDTH-1);

Sln_errAck : out std_logic;

```

```

Sln_retry : out std_logic;

Sln_toutSup : out std_logic;

Sln_xferAck : out std_logic;

--USER-- add user I/Os to port list

LED : out std_logic_vector(0 to 3)

);

end entity OPB_Mycore; --USER-- change entity name

-- architecture

architecture imp of OPB_Mycore is --USER-- change entity name

```

#### Step 7. Edit the entity ports to include the user I/Os:

```

entity OPB_Mycore is --USER-- change entity name

generic

(

C_BASEADDR

: std_logic_vector(0 to 31) := X"FFFFFFFF;

C_HIGHADDR: std_logic_vector(0 to 31) := X"00000000";C_MIR_BASEADDR: std_logic_vector(0 to 31) := X"FFFFFFF;

C_MIR_HIGHADDR : std_logic_vector(0 to 31) := X"00000000";

: integer

C_USER_ID_CODE

:= 3;

C_INCLUDE_MIR

: integer

:= 0;

C_OPB_AWIDTH

:= 32;

: integer

: integer

C_OPB_DWIDTH

:= 32;

: string := "virtex2" -- not used

C_FAMILY

);

port

(

--Required OPB bus ports, do not add to or delete

OPB_ABus : in std_logic_vector(0 to C_OPB_AWIDTH-1);

: in std_logic_vector(0 to C_OPB_DWIDTH/8-1);

OPB_BE

OPB_Clk

: in std_logic;

: in std_logic_vector(0 to C_OPB_DWIDTH-1);

OPB_DBus

OPB_RNW

: in std_logic;

: in std_logic;

OPB_Rst

OPB_select : in std_logic;

OPB_seqAddr : in std_logic;

Sln_DBus : out std_logic_vector(0 to C_OPB_DWIDTH-1);

Sln_errAck : out std_logic;

Sln_retry : out std_logic;

Sln_toutSup : out std_logic;

Sln_xferAck : out std_logic;

--USER-- add user I/Os to port list

-- LED

: out std_logic_vector(0 to 3);

MyInPort

: in std_logic_vector(0 to 3);

MyOutPort

: out std_logic_vector(0 to 3)

);

end entity OPB_Mycore; --USER-- change entity name

```

Step 8. Edit the user logic component declaration and instantiation:

# -- architecture

```

architecture imp of OPB_Mycore is --USER-- change entity name

--USER-- component declaration for user core logic. Change the

--component declaration below to the declaration of the user's

--logic.

component mycore_user_logic is

port

(

Bus2IP_Addr : in std_logic_vector(0 to 31);

Bus2IP_Clk : in std_logic;

Bus2IP_CS

: in std_logic;

Bus2IP_Data : in std_logic_vector(0 to 31);

Bus2IP_RdCE : in std_logic;

Bus2IP_Reset : in std_logic;

Bus2IP_WrCE : in std_logic;

IP2Bus_Data : out std_logic_vector(0 to 31);

MyInPort : in std_logic_vector(0 to 3);

MyOutPort : out std_logic_vector(0 to 3)

);

end component mycore_user_logic;

--OPB IPIF lite declaration -- do not change

component opb_ipif_ssp0 is

generic

(

C_BASEADDR : std_logic_vector(0 to 31) := X"FFFFFFFF;;

C_HIGHADDR : std_logic_vector(0 to 31) := X"00000000";

C_MIR_BASEADDR : std_logic_vector(0 to 31) := X"FFFFFFFF;

C_MIR_HIGHADDR : std_logic_vector(0 to 31) := X"00000000";

C_USER_ID_CODE : INTEGER

:= 1;

C_INCLUDE_MIR : INTEGER

:= 0;

C_OPB_AWIDTH : INTEGER

:= 32;

C_OPB_DWIDTH : INTEGER

:= 32;

C_FAMILY

: string

:= "virtex2"

);

port

(

OPB_ABus: in std_logic_vector(0 to C_OPB_AWIDTH-1);OPB_BE: in std_logic_vector(0 to C_OPB_DWIDTH/8-1OPB_Clk: in std_logic;OPB_DBus: in std_logic_vector(0 to C_OPB_DWIDTH-1);OPB_DBUS: in std_logic_vector(0 to C_OPB_DWIDTH-1);

: in std_logic_vector(0 to C_OPB_DWIDTH/8-1);

OPB_RNW: in std_logic;OPB_Rst: in std_logic;OPB_select: in std_logic;OPB_seqAddr: in std_logic;

Sln_DBus: out std_logic_vector(0 to C_OPB_DWIDTH-1);Sln_errAck: out std_logic;Sln_retry: out std_logic;

Sln_toutSup : out std_logic;

Sln_xferAck : out std_logic;

Bus2IP_Addr : out std_logic_vector(0 to C_OPB_AWIDTH-1);

: out std_logic_vector(0 to C_OPB_DWIDTH/8-1);

Bus2IP BE

Bus2IP_Burst : out std_logic;

Bus2IP_Clk : out std_logic;

Bus2IP_CS : out std_logic;

Bus2IP_Data : out std_logic_vector(0 to C_OPB_DWIDTH-1);

Bus2IP_RdCE : out std_logic;

Bus2IP_Reset : out std_logic;

Bus2IP_RNW

: out std_logic;

Bus2IP_WrCE : out std_logic;

```

```

IP2Bus_Ack

: in std_logic;

IP2Bus_Clk

: in std_logic;

IP2Bus_Data : in std_logic_vector(0 to C_OPB_DWIDTH-1);

IP2Bus_Error : in std_logic;

IP2Bus_PostedWrInh : in std_logic;

IP2Bus_Retry : in std_logic;

IP2Bus_ToutSup

: in std_logic

);

end component opb_ipif_ssp0;

--IP Interconnect (IPIC) signal list --do not delete

signal Bus2IP_Addr : std_logic_vector(0 to C_OPB_AWIDTH-1);

signal Bus2IP_BE

: std_logic_vector(0 to C_OPB_DWIDTH/8-1);

signal Bus2IP_Burst : std_logic;

signal Bus2IP_Clk : std_logic;

signal Bus2IP_CS : std_logic;

signal Bus2IP_Data : std_logic_vector(0 to C_OPB_DWIDTH-1);

signal Bus2IP_RdCE : std_logic;

signal Bus2IP_Reset : std_logic;

signal Bus2IP_RNW : std_logic;

signal Bus2IP_WrCE : std_logic;

signal IP2Bus_Ack : std_logic;

signal IP2Bus_Clk : std_logic;

signal IP2Bus_Data : std_logic_vector(0 to C_OPB_DWIDTH-1);

signal IP2Bus_Error : std_logic;

signal IP2Bus_PostedWrInh : std_logic;

signal IP2Bus_Retry : std_logic;

signal IP2Bus_ToutSup

: std_logic;

begin

_____

--OPB IPIF lite instantiation -- do not delete

OPB_IPIF_SSP0_I : opb_ipif_ssp0

generic map

(

C_BASEADDR

=> C_BASEADDR,

C_HIGHADDR

=> C_HIGHADDR,

C_MIR_BASEADDR => C_MIR_BASEADDR,

C_MIR_HIGHADDR => C_MIR_HIGHADDR,

C_MIR_MIGHEDER=> C_MIR_MIGHEDER,C_USER_ID_CODE=> C_USER_ID_CODE,C_INCLUDE_MIR=> C_INCLUDE_MIR,C_OPB_AWIDTH=> C_OPB_AWIDTH,C_OPB_DWIDTH=> C_OPB_DWIDTH,

C_OPB_DWIDTH

C_FAMILY

=> C_FAMILY

)

port map

(

=> OPB_ABus,

OPB_ABus

OPB BE

=> OPB_BE,

OPB_Clk

=> OPB_Clk,

OPB DBus

=> OPB DBus,

=> OPB_RNW,

OPB_RNW

=> OPB_Rst,

OPB_Rst

OPB_select

=> OPB_select,

OPB_seqAddr

=> OPB_seqAddr,

Sln_DBus

=> Sln_DBus,

Sln_errAck

=> Sln_errAck,

Sln_retry

=> Sln_retry,

Sln_toutSup

=> Sln_toutSup,

```

=> Sln\_xferAck,

Sln\_xferAck

```

Bus2IP_Addr

=> Bus2IP_Addr,

=> Bus2IP_BE,

=> Bus2IP_Burst,

Bus2IP_BE

Bus2IP_Burst

Bus2IP_Clk

=> Bus2IP_Clk,

Bus2IP_CS

=> Bus2IP_CS,

Bus2IP_Data

=> Bus2IP_Data,

Bus2IP RdCE

=> Bus2IP RdCE,

Bus2IP_Reset

=> Bus2IP_Reset,

=> Bus2IP_RNW,

Bus2IP_RNW

Bus2IP_WrCE

=> Bus2IP_WrCE,

IP2Bus_Ack

=> IP2Bus_Ack,

IP2Bus_Clk

=> IP2Bus_Clk,

IP2Bus_Data => IP2Bus_Data,

IP2Bus_Error => IP2Bus_Error,

IP2Bus_PostedWrInh => IP2Bus_PostedWrInh,

IP2Bus_Retry => IP2Bus_Retry,

IP2Bus_ToutSup => IP2Bus_ToutSup

);

--USER-- change the USER_LOGIC_I instantiation below to the

--instantiation of the user logic.

MYUSER_LOGIC_I : mycore_user_logic

port map

(

Bus2IP_Addr => Bus2IP_Addr,

Bus2IP_Clk => Bus2IP_Clk,

Bus2IP_CS => Bus2IP_CS,

Bus2IP_Data => Bus2IP_Data,

Bus2IP_Reset => Bus2IP_Reset,

Bus2IP_RdCE => Bus2IP_RdCE,

Bus2IP_WrCE => Bus2IP_WrCE,

IP2Bus_Data => IP2Bus_Data,

MyInPort

=> MyInPort,

MyOutPort => MyOutPort

);

end architecture imp;

--USER-- The following signals must be driven by the user_logic or by the

following assignments.

IP2Bus Ack

<= '1'; -- no wait states, immediate Ack. Drive

-- from user_logic to add wait states

<= '0'; -- no retry

IP2Bus_Retry

IP2Bus_Error

<= '0'; -- no error

IP2Bus_ToutSup

<= '0'; -- no timeout suppress. If IP2Bus_Ack is

-- delayed more than 15 clocks, drive

-- IP2Bus_ToutSup to '1' to avoid

-- arbiter timeout on OPB.

IP2Bus_PostedWrInh <= '0'; -- do not inhibit posted write

```

**Step 9.** The next step is to edit the .mpd and .pao template files. In the .mpd file you just need to change the IP name and add the user logic ports. In the .pao file, you need to add the files you have added to the user core that will be compiled when the platform generation tools are run. You can again search for --USER-- to find the lines that may require editing. Remember that the .pao file defines the Peripheral Analyze Order, so the files must be put in the correct order for VHDL compilation (subdesigns first followed by the top level file).

```

##

## Microprocessor Peripheral Definition

##

BEGIN opb_mycore, IPTYPE = PERIPHERAL, EDIF=TRUE # --USER-- change core name

BUS_INTERFACE BUS = SOPB, BUS_STD = OPB, BUS_TYPE = SLAVE

## Generics for VHDL or Parameters for Verilog

PARAMETER c_baseaddr= 0xFFFFFFF, DT = std_logic_vector, MIN_SIZE = 0xFFPARAMETER c_highaddr= 0x00000000, DT = std_logic_vector

PARAMETER c_mir_baseaddr = 0xFFFFFFF, DT = std_logic_vector, MIN_SIZE = 0xFF

PARAMETER c_mir_highaddr = 0x00000000, DT = std_logic_vector

PARAMETER c_user_id_code = 3, DT = integer

PARAMETER c_include_mir = 0,

DT = integer

PARAMETER c_opb_awidth= 32,DT = integerPARAMETER c_opb_dwidth= 32,DT = integer

PARAMETER c_family = virtex2, DT = string

# --USER-- Add user core parameters

## Ports

PORT opb_abus = OPB_ABus, DIR = IN, VEC = [0:(c_opb_awidth-1)],

BUS = SOPB

PORT opb_be = OPB_BE, DIR = IN, VEC = [0:((c_opb_dwidth/8)-1)], BUS = SOPB

PORT opb_clk = "", DIR = IN, BUS = SOPB

BUS = SOPB

PORT opb_dbus = OPB_DBus, DIR = IN, VEC = [0:(c_opb_dwidth-1)],

PORT opb_rnw = OPB_RNW, DIR = IN,

BUS = SOPB

PORT opb_rst

= OPB_Rst,

DIR = IN,

BUS = SOPB

PORT opb_select = OPB_select, DIR = IN,

PORT opb_select = IN,

BUS = SOPB

PORT opb_seqaddr = OPB_seqAddr, DIR = IN,

BUS = SOPB

PORT sln_dbus = Sl_DBus, DIR = OUT, VEC = [0:(c_opb_dwidth-1)],

BUS = SOPB

PORT sln_errack = Sl_errAck, DIR = OUT,

BUS = SOPB

PORT sln_retry = Sl_retry, DIR = OUT,

BUS = SOPB

PORT sln_toutsup = Sl_toutSup, DIR = OUT,

BUS = SOPB

PORT sln_xferack = Sl_xferAck, DIR = OUT,

BUS = SOPB

# --USER-- change to user core ports

= "", DIR = IN, VEC = [0:3]

PORT MyInPort

= "", DIR = OUT, VEC = [0:3]

PORT MyOutPort

END

_____

#

# opb_core_ssp0 pao file

#

lib proc_common_v1_00_b proc_common_pkg

lib proc_common_v1_00_b pselect

lib proc_common_v1_00_b

or_muxcy

ipif_pkg

lib ipif_common_v1_00_a

ipif_steer

lib ipif_common_v1_00_a

lib opb_bus_attach_v1_00_a reset_mir

lib opb_bus_attach_v1_00_a opb_bus_attach

lib opb_ipif_ssp0_v1_00_a opb_ipif_ssp0

# --USER-- add all user core source files and change the following source to

#

your top level core name and library

lib opb_mycore_v1_00_a my_subblock

lib opb_mycore_v1_00_a mycore_user_logic

lib opb_mycore_v1_00_a opb_mycore

```

**Step 10.** The final step is to get your core into the system's MHS file. This can be done by editing the MHS file with a text editor or by using the Project  $\rightarrow$  Add/Edit Cores... (dialog) menu selection or the Project  $\rightarrow$  Add Core... (text) menu selection.

The following table shows the revision history for this document.

| Date     | Version | Revision                                  |

|----------|---------|-------------------------------------------|

| 11/19/02 | 1.0     | Initial Xilinx release.                   |

| 1/17/03  | 1.1     | Added base address specification section. |

|          |         |                                           |

# User Core Template for OPB (Master Services Package 0)

DS459 (v1.1) Jan. 17, 2003

**Product Specification**

# **Summary** This document provides the specification for a VHDL template that can be used to create a simple OPB master. The design template also includes an MPD file template and a PAO file template that can be modified as needed for the user core. The set of features and services provided in this template is called the Master Services Package 0 (MSP0). It can be used to simplify creation of user cores that require only an OPB master attachment.

| opb_core_msp0 | v1.00b |

|---------------|--------|

|---------------|--------|

# Introduction

The MSP0 OPB user core template consists of the following files:

- A VHDL file, opb\_core\_msp0.vhd, that provides the core's entity and architectural sections, instantiates an IP Interface (IPIF) for connection to the host bus, and provides an example instantiation of user logic.

- An MPD (Microprocessor Peripheral Definition) file that provides all of the required MPD contents except for the additional ports required by the user logic.

- A PAO (Peripheral Analyze Order) file that provides all of the required PAO entries except for the files required by the user logic.

- An example user logic design which consists of a simple peripheral that fills memory with an incrementing data pattern.

The services provided by the MSP0 OPB user core template are:

- Master-only attachment to the OPB bus.

- Support for single-beat transfers (no burst support).

- Support for delayed data acknowledge controlled by the host bus.

- Connection to user logic with a simplified set of IPIC (IP Interconnect) signals.

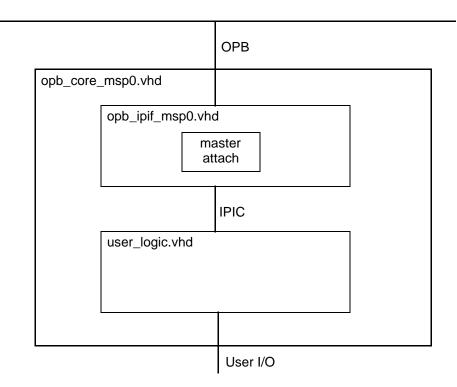

# **Block Diagram**

The block diagram of the MSP0 user core template is shown below in Figure 1. The VHDL template supplies two components: a component for the user logic and a component for an IPIF (IP Interface). The IPIF used in the template is a simplified IPIF that uses only the services and ports required by the capabilities provided with the template. The opb\_core\_msp0.vhd file uses a similarly named IPIF called opb\_ipif\_msp0.vhd. It is important to understand that the IPIF used in the MSP0 user core template is not a full IPIF but only provides the parts of the full

© 2002 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice. NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature application or standard Xilinx makes on representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you