# Pitch Detection

Embedded System Design Final Report

Due May 10, 2005

Stephen A. Edwards

- -

Embedded Systems Design, 2005

- -

Koohee Lee (kl2188@columbia.edu)

Guy Sivan (gs2131@columbia.edu)

Gary Lo (gcl2104@columbia.edu)

## Table of Contents

## 1. Project Overview

## 2. Project Design

- Prototype

- Finalized Algorithm

## 3. Design Components

- Hardware Design

- Software Design

## 4. Calculations

## 5. Work Distribution

- Koohee Lee

- Guy Sivan

- Gary Lo

## 6. Future Advice and Lessons Learned

- 7. VHDL Code

- 8.C Code

#### 1. Project Overview

Our final product was targeted towards users that were in the early stages of learning a new and foreign language. In many foreign languages, especially some of the South East Asian ones, the accuracy of a speaker's pronunciation is highly dependant upon their ability to create the correct pitch and tone. To this end, it was our desire to create a system that would allow a user to visualize their own voice patterns and make corrections based on their own observations.

Our design was to create a hardware/software combination that would allow a user to see a plot of pitch versus time in a real-time format.

For simplicity let us assume that a voice consists of a single sinusoid. To find the pitch or frequency at a certain point in time, one can just look closely (zoom into) a waveform and measure the distance between to successive peaks. This distance corresponds to the period o the voice, and so to find the frequency, we just need to take the reciprocal of this value. This is the fundamental concept of our algorithm.

In the real world, a voice consists of many sinusoids rather than just one pure sinusoid. These sinusoids are a result of the anatomy of the human vocal system and appear all over the frequency spectrum (at many different frequencies). We have a much more complicated signal that consists of the fundamental harmonic and many other harmonics. The fundamental harmonic is the main frequency and it is what we define as the "pitch" of the voice. Our project is to find exactly this, and to plot it in real-time to get a graphical view of how the pitch in someone's voice is changing.

## 2. Project Design

#### Prototype

We created an initial prototype that would execute in Matlab. The goal of the prototype was to determine the feasibility of our project, as well as prove that our algorithm actually worked as planned. The Matlab program was created based on an initial algorithm that we designed which has since been modified to increase performance.

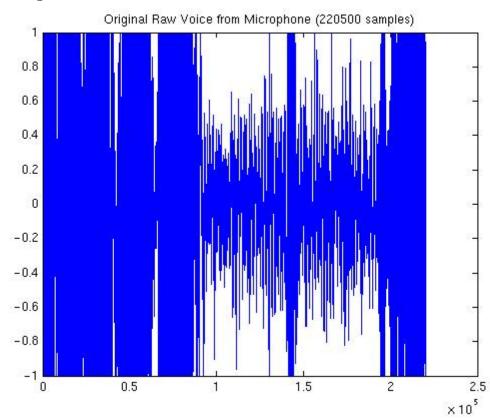

The input to our program was Koohee's voice, which was taken in through a microphone and stored. This data was processed and outputted the following graph.

Data Input:

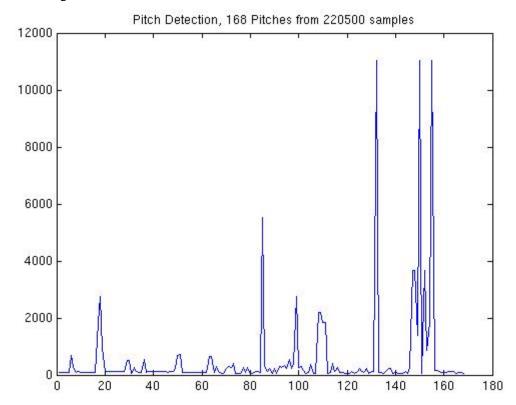

Data Output:

Based on the success of our prototype we were able to show that not only was our project feasible, but the algorithm worked.

#### Finalized Algorithm

The first step is to take in the sound wave. The A/D will take a signal from the microphone and output a 16bit digital signal at 11kHz, which will be shifted into a shift register the size of one block (330 samples). Every 330 samples, the contents of the shift register will be copied into a buffer. The contents in this buffer are what we run our algorithm on to determine a single value on the output of the pitch graph.

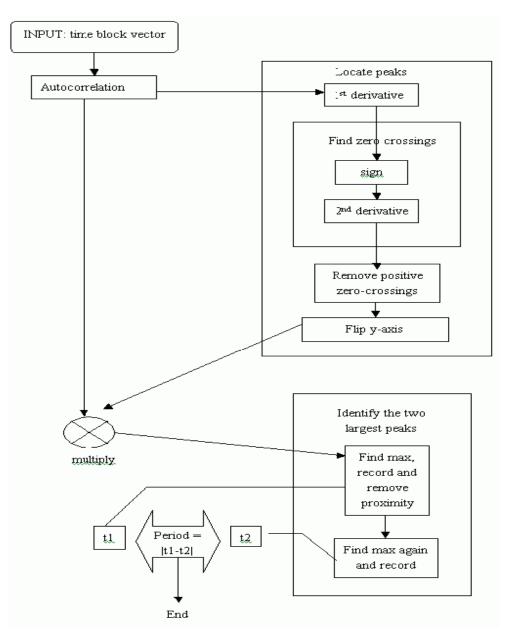

To run the algorithm, the first step is to perform a half-autocorrelation on the data set in the input buffer. The result of this autocorrelation will allow us to determine the distance between the two peaks in a time block because they will correspond to the two largest peaks in the autocorrelation. Performing this process one the data from the buffer will leave us with a new set of 330 points of data, the "half-autocorrelation graph". This data is then processed as follows to find the distance between the peaks.

- 1. Take the derivative of the data.

- 2. Perform the sign function on the data from step 1.

- 3. Take the derivative of data from *step 2* and multiply by -1.

- 4. Remove negative zero crossings.

- 5. Multiply results from *step 4* with data in halfautocorrelation graph one data point at a time and store in new buffer (or same buffer as *step 4* to save space.)

- 6. (May not be necessary:) Remove first few points from result in *step 5*.

- 7. Find the first peak and record its index in the buffer.

- 8. Use the index from step 7 and the block specifications

to find the distance between nearest peaks and

calculate value in time (period) and corresponding

frequency (pitch):

Period = T = (index / (samples per block)) \* (block

time),

Pitch = f = 1 / T

- 9. Output the pitch

Block Diagram of Algorithm.

## 3. Design Components

#### Hardware Design

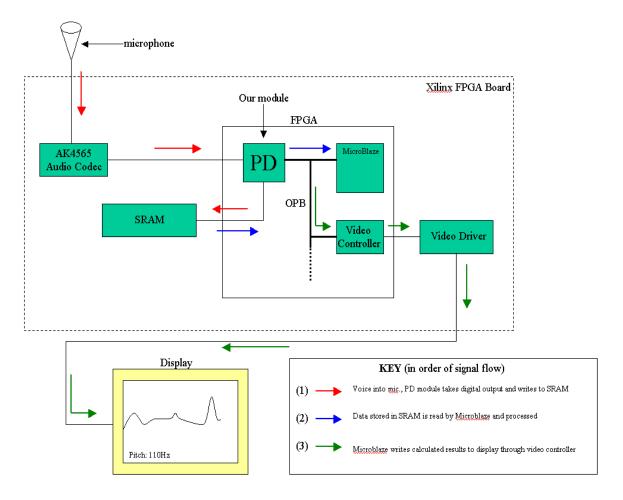

Our plan was to do three things inside hardware:

- 1. We wanted to take in voice data from a microphone and store it in the SRAM. This required using the audio codec to digitize the analog data from our voices.

- 2. Next we needed to extract data from the SRAM and pass it to the C program for processing.

- 3. Incorporate video controller from previous lab to get output onto the screen after processing inside C program.

What we were able to do:

1. We were able to create VHDL code that would allow us to write data into the SRAM from a microphone.

2. We were unable to determine how to get data stored inside the SRAM and send it to the Microblaze and our C program.

#### Software Design

We used C to process the data that was passed to the Microblaze from the SRAM. This process contained several steps:

- 1. Perform half-autocorrelation of data.

- 2. Take the first derivative.

- 3. Classify them into {-1, 0, 1} as the sign.

- 4. Find out zero-crossing.

- 5. Remove positive one's.

- 6. Flip the sign.

- 7. Multiply them by the data from step 1.

- 8. Find the maximum value and its location.

- 9. Return the pitch of the processing block. a. (Sampling frequency) / (STEP \* pitch location)

The C program proves to work like the Matlab program, but is currently implemented using floating point. It must be modified to work with the data stored in the SRAM (nonfloating point data). We need to reduce the input size of the data by dividing it by a constant to ensure that overflow of output data from half-autocorrelation does not occur.

## Calculations

We had to conduct several calculations to determine the feasibility of our project given our algorithm and the available hardware.

Given:

| 10.<br>11.<br>12.<br>13.                                           | Audio sampling device at 11kHz.<br>A/D converter with 16 bit output. |

|--------------------------------------------------------------------|----------------------------------------------------------------------|

| Clock Cycle Calculation (Half-Autocorrelation)                     |                                                                      |

| orig_n = 330<br>n = 165                                            |                                                                      |

| Total number of multiplications = n(2n-1):                         |                                                                      |

| $= 165*(330-1) \\= 54285$                                          |                                                                      |

| Total number of additions = $(n-1)(2n-1)$ :                        |                                                                      |

|                                                                    | 165-1)(330-1)<br>3956                                                |

| Clock cycles for addition: 1<br>Clock cycles for multiplication: 5 |                                                                      |

| Total clock cycles requires:                                       |                                                                      |

| = 1*(54285) + 5*(53956)<br>= 324056                                |                                                                      |

| Process running at 50Mhz, implies a time per clock cycles of:      |                                                                      |

| = 1<br>= 2                                                         | / 50Mhz<br>*10 <sup>-®</sup> seconds per cycle                       |

| Therefore, total time for half-autocorrelation:                    |                                                                      |

| $= 324065 * (2*10^{-8})$<br>= 6.4813 ms                            |                                                                      |

⇒ This number is well within our range of 30ms per time block.

#### Block Size Calculation

In order to calculate the pitch, we need at least two peaks to be within the block we are measuring the pitch of. Given that the block will not always perfectly align with the waveform, the only way we can ensure that at least two peaks are within the block is to set the block size to **three** wavelengths of the lowest possible frequency. As mentioned earlier we chose the lowest possible frequency to be 100Hz.

1/(100Hz) = 10ms, 3\*10ms = 30ms, At a sampling frequency of 11kHz: (11kHz)\*(30ms) = 330 samples,

⇒ Block Size = 30ms, 330 samples.

Note: The actual sampling rate of the codec was 44kHz, so we had to decimate the input to simulate 11kHz (1 out of every 4 samples).

### 5. Work Distribution

#### Koohee Lee

- Rewrote full algorithm in Matlab for prototyping, verification and fine-tuning.

- o Used Matlab to create samples and diagrams to prove that our algorithm worked.

- o In charge of creating the C code to implement DSP.

- o Worked together to write final project report.

#### Guy Sivan

- o Full system design.

- o In charge of VHDL programming.

- o Designed signal processing algorithm for pitch detection.

- o Reviewed details of DSP for timing and feasibility calculations.

- Researched and studied datasheets for necessary hardware components.

- o Worked together to write final project report.

#### Gary Lo

- Reviewed details of DSP for timing and feasibility calculations.

- Modified signal processing algorithm for increased efficiency; including the idea of the halfautocorrelation concept.

- Researched and studied datasheets for necessary hardware components.

- o Worked together to write final project report.

- o Involved in coding for both VHDL and C.

### 6. Future Advice and Lessons Learned

Every member of the group felt that if we had coordinated and managed our time more skillfully we would have been able to finish our project. Our inability to be disciplined about our meeting times caused two problems:

- 1. We were unable to meet with our advisor (Marcio) as often as we would have liked to discuss our project.

- 2. We were forced to create all of our VHDL code in a very hasty manner in order to try and generate some final result.

As it is now, we believe that with another week or two of work we could have the project fully completed.

Although we were unable to create a finished working product, we did do several things correctly. By rigorously testing and prototyping our algorithm in both Matlab and C were able to prove that our design would work. Also, the time spent modifying our algorithm meant that it was even more efficient than we had initially expected it to be.

In the future, we would recommend that if it is difficult to find a specific time where all members of the group are able to meet, start by using the class time as a meeting time because all group members will always be available during this time. We also recommend that people start early, create a detailed plan, and modularize the project so that individuals in the group could be responsible for their own part of the project.

### 7. VHDL

-- REAL-TIME PITCH DETECTION \_\_\_\_\_ library ieee; use ieee.std\_logic\_1164.all; use IEEE.STD\_LOGIC\_ARITH.all; use IEEE.STD\_LOGIC\_UNSIGNED.all; entity pd is generic ( C\_OPB\_AWIDTH : integer := 32;C OPB DWIDTH : integer := 32;C\_BASEADDR : std\_logic\_vector(0 to 31) := X"00000000"; C\_HIGHADDR : std\_logic\_vector(0 to 31) := X"FFFFFFFF" ); port ( OPB Clk : in std\_logic; : in std\_logic; OPB\_Rst OPB\_ABus : in std\_logic\_vector(0 to C\_OPB\_AWIDTH-1); --(31:0) : in std\_logic\_vector(0 to C\_OPB\_DWIDTH/8-1);--(3:0) OPB BE OPB\_DBus : in std\_logic\_vector(0 to C\_OPB\_DWIDTH-1); --(31:0) : in std\_logic; OPB RNW OPB select : in std logic; OPB\_seqAddr : in std\_logic; -- Sequential Address SIn DBus : out std\_logic\_vector(0 to C\_OPB\_DWIDTH-1); --(31:0) SIn\_errAck : out std\_logic; -- (unused) Sln\_retry : out std\_logic; -- (unused) -- Timeout suppress Sln\_toutSup : out std\_logic; Sln\_xferAck : out std\_logic; -- Transfer acknowledge SRAM CE : out std\_logic; --sram chip enable (active low) SRAM\_OE : out std\_logic; --sram output enable (active low) : out std\_logic; SRAM\_WE --sram write enable (active low) SRAM\_UB : out std\_logic; --sram enable upper-byte(active low) SRAM LB --sram enable lower-byte(active low) : out std\_logic; : out std\_logic\_vector(17 downto 0); --sram 18 bit address PB A : inout std\_ulogic\_vector(15 downto 0); --sram 16 bit data PB\_D

-- G: For audio codec -au\_mclk : out std\_logic; au\_lrclk : out std\_logic; au\_bclk : out std\_logic; au\_sdti : out std\_logic; au\_sdto0 : in std\_logic; : out std\_logic au\_cs ); end pd; \_\_\_\_\_ architecture Behavioral of pd is \_\_\_\_\_ -- SRAM \_\_\_\_\_ constant RAM\_AWIDTH : integer := 18; -- Number of address lines on the RAM constant RAM\_DWIDTH : integer := 16; -- Number of data lines on the RAM component OBUF\_F\_24 port ( O : out STD\_ULOGIC; -- the pin I : in STD\_ULOGIC); -- signal to pin end component; component IOBUF\_F\_24 port ( IO : inout STD\_ULOGIC; -- signal from pin I : in STD\_ULOGIC; -- the pin -- 1-drive IO with I T : in STD\_ULOGIC); end component; \_\_\_\_\_ -- Audio Controller \_\_\_\_\_ component wr\_audio\_control port ( clk\_in: in std\_logic; -->200ns clock

```

init: in std_logic;

--pulse input

done: out std_logic;

D_in: in std_logic_vector(15 downto 0);

--control data

cntrl_out: out std_logic);

end component;

_____

-- Codec

_____

component ak4565

port (

clk

: in std_logic;

: in std_logic;

rst

mclk

: out std_logic;

bclk

: out std_logic;

Irclk

: out std_logic;

sdti

: out std_logic;

sdto0 : in std_logic;

: out std_logic;

csn

cclk

: out std_logic;

cdti

: out std_logic;

adcdone : out std_logic; --AD indicator

dacload : out std_logic; --DA indicator

--G: UNUSED

adc_dtout : out std_logic_vector(15 downto 0); --data out to fpga

dac_dtin : in std_logic_vector(15 downto 0); --parallelload data from fpga

c_datain : in std_logic_vector(15 downto 0); --parallelload control from fpga

: in std_logic :='0'; --write to control

c_wr

c_done : out std_logic --write control done

);

end component;

-- SIGNALS

_____

signal mclk : std_logic; --12.5Mhz

signal bclk : std_logic; --3.125Mhz

signal Irclk: std_logic; --48.8Khz

signal cclk: std_logic;

signal sdti: std_logic;

```

```

signal latch16bit: std_logic_vector(15 downto 0) := x"0000";

signal adcdone : std_logic;

signal dacload : std_logic; --G: UNUSED

signal adc_dtout : std_logic_vector(15 downto 0); --data out to fpga

signal dac_dtin : std_logic_vector(15 downto 0) := x"0000"; --parallelload data

from fpga --G: UNUSED

signal c_datain : std_logic_vector(15 downto 0) :="1110000011100111"; --

parallelload control from fpga

signal csn : std_logic;

signal c_wr : std_logic;

signal c_done : std_logic;

signal trigger : std_logic;

_____

--SRAM

signal tri_state : std_logic; --tristate

signal ABus: std_logic_vector(17 downto 0); --Abus --always equal to

sram addr

signal pbDIn: std_logic_vector(15 downto 0);

--RAM_DI

--is equal to sram dt wr when

c_state=norm

--else is all zeroes

signal sram_rnw: std_logic;

--RNW

signal sram_addr: std_logic_vector(17 downto 0);

--Abus

signal sram_dt_rd: std_logic_vector(15 downto 0);

--RAM DO

signal sram_dt_wr: std_logic_vector(15 downto 0); --connects to pbDIn when

c_state=norm

-- G added:

signal chip_select : std_logic;

signal output_enable, write_enable : std_logic;

signal upperbyte_enable, lowerbyte_enable : std_logic;

signal RNW : std_logic;

signal RST : std_logic;

-- G added: some more stuff (for SRAM to be OPB readable (?))--

-- Critical: SIn_xferAck is generated directly from state bit 0!

```

```

constant STATE_BITS : integer :=3;

constant Idle : std logic vector(0 to STATE BITS-1) := "000";

constant Selected : std_logic_vector(0 to STATE_BITS-1) := "001";

constant Read : std_logic_vector(0 to STATE_BITS-1) := "011";

: std_logic_vector(0 to STATE_BITS-1) := "111";

constant Xfer

signal present state, next state : std logic vector(0 to STATE BITS-1);

_____

signal initcnt:std_logic_vector(15 downto 0):=X"0000"; --has to wait >

4128/fs=90ms for initialization

constant pre_init : std_logic_vector(1 downto 0):="00";

constant c_wr_wait: std_logic_vector(1 downto 0):="01";

constant wait_done: std_logic_vector(1 downto 0):="10";

constant norm : std_logic_vector(1 downto 0):="11";

signal c_state, n_state : std_logic_vector(1 downto 0):="00"; --used in both

FSMs

signal c_serial_data: std_logic;

--used for FSM that controls writing audio data to memorys

constant idling : std_logic_vector(1 downto 0):="00";

constant s1: std_logic_vector(1 downto 0):="01";

constant s2 : std_logic_vector(1 downto 0):="10";

signal s_done : std_logic; --when done writing to SRAM

_____

--G: added: (THESE SIGNALS WILL HELP COORDINATE WHO IS READING AND

WRITING, but they are not yet used fully)

signal audio_wr_addr: std_logic_vector(17 downto

0):="00000000000000000"; --the pointer to where the

--current audio sample

--should be written to in

SRAM

--used to disable the microblaze from

signal en_MB_read: std_logic;

--reading when the data from codec is

--being written to SRAM.

signal MB_read_addr: std_logic_vector(17 downto 0); --the current address

where the

--Microblaze reads from.

_____

```

begin

-----Audio Interface Signals and Buffering-----au\_mclk <= mclk; -----VERY IMPORTANT---- mclk must be sync with LRCLK au bclk  $\leq$  = bclk; au\_lrclk<= lrclk; au\_sdti <= sdti; au\_cs <=csn; -----SRAM pin assignment-----\_\_\_\_ SRAM\_CE <= '0' when chip\_select = '1' else '1'; -- '0' when c\_state=norm else1? SRAM\_WE <= '0' when write\_enable = '1' else '1'; SRAM\_OE <= '0' when output\_enable = '1' else '1'; --sram\_rnw? SRAM\_UB <= '0' when upperbyte\_enable = '1' else '1'; SRAM\_LB <= '0' when lowerbyte\_enable = '1' else '1'; gen1: for m in 0 to 17 generate sramAddrpin:OBUF\_F\_24 port map (  $O = > PB_A(m)$ , I = ABus(m); end generate; gen2: for m in 0 to 15 generate sramDatapin:IOBUF\_F\_24 port map (  $O = sram_dt_rd(m)$ ,  $IO = >PB_D(m)$ , I = pbDIn(m), T=>tri\_state); end generate; --G: we have to change this:----tri\_state <= sram\_rnw when c\_state=norm else '0'; -- always writing ABus < = sram addr(17 downto 0); pbDIn(15 downto 2) <= sram\_dt\_wr(15 downto 2) when c\_state=norm else (others = > '0');pbDIn(0)<=sram\_dt\_wr(0) when c\_state=norm else cclk; pbDIn(1)<=sram\_dt\_wr(1) when c\_state=norm else c\_serial\_data; \_\_\_\_\_

chip\_select <=

```

'1' when OPB_select = '1' and

OPB_ABus(0 to C_OPB_AWIDTH-2-RAM_AWIDTH) =

C_BASEADDR(0 to C_OPB_AWIDTH-2-RAM_AWIDTH) else

'0':

--The code below is from Lab6 and is for making the Microblaze be able to

--read from the SRAM. This way we can get the incoming audio data into the

C-

--code and do the signal processing in C. It seems that although C is much

--slower than doing it in hardware, there is enough speed to keep up real-

--time with much decimation (i.e. skipping output points). This just means a

--less smooth output.

-- Sequential part of the FSM

fsm_seq : process(OPB_Clk, OPB_Rst)

begin

if OPB Rst = '1' then

present_state <= Idle;</pre>

elsif OPB Clk'event and OPB Clk = '1' then

present_state <= next_state;

end if;

end process fsm_seq;

-- Combinational part of the FSM

fsm_comb : process(OPB_Rst, present_state, chip_select, OPB_Select, RNW)

begin

RST <= '1';

write_enable <= '0';

output_enable <= '0';

upperbyte_enable <= '1';

lowerbyte_enable <= '1';

tri_state <= '0';

-- used to be "tristate"

if OPB_RST = '1' then

next_state <= Idle;</pre>

else

case present_state is

when Idle = >

if chip_select = '1' then

next_state <= Selected;</pre>

else

next_state <= Idle;

```

```

end if;

when Selected =>

if OPB\_Select = '1' then

if RNW = '1' then

RST <= '0';

next_state <= Read;</pre>

else

write_enable <= '1';

tri_state <= '0';

next_state <= Xfer;</pre>

end if;

else

next_state <= Idle;

end if;

when Read =>

if OPB\_Select = '1' then

output_enable <= '1';

tri_state <= '1';

next_state <= Idle;</pre>

end if;

-- State encoding is critical here: xfer must only be true here

when Xfer =>

next_state <= Idle;

when others =>

next_state <= Idle;

end case;

end if;

end process fsm_comb;

SIn_xferAck <= present_state(0);</pre>

_____

-- Audio codec port map

_____

```

ak:ak4565 port map(clk =>OPB\_Clk,

```

rst

=>OPB_Rst

mclk

= >mclk,

bclk

= bclk,

|rc|k => |rc|k

=>sdti,

sdti

sdto0 =>au_sdto0,

=>csn,

csn

cclk

=>cclk,

cdti

=>c_serial_data,

adcdone = > adcdone,

dacload => dacload,

adc_dtout => adc_dtout,

dac dtin = > dac dtin,

c_datain =>c_datain,

C_Wr = > C_Wr

c_done =>c_done);

_____

-- PROCESSES

_____

---latch output data----- (from codec)

process (OPB_Clk,OPB_Rst)

begin

if OPB_Rst = '1' then

latch16bit < = x"0000";

elsif OPB_clk'event and OPB_clk ='1' then

if adcdone = '1' then --and dacload = '1' then --G: don't need

latch16bit(15 downto 0)<=adc_dtout(15 downto 0);</pre>

end if;

end if;

end process;

_____

--G:added

--Write the latched data to the SRAM, but divide by 2 first.

process(OPB_Clk, OPB_Rst)

begin

if OPB_Rst='1' then

sram_dt_wr(15) < = latch16bit(15);</pre>

sram_dt_wr(14) < = latch16bit(15);</pre>

sram_dt_wr(13) < = latch16bit(14);

sram_dt_wr(12) < = latch16bit(13);</pre>

```

```

sram_dt_wr(11) < = latch16bit(12);</pre>

sram_dt_wr(10) < = latch16bit(11);</pre>

sram_dt_wr(9) < = latch16bit(10);</pre>

sram_dt_wr(8) < = latch16bit(9);

sram_dt_wr(7) < = latch16bit(8);</pre>

sram_dt_wr(6) < = latch16bit(7);</pre>

sram_dt_wr(5) < = latch16bit(6);

sram_dt_wr(4) < = latch16bit(5);</pre>

sram_dt_wr(3) < = latch16bit(4);</pre>

sram_dt_wr(2) < = latch16bit(3);

sram_dt_wr(1) < = latch16bit(2);</pre>

sram_dt_wr(0) < = latch16bit(1);</pre>

--sram_dt_wr(14 downto 0) < = latch16bit(15 downto 1);

end if;

end process;

--fsm of delay process-----

process(OPB_Clk,OPB_Rst)

begin

if OPB_Rst='1' then

c_state<=idling;

elsif OPB_Clk'event and OPB_Clk='1' then

c state<=n state;

end if;

end process;

--state machine combinational logic

FSM_Comb_wr_to_SRAM: process(OPB_Rst,trigger,c_state)

begin

sram_rnw<='1'; --always reading</pre>

s done<='0';

if rst='1' then

n_state <= idling;

else

case c_state is

when idling =>

if trigger='1' then

n_state<=s1;

else

n_state<=idling;

end if:

when s1 = >

--wait for calculation to be done

```

```

n_state<=s2;

when s_{2} = >

--store new data to SRAM

sram_rnw<='0'; --write to sram</pre>

s done<='1';

n_state<=idling;

when others =>

n_state<=idling;

end case;

end if:

end process;

--generate current address for writing or MB_reading.

process(OPB_Clk,OPB_Rst)

begin

if rst='1' then

sram_addr<="00000000000000000"; --sr_addr<="000101110111000000";

--starts at 24000

elsif OPB_Clk'event and OPB_Clk='1' then

if c_state=s1 then

sram_addr<=audio_wr_addr;</pre>

else

sram_addr<=MB_read_addr; --GUY: NO NEED (?)</pre>

end if;

end if;

end process;

--G: NOTE c_addr was changed to audio_wr_addr;

--update current SRAM address --

process(OPB_Clk,OPB_Rst)

begin

if OPB_Rst='1' then

audio_wr_addr <= "00000000000000000"; --24000, 1/2sec delay

elsif OPB_Clk'event and OPB_Clk='1' then

audio_wr_addr <= audio_wr_addr + 1;</pre>

end if;

end process;

```

```

-----

```

--GUY:

--- generate trigger for writing into SRAM when audio data is ready------

-- disables MicroBlaze from reading while data is being written to SRAM------

```

process (OPB_Clk,OPB_Rst)

begin

if OPB_Rst = '1' then

trigger<='0';

en MB read \leq = '0';

elsif OPB_clk'event and OPB_clk ='1' then

if adcdone = '1' then

trigger<='1';

en_MB_read <= '0';

else

trigger < = '0';

en_MB_read <= '1';

end if;

end if;

end process;

----control initialization for audio codec-----

--op0 op1 op2 a0 a1 a2 a3 a4 d0 d1 d2 d3 d4 d5 d6 d7

c_datain<= "111000000100000"; --c_datain<= "1110100010001000";

process (bclk, OPB_Rst)

begin

if OPB_Rst = '1' then

c_state <= pre_init;

elsif bclk'event and bclk='1' then

c_state<=n_state;

end if;

end process;

process (Irclk, OPB_Rst)

begin

if OPB_Rst = '1' then

initcnt \leq X''0000'';

elsif Irclk'event and Irclk='1' then

initcnt \leq = initcnt + 1;

end if;

end process;

process (initcnt(15),c_state,c_done)

begin

c wr < = '0';

case c_state is

when pre_init =>

```

```

--wait for initcnt

if initcnt(15) = '1' then

n_state<=c_wr_wait;

else

n_state<=pre_init;

end if;

when c_wr_wait =>

--hold c_wr for 1 cycle

c_wr<='1';

n_state<=wait_done;

when wait_done =>

if c_done='1' then

--normal operation

n_state<=norm;

else

n_state<=wait_done;

end if;

when norm =>

n_state<=norm;

when others =>

n_state<=pre_init;

end case;

```

end process;

end Behavioral;

8. C

//This code still needs to be modified so that the input will be from //the SRAM rather than a file. Also, all data will have to be converted //to int or short type (instead of float).

```

#include <stdio.h>

#include <stdlib.h>

/* sampling frequency */

#define FREQ 44100

/* size of one processing block */

#define BLOCKSIZE 330

#define STEP 4

/* */

/* for derivative */

#define Delta 0.001

int main(void)

{

FILE *fp, *fout;

int i, j, index, length, position;

int k = 0;

float tempval;

float *tempdata;

float data[BLOCKSIZE];

float temp;

float output[BLOCKSIZE];

float diff[BLOCKSIZE];

float zerocross[BLOCKSIZE];

float maxima[BLOCKSIZE];

char ch[BLOCKSIZE * STEP];

int itr = 0;

/* Read data from voice file */

if ((fp = fopen("sample.txt", "r")) == NULL)

fprintf(stderr, "Cannot open %s\n", "sample.txt");

/* The whole voice data; Will be limited by the RAM size */

tempdata = (float *) calloc(220500, sizeof(float));

/* 220500 as (BLOCKSIZE * STEP)

* One processing block.

*/

```

```

/* Write the voice file into tempdata */

i = 0;

if (fp != NULL) {

while ((feof(fp) == 0) && (i < 1000000)) {

fscanf(fp, "%s", &ch);

tempval = strtod(ch, NULL);

tempdata[i] = tempval;

i++;

}

}

printf("%d\n",i);

/* Return the total number of processing block */

printf("\nThe length of the whole sample: %d\n", i-1);

itr = 0;

length = i - 1;

while (itr < length) {

/* Sample every STEP'th data from each BLOCKSIZE*STEP */

for (i = 0; i < BLOCKSIZE; i++) {

data[i] = tempdata[i * STEP + itr];

}

/* Processing begins */

/* Half-autocorrelation

* We only care about the distance from peak */

for (i = 0; i < BLOCKSIZE; i++) {

j = 0;

output[i] = 0;

while ((j + i) < BLOCKSIZE) {

temp = data[j] * data[j + i];

output[i] = output[i] + temp;

i = i + 1;

}

}

/* First derivative and sign function */

temp = 0;

for (i = 0; i < (BLOCKSIZE - 1); i++) {

diff[i] = 0;

diff[i] = (output[i + 1] - output[i]) / Delta;

if (diff[i] > 0)

```

```

diff[i] = 1;

else if (diff[i] < 0)

diff[i] = -1;

}

diff[BLOCKSIZE - 1] = 0;

/* Zero Crossing, removing positive ones, flipping x-axis,

* and impulses at maxima with magnitude values */

for (i = 0; i < (BLOCKSIZE - 1); i++) {

zerocross[i] = 0;

zerocross[i] = (diff[i + 1] - diff[i]) / Delta;

if (zerocross[i] > 0)

zerocross[i] = 0;

else

zerocross[i] = zerocross[i] * (-1.0);

maxima[i] = zerocross[i] * output[i];

if (maxima[i] > temp) {

temp = maxima[i];

index = i;

}

}

/* Need to bring it back to correct sampling rate */

position = index * STEP;

zerocross[BLOCKSIZE - 1] = 0;

maxima[BLOCKSIZE - 1] = zerocross[BLOCKSIZE - 1] *

output[BLOCKSIZE - 1];

printf("n^** %d'th Pitch ***n^{"}, ++k);

printf("Pitch is at %d'th in the Maxima array\n\n", index);

printf("The value at that index: %e\n\n", maxima[index]);

printf("The (%d Hz / Index) is: %f\n\n", FREQ, FREQ/(double)position);

itr = itr + BLOCKSIZE * STEP;

fout = fopen("pitch_result.txt", "a");

fprintf(fout, "%f\n", FREQ / (double)position);

fclose(fout);

}

printf("\nWe've detected %d pitches so far!\n\n", k);

fclose(fp);

free(tempdata);

return 0;

```

}