## **Repurposing Software Defenses with Specialized Hardware**

Kanad Sinha

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

**COLUMBIA UNIVERSITY**

2019

#### **ABSTRACT**

#### Repurposing Software Defenses with Specialized Hardware

#### Kanad Sinha

Computer security has largely been the domain of software for the last few decades. Although this approach has been moderately successful during this period, its problems have started becoming more apparent recently because of one primary reason — performance. Software solutions typically exact a significant toll in terms of program slowdown, especially when applied to large, complex software. In the past, when chips became exponentially faster, this growing burden could be accommodated almost for free. But as Moore's law winds down, security-related slowdowns become more apparent, increasingly intolerable, and subsequently abandoned. As a result, the community has started looking elsewhere for continued protection, as attacks continue to become progressively more sophisticated.

One way to mitigate this problem is to complement these defenses in hardware. Despite lacking the semantic perspective of high-level software, specialized hardware typically is not only faster, but also more energy-efficient. However, hardware vendors also have to factor in the cost of integrating security solutions from the perspective of effectiveness, longevity, and cost of development, while allaying the customer's concerns of performance. As a result, although numerous hardware solutions have been proposed in the past, the fact that so few of them have actually transitioned into practice implies that they were unable to strike an optimal balance of the above qualities.

This dissertation proposes the thesis that it is possible to add hardware features that complement and improve program security, traditionally provided by software, without requiring extensive modifications to existing hardware microarchitecture. As such, it marries the collective concerns of not only users and software developers, who demand performant but secure products, but also that of hardware vendors, since implementation simplicity directly relates to reduction in time and cost of development and deployment. To support this thesis, this dissertation discusses

two hardware security features aimed at securing program code and data separately and details their full system implementations, and a study of a negative result where the design was deemed practically infeasible, given its high implementation complexity.

Firstly, the dissertation discusses code protection by reviving instruction set randomization (ISR), an idea originally proposed for countering code injection and considered impractical in the face of modern attack vectors that employ reuse of existing program code (also known as code reuse attacks). With Polyglot, we introduce ISR with strong AES encryption along with basic code randomization that disallows code decryption at runtime, thus countering most forms of state-of-the-art dynamic code reuse attacks, that read the code at runtime prior to building the code reuse payload. Through various optimizations and corner case workarounds, we show how Polyglot enables code execution with minimal hardware changes while maintaining a small attack surface and incurring nominal overheads even when the code is strongly encrypted in the binary and memory.

Next, the dissertation presents REST, a hardware primitive that allows programs to mark memory regions invalid for regular memory accesses. This is achieved simply by storing a large, predetermined random value at those locations with a special store instruction and then, detecting incoming values at the data cache for matches to the predetermined value. Subsequently, we show how this primitive can be used to protect data from common forms of spatial and temporal memory safety attacks. Notably, because of the simplicity of the primitive, REST requires trivial microarchitectural modifications and hence, is easy to implement, and exhibits negligible performance overheads. Additionally, we demonstrate how it is able to provide practical heap safety even for legacy binaries.

For the above proposals, we also detail their hardware implementations on FPGAs, and and discuss how each fits within a complete multiprocess system. This serves to give the reader an idea of usage and deployment challenges on a broader scale that goes beyond just the technique's effectiveness within the context of a single program.

Lastly, the dissertation discusses an alternative to the virtual address space, that randomizes the sequence of addresses in a manner invisible to even the program, thus achieving transparent randomization of the entire address space at a very fine granularity. The biggest challenge is to achieve this with minimal microarchitectural changes while accommodating linear data structures in the program (e.g., arrays, structs), both of which are fundamentally based on a linear address space. As a result, this modified address space subsumes the benefits of most other spatial randomization schemes, with the additional benefit of ideally making traversal from one data structure to another impossible. Our study of this idea concludes that although valuable, current memory safety techniques are cheaper to implement and secure enough, so that there are no perceivable use cases for this model of address space safety.

## **Contents**

| List of Tables |      |                                                   | iv<br>vi |  |

|----------------|------|---------------------------------------------------|----------|--|

|                |      |                                                   |          |  |

| 1              | Intr | oduction                                          | 1        |  |

|                | 1.1  | Software Based Defenses                           | 4        |  |

|                |      | 1.1.1 Why Software?                               | 4        |  |

|                |      | 1.1.2 Can it Keep Up with Attacks?                | 5        |  |

|                | 1.2  | Hardware Based Defenses                           | 6        |  |

|                |      | 1.2.1 Why Hardware?                               | 6        |  |

|                |      | 1.2.2 But It is No Silver Bullet                  | 7        |  |

|                | 1.3  | Thesis and Contributions                          | 9        |  |

| 2              | Bacl | kground                                           | 12       |  |

|                | 2.1  | Baseline Architecture                             | 13       |  |

|                | 2.2  | Semantic Metadata Based Defenses                  | 14       |  |

|                | 2.3  | Tagged Defenses                                   | 16       |  |

|                | 2.4  | Cryptographic Defenses                            | 17       |  |

|                | 2.5  | Logging or Monitoring Based Defenses              | 18       |  |

| 3              | Revi | iving Instruction Set Randomization with Polyglot | 19       |  |

|                | 3.1  | Introduction                                      | 20       |  |

|                | 3.2  | Background and Motivation                         | 23       |  |

|                |      | 3.2.1 Previous ISR Schemes                        | 23       |  |

|                |      | 3.2.2 ISR against Code-Reuse Attacks              | 24       |  |

|                | 3.3  | Adversarial Model                                 | 25       |  |

|                | 3.4  | System Architecture                               | 26       |  |

|                |      | 3.4.1 Software                                    | 26       |  |

|                |      | 3.4.2 Hardware                                    | 28       |  |

|                |      | 3.4.3 Design Choice Implications                  | 34       |  |

|                | 3.5  | Implementation Details                            | 35       |  |

|                |      | 3.5.1 Software                                    | 36       |  |

|                |      | 3.5.2 Hardware                                    | 37       |  |

|                | 3.6  | Security Analysis                                 | 40       |  |

|   |      | 3.6.1 Motivating Strong Encryption        | 0 |

|---|------|-------------------------------------------|---|

|   |      | 3.6.2 Effectiveness                       |   |

|   |      | 3.6.3 Proof-of-Concept Exploit            | 2 |

|   | 3.7  | Ecosystem                                 | 4 |

|   |      | 3.7.1 Challenges                          | 4 |

|   |      | 3.7.2 Distribution Models                 | 6 |

|   |      | 3.7.3 Key Management                      | 7 |

|   | 3.8  | Evaluation                                | 7 |

|   |      | 3.8.1 Performance                         | 8 |

|   |      | 3.8.2 FPGA Implementation Results         |   |

|   | 3.9  | Related Work                              |   |

|   |      | Conclusion                                |   |

|   | 5.10 | Conclusion                                | _ |

| 4 | Prac | tical Memory Safety with REST 5           | 3 |

|   | 4.1  | Introduction                              | 4 |

|   | 4.2  | Motivation                                | 8 |

|   | 4.3  | Hardware Design                           |   |

|   |      | 4.3.1 ISA Modifications                   |   |

|   |      | 4.3.2 Microarchitecture                   | 2 |

|   | 4.4  | Software Design                           |   |

|   |      | 4.4.1 Userlevel Support                   |   |

|   |      | 4.4.2 System Level Support                |   |

|   | 4.5  | Hardware/Software Security                |   |

|   | 1.5  | 4.5.1 Threat Model                        |   |

|   |      | 4.5.2 Hardware Discussion                 |   |

|   |      | 4.5.3 Software Discussion                 |   |

|   | 4.6  | Evaluation                                |   |

|   | 4.0  | 4.6.1 Performance Overheads               |   |

|   |      | 4.6.2 FPGA Area Overheads                 |   |

|   | 4.7  | Related Work                              |   |

|   | 4.7  | Conclusion                                |   |

|   | 4.0  | Conclusion                                | _ |

| 5 | Addı | ress Space as a Primary Line of Defense 8 | 5 |

|   | 5.1  | Introduction                              |   |

|   | 5.2  | Motivation                                |   |

|   | 0.2  | 5.2.1 The Address Interface               |   |

|   |      | 5.2.2 Exploiting the AGI                  |   |

|   | 5.3  | Related Work                              |   |

|   | 5.4  | Apparent Address Space                    |   |

|   | Э.т  | 5.4.1 Security Implications               |   |

|   |      | 5.4.2 Challenges                          |   |

|   | 5.5  | Implementation                            |   |

|   | ٥.5  | 5.5.1 Hardware Design                     |   |

|   |      | 5.5.2 Software Support                    |   |

|   |      | 5.5.3 Security Evaluation 9               |   |

|   |      | 7. J. J. J. ANA/ULILY L/VALUATION         |   |

|    | 5.5.4 Feasibility                                  |       |  |  |

|----|----------------------------------------------------|-------|--|--|

| 6  | Concluding Remarks                                 | 101   |  |  |

|    | .1 Lessons Learned                                 | . 102 |  |  |

| Bi | iography                                           | 105   |  |  |

| Aj | Appendix 11                                        |       |  |  |

|    | Algorithms Used to Leak XOR and Transposition Keys | . 116 |  |  |

# **List of Figures**

| 2.1 2.2    | Generic baseline architecture and its hardware security mechanisms                                                                                                                                                                                       | 13<br>15 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

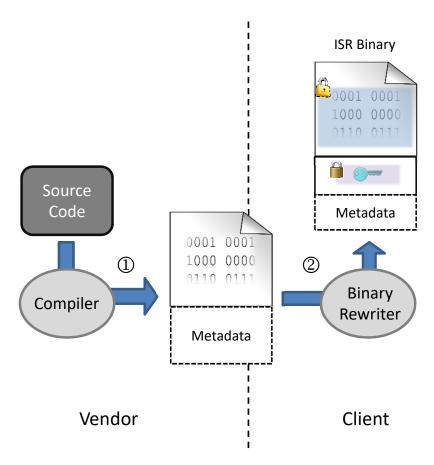

| 3.1<br>3.2 | High-level overview of Polyglot                                                                                                                                                                                                                          | 21       |

|            | pointer to the next level, whereas PTE is the final translation                                                                                                                                                                                          | 27       |

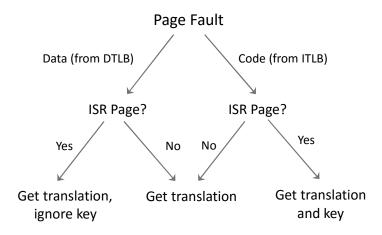

| 3.3<br>3.4 | ISR page fault handling flowchart                                                                                                                                                                                                                        | 29       |

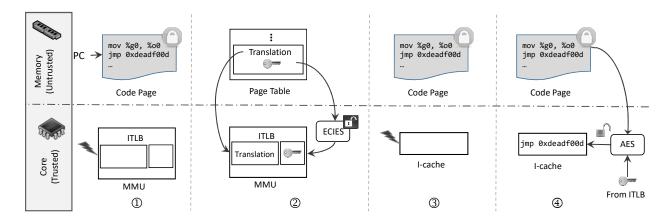

| 3.5        | decrypted using the page key before dropping into I-cache                                                                                                                                                                                                | 30       |

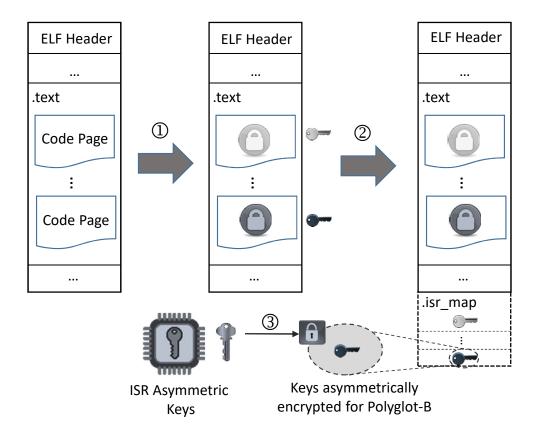

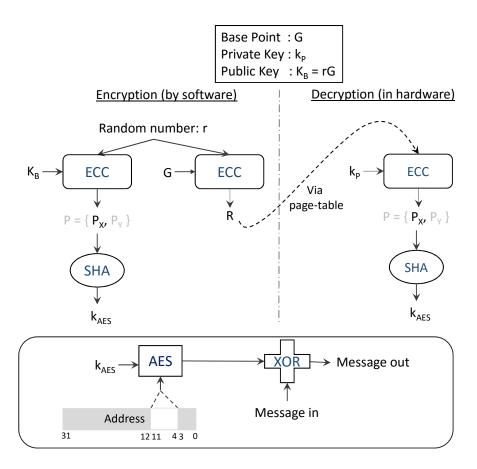

| 3.6        | the target system's public key, and embedded within a new section of the ELF binary. Encryption and decryption in the ECIES scheme. Letters in caps indicate points in the Gaussian space which have consist of x- and y- coordinates. Base point, G, is | 36       |

| 3.7        | specified by the standards                                                                                                                                                                                                                               | 39       |

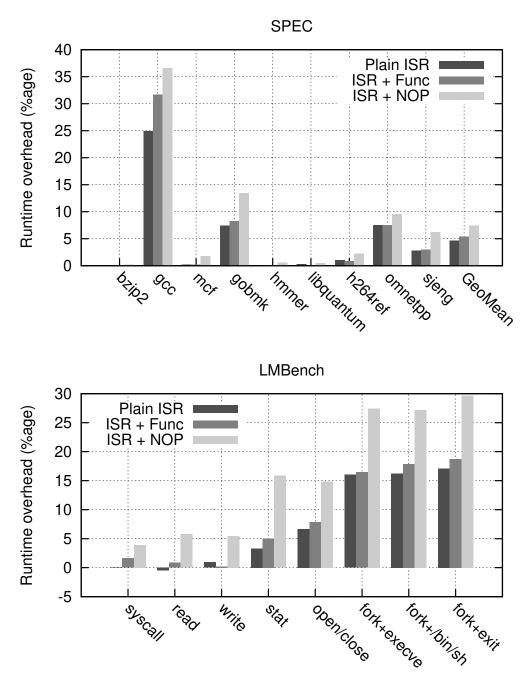

| 3.8        | final ISR binary                                                                                                                                                                                                                                         | 45<br>49 |

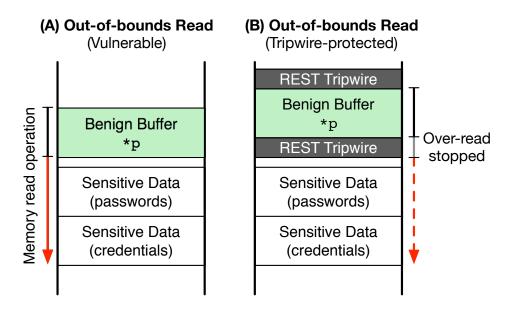

| 4.1        | (A) Unsanitized memcpy bug reads sensitive data outside the benign buffer. (B) REST tokens placed around the buffer detects this out-of-bounds access                                                                                                    | 58       |

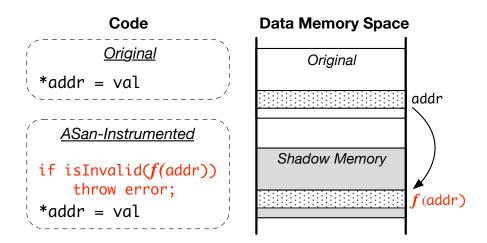

| 4.2        | Code and address space transformation done by ASan. Memory accesses are instrumented to check against the corresponding value in the shadow memory (dark                                                                                                 |          |

| 4.0        | region in figure), calculable with a simple mapping function, $f$                                                                                                                                                                                        | 59       |

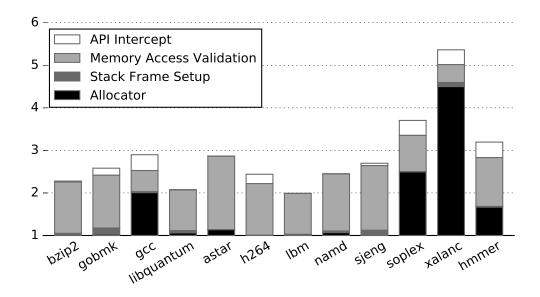

| 4.3        | Breakdown of various sources of overhead in ASan with respect to a plain binary using libc's allocator                                                                                                                                                   | 60       |

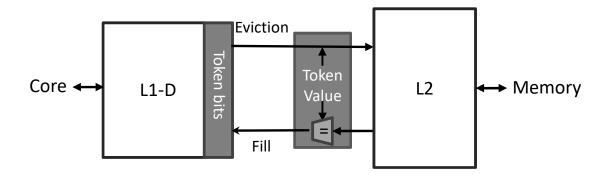

| 4.4        | Hardware modifications for <i>REST</i> include an extra metadata bit per cache line in L1 data cache indicating whether it contains a token, and the token detector to                                                                                   |          |

|            | examine incoming data from lower caches and fill the token value into evicted lines.                                                                                                                                                                     | 62       |

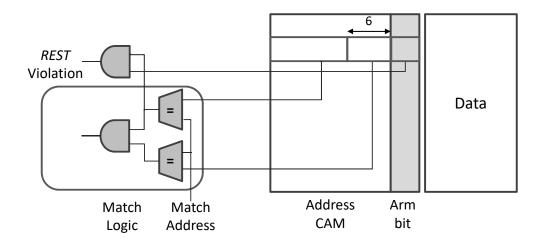

| 4.5        | Modifications to the LSQ. Added structures are noted in darker shade                                                                                                                                                                                     | 65       |

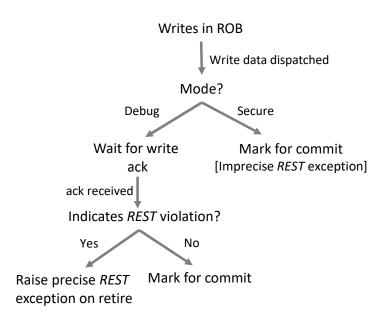

| 4.6        | Flowchart showing write commit logic for <i>REST</i>                                                                                                                                                                                                     | 66       |

| 4.7  | (A) For stack safety we instrument the program to insert tokens around vulnerable |    |

|------|-----------------------------------------------------------------------------------|----|

|      | buffers. (B) Our allocator provides heap safety by surrounding allocations with   |    |

|      | tokens and blacklisting deallocated regions in the quarantine pool                | 68 |

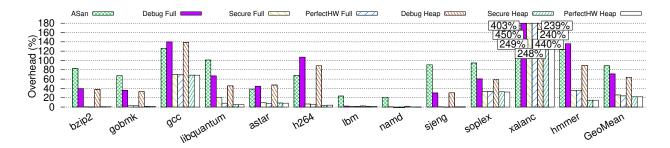

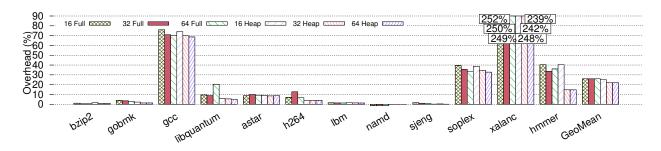

| 4.8  | Runtime overheads (over plain) of ASan and REST in the debug, secure, and per-    |    |

|      | fect (zero-cost) hardware modes while providing full and heap safety              | 76 |

| 4.9  | Runtime overheads (over plain) of using 16B, 32B and 64B tokens in secure mode.   | 76 |

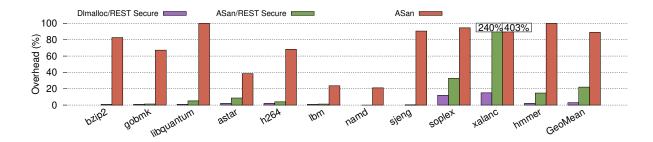

| 4.10 | Runtime overheads (over plain) of heap protection with dlmalloc. ASan/REST and    |    |

|      | ASan results are also shown again for reference                                   | 78 |

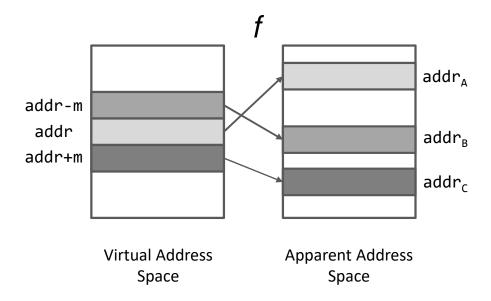

| 5.1  | Apparent Address Space as an Abstraction over the Virtual Address Space           | 92 |

| 5.2  | Tagging scheme employed for coloring memory objects in AAS                        |    |

## **List of Tables**

| 3.1 | Comparison of various ISR proposals. (*Shared library support does not necessarily imply sharing them across processes, unless code sharing is allowed.) | 23 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Actions taken on various operations for L1-D cache hits and misses                                                                                       | 64 |

| 4.2 | Simulation base hardware configuration                                                                                                                   | 74 |

| 4.3 | Comparison of previous hardware techniques (assuming single-core systems for                                                                             |    |

|     | simplicity). †Although MPX-supported binaries execute with modules that are not                                                                          |    |

|     | protected, metadata is dropped when such modules manipulate an MPX-augmented                                                                             |    |

|     | pointer. ‡See text                                                                                                                                       | 84 |

## Acknowledgements

This doctorate may not be the hardest thing I have attempted, but it is by far the hardest thing I have achieved. There were times when doubts almost led me to quit, but I am glad I persevered. Many are to blame for getting me past the finish line.

Needless to say, the biggest credit goes to my advisor, Simha. Beyond the wealth of know-how I have acquired from him over the years, his most important lessons have been completely non-technical. He has deeply affected my perception of knowledge, and reformed my outlook towards learning in general. I am deeply grateful for his patience and encouragement throughout, especially in times when research involved just hopelessly searching. If there is one thing I can take away from my time here, I hope it is his ability to have faith in a vision.

I am also very grateful to the other faculty members at the department, particularly Luca Carloni, Martha Kim, Steve Bellovin, and Suman Jana, for the guidance and advice they provided me whenever I sought them. From my numerous discussions and seminars with them, I am humbled by the depth of their intellectual curiosity, and hope to emulate it in my future life. Last but not least, I thank my unofficial "co-advisor", Vasileios Kemerlis, who, while a graduate student here, found the time and patience to show a novice the ropes in the tricky field of security research.

A lot of friends, especially past and present occupants of CSB 467, have brightened my graduate life at Columbia. In no particular order, my heartfelt thanks to Hiroshi Sasaki, Melanie Kambadur, Paolo Mantovani, Emilio Cota, Andrea Lottarini, John Demme, Adam Waksman, Yipeng Huang, Jared Schmitz, Miguel Arroyo, Joel Porquet, Chester Rebeiro, Kshitij Bharadwaj, Giuseppe Di Guglielmo, Davide Giri, Luca Piccolboni, YoungHoon Jung, Young Jin Yoon, Christian Pilato, Richard Townsend. Vasilis Pappas, Theofilos Petsios, David Williams-King, and others. Of those I did not list, I cannot forget to name Adrian Tang, who motivated and distracted me in the right ways and at the right times, especially when the weight of a PhD proved difficult to bear.

Beyond Columbia, I was also lucky to have a few friends along the way, whose support and help were crucial to get me where I stand now. Of them, I have to mention Alok Sood, who consistently reminded me the meaning of friendship, Courtney Truesdell, who reminded me that much of life is the people in it, and Amit Malik, who was always there even when he was not.

And finally, heartiest thanks to my family, the new ones I found in this country and those I left at home. The warmth of their love (and food) buoys me in times when I am overwhelmed by the life of a researcher. Especially, my parents, my gratitude to whom I cannot even begin to express. In their endless pool of faith in me, I try to see my reflection when my own self-belief wanes. I continue to strive to be the person they have always seen in me.

- Kanad

To Baba and Mum,

and

my good friend, Alok

## CHAPTER 1

### Introduction

Since the first stack overflow based computer worm was first launched by Robert Morris in 1988, attackers have developed ever sophisticated techniques for bypassing program security, while the defenders continuously try to develop measures to thwart them. Historically, this has resulted in a fascinating trend of cat-and-mouse, so that attackers and defenders are always engaged in an adversarial battle of one-upmanship. However, despite the best efforts of security researchers, attacks are still widely prevalent costing organizations and users significant economic loss. While there are many reasons for this, two major factors have persistently contributed to this state of affairs over the long-term.

First, as sophisticated as attack techniques are becoming, it is trivial compared to the rate at which the complexity of commercial software has grown. For instance, a modern browser includes a Javascript engine/interpretor, PDF viewer, multiple extensions, etc., is written in several languages, and has tens of millions of lines of code. More complexity implies a higher density of bugs, lower test coverage, and a larger attack surface. Pre-deployment detection of errors via testing and validation techniques have come a long way in the recent past with significant research and

development being done in the areas of rapid bug detection with tools like AddressSanitizer [100], larger test coverage with various forms of fuzzing, limiting the scope of bugs/attacks with software fault isolation, and so on. Even so, the state-of-the-art in validation lags far behind still, and is nowhere close to accounting for the discovery of all bugs and their scope of exploitation in production software.

Another reason for this is the prevalence of memory-unsafe languages like C and C++, which do not abstract away the address space and allow the program direct access to memory and its contents. Unmitigated access to raw memory means bugs have a higher scope of impact since no checks are built in at the language level to prevent semantically illegitimate accesses. The fact that they have been around for decades also means that there is a significant legacy code base of these languages. Although many type-safe languages have been developed since, prevalence of legacy code and the speed advantage enjoyed by these unmanaged languages has resulted in their continuing popularity among developers in the present and foreseeable future.

In response, security engineers have amassed a rich body of safety measures that aim to counter attacks while being minimally intrusive on the program. Traditionally, these techniques have primarily been implemented at various levels of software ranging from compiler-based static analyses to runtime defensive monitors. Besides some basic hardware support like that for paging, this has remained the status quo for the past few decades, wherein software has borne the brunt of the responsibility for security. However, due to multiple factors, performance being foremost among them, software-based security has not scaled well. As developers stack ever-increasing number of features, while seeking to keep performance overheads at a minimum, it is thus the case that security mechanisms are the ones that get side-tracked or abandoned.

To overcome this problem, hardware designers have lately picked up the gauntlet by providing features that either augment existing security schemes or implement them in its entirety. Employing special hardware for this purpose is highly promising since it potentially mitigates the critical issue of performance faced by software solutions. This has led to proposal of numerous hardware based security solutions in the last decade. Furthermore, as the cost of failure and economic

demand for safety rises, hardware vendors have jumped into the fray, announcing numerous instruction set architecture (ISA) extensions. Consequently, major design houses like Intel, ARM, and SPARC have introduced features to combat memory errors [3, 48, 53], pointer corruption [97], control flow integrity [27], isolated execution [75, 84], etc. in recent years.

As heartening as this trend might seem, we have to ask ourselves one crucial question: for all the advantages that specialized hardware provides and the number of hardware solutions proposed so far, why are more of them not seen in deployment today or even included in future microprocessor iterations? The answer partially lies in the process of hardware design and the considerations that go into it. Due to the long time-to-market (of the order of a few years typically), longevity of architectural specifications, and relative immutability of hardware, vendors are hesitant in adding new features if their effectiveness on deployment is uncertain. This is more pronounced when the solution in question is complex, so that integrating it into existing designs becomes intrusive, expensive, and difficult to validate. Hence, the fact that most previously proposed solutions have not translated to commercial implementations implies that hardware security researchers have not hit the right trade off of the aforementioned criteria favorably.

To this end, my research has sought to explore and enable the design of hardware features that are simultaneously effective as security measures, while requiring simple modifications to hardware, thus increasing their chances of deployment. Three case studies are presented in this dissertation that look at different approaches to securing program code and data against external exploitation. Of the three, two are positive studies wherein the first discusses a technique for securing code against runtime disambiguation and injection, whereas the second discusses a solution for practically securing data against malicious memory corruption and manipulation. The third case study presents a negative result involving a technique that seeks to secure the address space as a whole against unwanted memory disclosures, but the implementation overhead was found to be too high, thus making it impractical. With these studies, I hope to motivate the central thesis of this dissertation that asserts the design of low overhead, low complexity, yet effective hardware solutions to augment system security.

#### 1.1 Software Based Defenses

#### 1.1.1 Why Software?

Software based defensive schemes have been and remain the norm in the computer security, and for good reason. Software is cheap to develop, deploy, and update. Thus, the time from the discovery of a bug, to the development of its patch, to pushing the updates to client systems is fairly quick and the process easy. In fact, most software systems are engineered and maintained to accommodate such operations, with advances currently being made in even live patching of systems without any downtime. This is especially critical for security patches, since some of these bugs can be exploited en masse within a short period (especially for web-facing programs), thus increasing their fallout.

Additionally, since software solutions have access to the high-level semantic information of the program, they are easier to reason about and apply. For instance, consider a simple buffer overflow. At the level of the language, the notion of bounds exists and hence, it is easier to determine when they have been violated. This information is absent at the machine level where all that is visible is a flat memory space. Hence, a defense against overflows is potentially easier to implement at the language level, than anywhere below. Consequently, a whole slew of compiler-based software tools have been developed [38, 39, 62, 81] to ensure memory safety for C-based programs. In fact, even hardware based defenses often rely on semantic information passed down to enforce bounds more accurately [36, 79, 105].

A third reason is probably just awareness and the lack of efficient collaboration among software and hardware researchers. Software bugs are easier fixed by people who understand software and how/what attack vectors are/can be utilized to exploit them. Traditionally, software developers have not had a good understanding of hardware microarchitecture or at least, do not have an open channel of communication with hardware developers. Vice versa applies for hardware developers, who are generally unaware of security concerns in software, and do not necessarily have the "hacker mindset". They have only been concerned with power and performance which is what the market has demanded of them thus far. The ramifications of this lack of awareness among hardware designers was made painfully clear with the discovery of the Spectre [60] and Meltdown [68] attacks, which are a direct consequence of some fundamental tenets of out-of-order processing, namely speculative execution. Thus, the insular nature of software and hardware development has contributed to an absence of cross-disciplinary approaches to mitigating persistent and potentially forward-looking threat vectors effectively.

#### 1.1.2 Can it Keep Up with Attacks?

For the past several decades, semiconductor technology has progressed in accordance with Moore's law, giving users exponential increments in performance year-on-year without any modifications to code whatsoever. This blanket speedup of general purpose computation allowed increasingly complicated and feature-rich applications to be deployed with nominal to no overhead apparent to the user. Software-based security also benefited from this phenomenon; as these defenses became more complex and hence, more compute- and/or memory-intensive, their overhead could be accommodated due to faster execution speeds. However, as Moore's law comes to an end, other avenues for speeding up selective aspects of execution are now being explored (multicores, accelerators, etc.). Although some specialized hardware modules for security have been developed (TPMs [117], for instance), this new trend has had little to no positive effect on software security. As a result, users are hesitant to employ software defense schemes that may be secure but slow down the system noticeably. This is undesirable since contemporary attacks have evolved in sophistication to the point that current defenses are not effective enough. Attackers are not only exploiting the previous attack vectors in intelligent ways, but are also continuously inventing novel ones. For instance, if we look at the root causes for remote code execution in Microsoft software in the last few years [125], we see that not only are the classic memory attacks still valid and as relevant, but new vectors like type confusion are exploding. With so many diverse threats to protect against, software based solutions struggle to meet the requirements of performance while still being effective.

Furthermore, there is another reason that limits the effectiveness of some software based solu-

tions — privilege. Most of these solutions operate at the same privilege level, indeed in the same address space, as the program. Any attacker advanced enough to have the capability to affect the program, can, hence, affect the security measure as well. Stack canaries, for instance, have been shown to be easily bypassable via simple brute forcing and/or disclosure of canary value [93].

#### 1.2 Hardware Based Defenses

Due to the above shortcomings of software based defenses, security engineers have started looking towards hardware for assistance, thus creating a new paradigm for defensive techniques. Doing so, however, is not as simple as it seems. In order to develop truly secure and practical solutions in hardware, it behooves us to understand the trade offs and considerations that guide their design.

#### 1.2.1 Why Hardware?

As discussed above, the foremost argument for implementing defenses in hardware is, unsurprisingly, performance. In fact, task-specific special purpose hardware is especially commonplace nowadays with modern commercial system-on-chips containing multiple accelerators for common applications like graphics and cryptography. Specialized hardware for a specific task is generally better than an equivalent software implementation in terms of performance and energy, when the task has a well-defined data set and is self-contained. The same principle applies for hardware based defenses as well – if the solution involves operations being performed on clearly disambiguated data operands, it might be a good candidate for hardware implementation. Consider, Softbound [81], a compiler based bounds checking solution aiming to provide spatial memory safety, which checks the validity of every memory access against the bounds defined in the metadata for the pointer being dereferenced. These metadata are, in turn, stored at a known fixed offset from the pointer. The hardware implementation of the same, Hardbound [36], brings down its overhead from 79% to only 5%.

Additionally, there is also the advantage of privilege. Since hardware is at the root of all trust in

the system and has the higher privilege than any piece of software, defenses employed in hardware are harder to disable, manipulate, and/or bypass<sup>1</sup>.

One general concern about hardware based solutions, however, is that they are too low-level and hence, do not observe enough semantic information about the program to effectively detect anomalous behavior. This does not always have to be the case, especially when the attack involves a clear violation of architectural principles that reflect common program behavior (e.g., functions should always return to the instruction after the corresponding call to it). Solutions to more complicated problems have taken the following two approaches so far. Firstly, a hardware-software co-design has been shown to be very effective wherein the hardware takes hints from software, either at runtime or through metadata generated through compile-time analyses. Numerous past works, especially in the area of memory safety, have taken this approach since it was observed in many cases that identification of linguistic constructs like pointers and data structures completely in hardware was imprecise and resulted in false positives/negatives [36]. Simple hints/annotations at the program level, when possible, easily and efficiently mitigated this problem. The second approach is a more recent one wherein the hardware infers semantic information via microarchitectural events. This usually requires training against a golden model so that malicious behavior is signaled whenever this expectation is violated. Although the latter technique has only been shown to be effective for anomaly detection [34], it can potentially be used for detecting more specific attack scenarios.

#### 1.2.2 But It is No Silver Bullet

With all the benefits of hardware based defenses outlined above, the question we need to ask ourselves then is, why not implement all or most defenses in hardware? Or more specifically, where do we draw the line at which point it would make sense to implement a software technique to hardware? To answer this question, we have to understand the various factors and trade-offs that

<sup>&</sup>lt;sup>1</sup>This is a double-edged sword since hardware attacks can also be extremely potent. The recent Spectre, Meltdown, and Rowhammer [59] attacks are cases to this point.

hardware vendors have to contend with for a design to make economic sense.

**Performance.** As fast as specialized hardware can be, they still usually do introduce some slowdown. As such, engineers have to keep the slowdown figures of the design to a few percentage points for it to be viable (depending on the context). Unless they are able to achieve this, the feature will be deemed fairly slow for most practical purposes. It, thus, becomes a trade-off wherein the vendor has to gauge performance overheads of the feature, how critical that security feature is for the client's application, and what portion of the total user base utilize those applications.

**Effectiveness.** This is a crucial factor especially for security measures, since, unlike other performance or usability optimizations/extensions, security measures could potentially become quickly outdated if a new attack vector is discovered. Because hardware is not easily updatable, users would just be burdened with a useless, or in some extreme cases, harmful hardware feature, rendering the vendor's investment in the technology unprofitable. Given major hardware design iterations take several years to go from conception to commercialization, vendors, thus, need to be assured of the importance of the problem in question in the years to come, and the effectiveness of the solution against unpredictable vectors within this period.

Complexity. The complexity of any feature directly correlates to the effort and cost of its integration in the final product. This is because complex solution can interact with and occasionally need modifications in multiple microarchitectural subsystems, thus raising not only the cost of development but also that of validation. Since most commercial microprocessors are already extremely intricate, introducing complex features, security or otherwise, entails an arduous effort, and does not guarantee that new bugs will not be introduced. Furthermore, complex techniques often require power hungry structures, thus increasing the energy budget of the chip, especially if it is an always-on feature.

**Longevity.** Although hardware is not as immutable as most people imagine<sup>2</sup>, they are still highly static compared to the flexibility offered by software. Architectural specifications persist over multiple processor generations, users continue to use the same hardware for years on end.

<sup>&</sup>lt;sup>2</sup>Vendors often release microcode patches to change the functionality of chips on the field.

Tying back to the long-term effectiveness of the measure, it becomes more critical to determine whether the technique exhibits a conservative promise to be a significant deterrent for that attack in the near future. Otherwise, it is hard to justify its inclusion in the final product.

A good hardware solution would, thus, have to assuage all of the above vendor concerns sufficiently and convincingly to make its way into production and sustained usage. Consider Intel MPX [53] for instance. It was released in commercial Intel Haswell processors in 2015, and follows the long line of work in the area of bounds checking support in hardware [36, 45, 79, 80]. This approach required fairly non-trivial changes to hardware and software, and consequently, due to its many issues of compatibility and performance [86], MPX hardly made its way into popular applications. In fact, support for MPX was recently retired in GCC9. Over the last decade, numerous other hardware security features have been proposed in major architectural, systems, and security conferences, and yet only a small handful can be seen in current chips. Even accounting for the fact that, as with other technologies, security ideas need to be improved and cross-validated over multiple iterations before they can be considered refined enough for commercial release, the disparity between research and deployment in hardware security implies a lack of cognizance of the above factors so far.

### 1.3 Thesis and Contributions

In the light of the above discussion, this dissertation makes the following thesis statement:

Hardware support for software-based defenses can not only complement but also improve their efficacy and performance, without requiring extensive modifications to core microarchitecture.

To support the above thesis, this dissertation makes the following contributions in the form of three case studies.

**I. Securing Code.** There exist two main attack vectors for compromising the integrity of code and its flow in a program — code injection attacks and code reuse attacks<sup>3</sup> [114]. Both of these

<sup>&</sup>lt;sup>3</sup>Code pointer corruption might lead to either or both, but we treat it as a data-based attack for this discussion.

techniques have been documented for over 20 years, but are still relevant today. Although code injection was largely mitigated as a primary vector with hardware features like the NX bit and W⊕X, code reuse attacks are still being employed in the wild today. The first contribution of this dissertation is to re-architect a technique called instruction set randomization (ISR) that is considered highly effective against code injection attacks but fundamentally vulnerable to code reuse. In fact with threat models relevant today, even ISR's effectiveness against code injection is questionable. By adding some hardware support, we demonstrate for the first time that our variant of ISR not only prevents code injection attacks under current threat models, but could also effectively counter state-of-the-art code reuse attacks. We achieve this by encrypting code with strong cryptographic primitives statically, and decrypting them just before execution, without adding significant performance overheads. Crucially, as asserted by the thesis of this dissertation, we show how this can be made possible with modifications to the L1 instruction cache and the MMU page walker, thus leaving other core substructures and data caches largely in tact. We also provide a full-system view of this technique highlighting how its protection could be turned on from the very first instruction executed at boot, and the distribution models that need to be in place to accommodate a feature like this.

II. Securing Data. Next in the dissertation, we discuss a novel method for securing data against common types of memory safety violations, which are one of the most long-standing and critical threats in computer security. While previous solutions in this area were effective, they required non-trivial changes to hardware, besides other drawbacks. Our technique, however, introduced hardware support for a simple primitive, i.e., comparison against a large, predetermined random value, and used this primitive to enable practical memory safety in the program with simple software support. Notably, since our primitive itself is so simple, its hardware support is also very trivial (just a comparator at minimum). We also demonstrate how our technique introduces nominal slowdown in the application and is able to provide heap safety even for legacy binaries.

**III. Securing the Address Space.** The final case study in this dissertation presents a negative result, wherein we modify the virtual address space to present a randomized sequence of addresses

to the program instead of the traditional model where addresses follow a linear sequence. This effectively serves to uniformly randomize of the entire address space at a very fine granularity. We argue that doing so prevents the attacker from "traversing" from one data structure to another, thus providing spatial memory safety. It was, however, determined that the implementation and performance cost of this scheme would be too high and would, hence, fail the criteria of our discussion thus far.

## CHAPTER 2

## Background

Before we dive into the case studies, it is useful to understand the general approaches towards implementation of hardware solutions in order to gain a better insight into the related complexity and sources of overhead, independent of the goal of the individual technique. Towards that end, in this chapter, I will broadly classify past and present hardware security solutions that have been proposed to aid or replace problems traditionally handled by software, and discuss the the nature of modification necessary to accommodate them in a modern general-purpose microprocessor. This classification will be based on the type of hardware implementation, rather than the problem it solves or the effectiveness of different proposals constituting the class. In the subsequent chapters, a detailed analysis of the related work for relevant topics will be presented. Also, note that there are other classes of defenses that counter side channel attacks, provide isolation, etc., and so, are tangentially related to code and data security, but from a hardware or privilege standpoint. Such defenses are considered out of scope for the sake of this discussion.

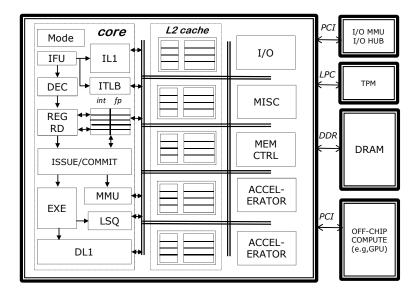

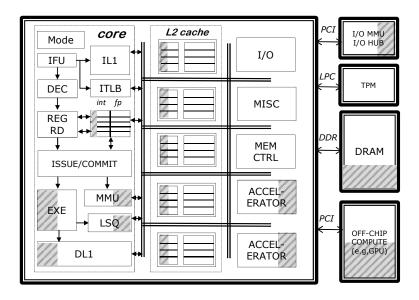

Figure 2.1: Generic baseline architecture and its hardware security mechanisms.

#### 2.1 Baseline Architecture

Prior to discussing various aspects of the cost and benefits associated with particular hardware defenses and the changes they require, we provide the readers with a baseline architectural design against which to evaluate hardware solutions, existing or new.

Figure 2.1 shows the baseline architecture that we use for illustrating all the security techniques. The baseline shows a processor and off-chip components: the off-chip components include DRAM, off-chip compute units which can be GPUs or FPGAs, a TPM and a I/O hub chip which can connects to various peripherals. Inside the processor, without loss of generality, we assume a single core processor but we will point out multicore related issues as they are relevant.

The core includes standard microarchitectural structures: the mode bits determine if the core is in supervisory mode or user mode, the IL1 is the level 1 instruction cache that holds instructions, the ITLB is the translation lookaside buffer which provides virtual to physical address translation for instructions, an instruction fetch unit (IFU), a decoder, a register file that has integer and fp register, an out-of-order issue and commit unit, and several structures for handling memory accesses.

The structures for handling memory accesses include a level 1 data cache, the load store queue

(LSQ) which is used to support reordering of memory requests, MMU which includes the data translation lookaside buffer and different page walking or page walk caching mechanisms. Beyond the core, we assume a L2 cache that is banked, each bank has tags and data. Our baseline chip also includes some special purpose on-chip offload engines (such as a graphics core), a memory controller that reorders and relays request to memory, and I/O controller that relays and manages requests to I/O devices.

All of these on-chip structures are connected by an on-chip network. This baseline is abstract and sufficiently representative to provide intuition on cost/complexity of hardware security mechanisms.

#### 2.2 Semantic Metadata Based Defenses

This class of defenses associates semantic metadata with each pointer in order to ascertain that it is never illegitimately dereferenced. This metadata could take the form of addresses, permissions, and other semantic information regarding the corresponding data structure, and may be stored along with the pointer or in a separate shadow space that reflects the program's memory layout. Works in this category have so far taken one of two forms.

In the first variant, the metadata is used to enforce bounds checking on the pointer at dereference. Each pointer is functionally associated with a corresponding start address and an end address (or length) that specifies the bounds of the pointed structure. In some works, temporal information is also stored that indicates the "version" of the structure, so that if the current structure is deal-located and another allocated in the same region, a pointer dereference of the old structure can be caught. The first hardware support for such a scheme was Hardbound [36], which did not enforce temporal safety. Subsequent works [45, 79, 80] refined this technique to enforce more accurate spatial and temporal bounds. Notably, Intel launched the MPX ISA extension [53] in 2015 that brought this technology into a commercial domain.

The second variant in this class is capability based architectures. Capabilities are a form of

Figure 2.2: Hardware modifications for semantic metadata based defenses (highlighted).

access-control and can be loosely defined as tokens necessary to access a particular resource. Conceptually they can be represented as a data structure consisting of a unique resource-identifier and the associated credential. Privileges are acquired by entities when they receive the appropriate token. These tokens must be unforgeable and are passed to entities, preferably according to the principle of least privileges. Although considered an obsolete technology until recently, CHERI [126] and its follow-up works [22, 23, 123] have revived it, and demonstrated its viability in a practical setup.

Hardware Modifications. Although individual proposals have their own unique design points and optimizations, here we outline common features of a naive design for a typical scheme in this class. Such system conceptually require wider data-paths and memory elements, and access checking circuitry on memory accesses to impose rules dictated by the metadata, which have to be separately accessed. Often techniques provide a separate metadata cache and TLB at the L1, thus functionally extending the existing caches and TLB, to enable fast lookup of metadata. Notably, WatchdogLite handles metadata explicitly just like regular data, while CHERI uses a capability coprocessor a placed next to the pipeline to perform the latter. The hardware units that are affected are shown in Figure 2.2.

## 2.3 Tagged Defenses

This type of defense is similar to the previous class in that they use metadata (often called tags, in this context), but in this class they are usually just one or a few bits. The tags indicate a state, only meaningful in the context the defense operates. Depending on the solution, these tags could be semantically attached to memory locations, pointers, and/or data. For instance, some techniques [96, 107, 119] attach tags to memory to validate if can be accessed or not. Some [3, 48] go still further by attaching tags to pointers as well, to enforce a degree access control by mandating that tags of pointers and accessed location match.

A more advanced form of this class of defense is dynamic information flow tracking (DIFT) [113]. DIFT uses metadata or *taints* to track the flow of untrusted information within the system, to make sure that it does not unexpectedly affect any trusted or secret portion of the system, or otherwise leak it on untrusted channels. The idea is that if at least one of the operands for an operation is untrusted, the output is untrusted as well and should be limited in its ability to interact with other elements of the program. The same goes for all operations involving this output, and so on. Depending on how the tags are propagated and checked, what gets tainted, and who monitors them, DIFT can be used for a variety of purposes from access control to information leakage.

Hardware Modifications. The degree of tagging support is dependent on what is being tagged and how tags are propagated. Conceptually, the modifications required are similar to the previous class. To detect flow of data through the processor, the data pathways – memory elements (register file, microarchitectural registers, and buffers) and buses/interconnection networks – have to be extended by the tag-width. In practice, however, when the tags are narrow enough, some solutions have leverage/repurpose ECC bits in main memory for tags [3, 48]. Some current solutions aimed at 64-bit architectures also use the unused higher order of the address to store pointer tags, thus significantly lowering the hardware requirements. Depending also on whether the data and tags can be atomically accessed, one or more memory accesses may be necessary for each data access. Additionally, for DIFT, to taint the output of operations involving tainted data, a small OR gate is necessary around computational units which takes as input the taint statuses of the inputs, and

marks the output tainted if any of the inputs are tainted. Since both classes are based on per memory metadata, the hardware modifications for this class are similar to that of the previous class shown in Figure 2.2.

## 2.4 Cryptographic Defenses

Although cryptography has been a popularly used mechanism for data integrity and secrecy, there have only been a handful proposals that utilize it to protect code and data at the process abstraction level. Hence I will give a brief overview of some notable techniques individually below.

ASIST [88] is the first hardware scheme proposed to support ISR (discussed in more detail in chapter 3). Essentially, it encrypts program code with simple XOR or bit transposition. This is done at runtime with a simple key, programmable into a register, which decrypts instructions just before they are stored in the L1 instruction cache. Polyglot [104] operates similarly except it uses stronger AES encryption, besides asymmetrically encrypting the code encryption keys as well. Details of these technique are discussed in more detail in the next chapter.

Recently, a similar randomization technique, called HARD [8] for data was proposed that statically determined equivalence classes of data based on the instruction they were accessed from. These classes were then XOR-encrypted with the same key and the key associated with the instruction(s). Recently, ARM also announced a pointer authentication technology [97], wherein all pointers can be encrypted with a master key and authenticated at dereference. This is to counter out-of-band corruption or forging of original pointers, for instance, through an overflow of a buffer into a neighboring pointer variable.

Hardware Modifications. The techniques outlined above have completely different purposes and hence do not share any common design features except the addition of a decrypting unit. For ASIST and Polyglot, this unit is added at the memory facing interface of the L1 instruction cache and is just a XOR or a large decoder structure. In case of ARM pointer authentication, although design details have not been disclosed publicly, a naive design would introduce an encryption and

decryption engine in the pipeline as an additional functional unit. HARD also adds caches around the pipeline and decryption units. Overall, above techniques introduce small overheads on the baseline architecture depending on the specific cryptographic algorithm used and where in the data path the operations occur.

## 2.5 Logging or Monitoring Based Defenses

Many novel ideas have lately been proposed that leverage microarchitectural logs present in modern microprocessors (hardware performance counters, branch direction stores, etc.) to detect attacks or otherwise anomalous program execution. One of the challenges of utilizing hardware logs is the fact that they may not capture enough information about the execution software, be it the OS or individual programs on it, so much so that any kind of semantic information about the past or present state of execution may not be discernible. To illustrate through a naive example, could one be able to detect that a buffer overflow attack has occurred just by looking at the cache-miss counters? Luckily, modern microprocessors usually maintain a host of different counters or records that have been shown to reflect program behavior fairly well [102]. Depending on the complexity of information sought, some form of heuristic post-processing of these data may be required though, thus requiring an offline software component (running on a separate core, for instance) to process the data and raise the alarm when necessary.

**Hardware Modifications.** Usually these solutions require very little hardware modifications, since the bulk of the logs are already present in the microarchitecture. Synthesizing this information may however require a small hardware component (in SCRAP [55], for instance), unless this task is offloaded to software [34, 87].

## CHAPTER 3

## Reviving Instruction Set Randomization with Polyglot

Instruction set randomization (ISR) was originally proposed as a countermeasure against code injection attacks. However, it is largely considered to have lost its relevance due to the pervasiveness of code-reuse techniques in modern attacks, against which ISR is fundamentally ineffective. Additoinally, code injection no longer remains a foundational component in contemporary exploits.

This chapter revisits the relevance of ISR in the current security landscape. We show that prior ISR schemes are ineffective against code injection, but can be made effective against codereuse attacks, and even counter state-of-the-art variants, such as "just-in-time" ROP (JIT-ROP). Yet, certain key architectural features are necessary for enabling these capabilities. We implement a new ISR system, namely Polyglot, on a SPARC32-based Leon3 FPGA that runs Linux. We show that our system incurs a low performance overhead (4.6% on a subset of SPEC CINT2006) and defends against real-world (JIT-)ROP exploits, while still supporting critical features like page sharing. Polyglot is also the first ISR implementation to be applicable to the entire software stack: from the bootloader to user applications.

#### 3.1 Introduction

Instruction set randomization (ISR) was proposed as a way of mitigating code injection attacks [7, 56]. Specifically, ISR involves *randomizing* the underlying instruction-set architecture (ISA) of a CPU, thereby giving the appearance of a unique instruction set to every program. For instance, the opcode 0xa may denote XOR on one machine, but may be invalid on another. This prevents an unauthorized party (attacker) from using the *same* exploit on multiple targets—any injected (shell)code must adhere to the unique ISA used by the vulnerable program to be effective.

ISR implementations typically "emulate" the random ISA using a layer of encryption. Code is encrypted at the binary level and decrypted on-memory, right before execution. Apart from ASIST [88], the only hardware-based ISR scheme to date, all previous solutions [7, 16, 51, 56, 95] are software-based and primarily utilize dynamic binary instrumentation frameworks, like Pin [71]. This method for generating diversity is far simpler than customizing the decoder on each chip to implement random instruction mappings or changing the microarchitecture of every CPU instance.

However, ISR has a major drawback that impedes its widespread adoption—it is completely ineffective against code-reuse attacks, which is the typical cornerstone of modern exploits [21, 89, 90, 101]. This is because code-reuse attacks, as the term implies, stitch together legitimate code pieces, already present in the address space of a running process. Additionally, as we show later, once an attacker has the means to overcome techniques like W⊕X, ISR can be trivially bypassed as well. Hence, even as a defense against code injection, ISR is no more effective than other established techniques.

Aside from this fundamental limitation, all the previously-proposed ISR schemes also suffer from one, or more, of the following major issues:

- ① Unfavorable performance–security trade-offs. Since instructions are decrypted at runtime, the decryption process falls squarely in the critical path of instruction execution and the associated latency is hard to amortize. Hence, weak encryption schemes are traditionally used to offset this overhead, resulting in new attacks [109, 124].

- 2 No self-protection. Since most previous solutions are software-based, they: (a) expose a

Figure 3.1: High-level overview of Polyglot.

large trusted computing base (TCB), and (b) can be turned off easily, because the enabling framework executes at the same privilege level with the protected application(s).

- 3 **Incongruent with modern software systems.** Previous schemes provide limited or no support for shared libraries and page sharing. Hence, they are impractical in modern settings, as they incur large memory overheads [6].

- 4 Archaic threat model. Previous approaches do not consider memory disclosure vulnerabilities as part of their threat model. Yet, arbitrary memory reads are a standard component in recent work in the area [5, 29, 33, 46, 106], and quite popular to present-day attacks.

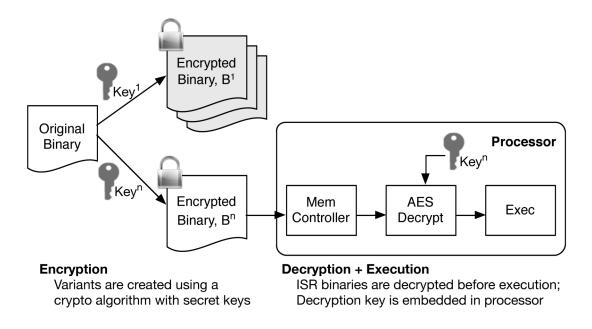

In this work, we propose *Polyglot*, a hardware-based ISR scheme that concurrently addresses all the above concerns. Polyglot not only improves significantly the traditional security properties of ISR, but also counters state-of-the-art code-reuse attacks, which are a novel and more relevant target for this technique. We utilize strong encryption (AES [110] and ECC), successfully overcoming the challenges of impractical performance *by removing decryption from the critical path* with microarchitectural optimizations. We present two schemes: (a) one with no overhead in practical systems, catering to the standard threat model used in anti code-reuse-attacks proposals; and

(b) another with nominal overhead to counter a stronger threat model. Unlike most prior work, we encrypt at the *page*, instead of application, granularity. This not only enables richer diversification, but also allows us to trivially support page sharing and seamlessly apply ISR to the system software (OS, hypervisor, etc.). We are also the first to show how ISR functionality can be logically extended to operate from system boot time, when the memory management unit (MMU), and hence paging, is disabled. Consequently, our implementation of ISR is available from the very first instruction that the system executes.

Figure 3.1 provides an overview of Polyglot. Binaries are encrypted page-wise with AES, while upon execution, the hardware memory controller (with the help of the OS) decrypts the executing instructions as they are transferred into the cache, so that the program remains encrypted in memory. We elaborate on the rationale and motivation of such a design in next section.

In summary, this work makes the following contributions:

- We propose Polyglot, a hardware-assisted ISR implementation, and demonstrate for the first time that it can be used as a defense not only against code injection, but also against (static or dynamic) code-reuse attacks (CRAs) that are a more critical extant threat. In addition, we show how prior proposals fail to fit into this role.

- We overcome the security-performance tradeoffs exhibited by previous ISR proposals, and illustrate how Polyglot can be performant despite using strong cryptographic schemes.

- We uphold the principles of scalable software design by supporting shared libraries and page sharing.

- We implement a SPARC32-based prototype, based on the Leon3 open-source SoC package [66], which allows us to study and demonstrate the full-system viability of our proposal.

This enables us to practically evaluate the system from a performance and security stand-point.

# 3.2 Background and Motivation

In this section, we give a brief overview of previous work on ISR, and claim that in the face of modern exploitation techniques, ISR is completely ineffective. Subsequently, we motivate a novel way in which ISR can become valuable again, when combined with other protection mechanisms, albeit only if strong encryption is employed.

#### 3.2.1 Previous ISR Schemes

| Proposal                    | HW<br>Based | Encryp-<br>tion  | Granu-<br>larity | Shared<br>Libs* | Code<br>Shar-<br>ing | Self-<br>modifying<br>Code | Scope                               | Slow-<br>down |

|-----------------------------|-------------|------------------|------------------|-----------------|----------------------|----------------------------|-------------------------------------|---------------|

| Barrantes et al. [7]        | Х           | XOR              | Proc.            | Х               | Х                    | Х                          | App.                                | High          |

| Kc et al. [56]              | Х           | XOR              | Proc.            | Х               | Х                    | Х                          | App.                                | High          |

| Hu et al. [51]              | X           | AES              | Proc.            | Х               | Х                    | Х                          | App.                                | High          |

| Boyd et al. [16]            | X           | XOR              | Proc.            | Х               | Х                    | Х                          | App.                                | Med.          |

| Portokalidis et al. [95]    | X           | XOR              | Proc.            | ✓               | ✓                    | ✓                          | App.                                | Med.          |

| Papadogiannakis et al. [88] | 1           | XOR,<br>Trans/on | Proc.,<br>Kernel | 1               | Х                    | 1                          | App.,<br>Kernel                     | Negl.         |

| Polyglot                    | <b>√</b>    | AES,<br>ECC      | Mem.<br>page     | 1               | 1                    | 1                          | App.,<br>Kernel,<br>Boot-<br>loader | Low           |

Table 3.1: Comparison of various ISR proposals. (\*Shared library support does not necessarily imply sharing them across processes, unless code sharing is allowed.)

Most prior ISR attempts are software based (see Table 3.1), and typically implement randomization using dynamic binary instrumentation tools, such as Pin [71], or platform emulators, like Bochs [64]. Obviously, an attacker can turn off, or subvert, such components as they execute at the same privilege level as the protected application. Apart from other practicality issues, they also exhibit significant slowdowns [95] and were demonstrated to be bypassable [109, 124], due to their use of weak XOR-based encryption.

ASIST [88] sidesteps problems with performance and (the lack of support for) shared libraries by providing hardware support for ISR, and incorporates the best practices of most of the previous techniques. ASIST allows two types of weak encryption: XOR and transposition. The encryption

keys are unique to every process, and can be generated either at compile time, in which case the application statically links with all its dependencies, or at load time, where the pages are encrypted dynamically. The latter mode allows shared libraries, but does not allow sharing them between applications, thus incurring a significant (memory) overhead [6]. Absence of page sharing also precludes the copy-on-write primitive, significantly increasing the overhead of fork.

### 3.2.2 ISR against Code-Reuse Attacks

Code-reuse techniques are the attackers' response to the increased adoption of hardening mechanisms, like non-executable memory (NX), in commodity systems. The main idea behind codereuse is to construct the malicious payload by reusing instructions already present in the address space of a vulnerable process [101]. This powerful technique gives the attacker the same level of flexibility offered by arbitrary code injection, without injecting any new code at all; the malicious payload consists of just a sequence of *gadget* addresses intermixed with any necessary data arguments.

ISR is *fundamentally* ineffective against code-reuse attacks (CRAs), since attackers can construct their payload without knowing how the instructions have been scrambled. One only needs to know the *location* of the appropriate gadgets.

In the presence of various code-randomization schemes [63], state-of-the-art CRAs have been evolved to discover gadgets dynamically, at runtime, by scanning code pages [106]. To prevent this, two conditions have to be met:

- 1 The host binary should differ from the attacker's copy.

- 2 Code should not be readable.

These two conditions are sufficient, as an attacker can neither scan binaries at the host, nor use their own copy in conjunction with the diversified copy to mount a CRA. (Note that this does not rule out data-only attacks [19].)

To this end, we propose combining ISR with a fine-grained (code) randomization scheme to thwart state-of-the-art CRAs. While the latter satisfies condition (1) an ideal ISR implementation

can also *indirectly* prevent condition ② by revealing (ideally irreversible) encrypted text when code is read.

However, if ISR, plus diversification, is all that is needed, can we just combine code randomization with any of the previous ISR proposals? In other words, can we use ISR based on weak encryption to fulfill the above conditions? Unfortunately, encryption schemes such as XOR and bit transposition can be easily bypassed, even under the presence of fine-grained diversification; during our preliminary experiments we were able to leak keys for the two schemes easily, using entirely architecture- and ABI-independent methods (we elaborate more in Section 3.6.1). Hence, we argue that using stronger encryption, at low cost, is *pivotal* in providing effective ISR-based protection.

### 3.3 Adversarial Model

We assume that the chip manufacturer is trusted and the attacker is incapable of physically probing the contents of the chip. We also assume that the processor supports some form of  $W \oplus X$  mechanism (e.g., NX bit). In addition, the OS and the essential system components are otherwise trusted to perform their duties faithfully. Note that side-channel attacks are considered out of scope. We present two versions of Polyglot in this work, which are geared towards two adversarial models.

• Adversarial Model A. Under this model, the adversary has access to the source code and/or a non-randomized version of the target program. She is aware of memory corruption bugs in it that can be exploited to gain arbitrary read and write capabilities. The same applies in the kernel setting, but the MMU-related structures are assumed to be protected with existing defenses [32, 122]. Lastly, the attacker also has the ability to carry out a finite number of brute force attacks before being detected. In this scenario, the first variant of Polyglot, namely Polyglot-A, seeks to protect against runtime code-reuse attacks.

This model is identical to previous studies regarding runtime CRAs [29, 46, 106], both offen-

sive and defensive, with the additional extension to the kernel.

• Adversarial Model B. Under this model, the adversary does not have access to the source code, but is more capable: she can subvert the OS, including the MMU structures, can access the randomized binary, and has physical access to the system allowing her to snoop/probe the buses, memory, and system peripherals other than the processor internals. In other words, we consider the processor to be the only component in our TCB.

This model clearly goes beyond CRAs and targets (static and dynamic) code leaks in general. In this case, Polyglot-B tries to prevent theft of application keys, and hence, plaintext code.

## 3.4 System Architecture

In this section, we present Polyglot's architectural design, detailing our software and hardware modifications, and how they inter-operate to achieve our goals.

#### 3.4.1 Software

**Binary Generation.** To create an "ISRized" binary, we symmetrically encrypt a diversified version of it, at page granularity, with randomly generated keys. (Note that only executable sections are encrypted.) These key-to-address mappings are then asymmetrically encrypted using the target processor's public key and packaged into the binary itself. Since code is encrypted at a page granularity, the executable, and its required shared libraries, possibly encrypted by different sources, are able to interoperate. Additionally, asymmetric encryption ties the binaries to their respective hosts.

**Binary Execution.** The dynamic loader and the OS are responsible for extracting the encrypted keys from ISRized binaries. In particular, the OS is in charge of them, during its execution lifetime, and for setting up the process' page tables, as well as its own, in a format expected by the hardware. (Note that our scheme allows code pages to exist in plaintext if necessary.) Additionally, since we encrypt at page-granularity, code sharing for shared libraries, as well as for forked processes, is

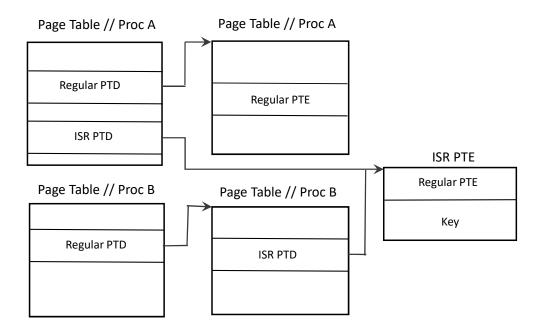

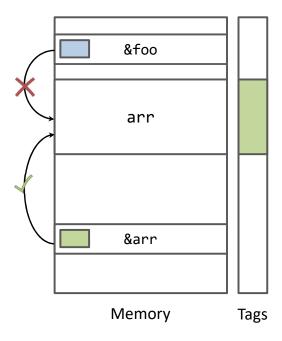

Figure 3.2: Modifications to page table. We use a reserved field in page-table value type field to indicate a subsequent ISR PTE. The ISR PTE here corresponds to a page shared between Processes A and B. PTD indicates a page table descriptor, which is a pointer to the next level, whereas PTE is the final translation.

readily supported, i.e., by using the same translation entry among the page tables of processes that share a particular page (see Figure 3.2).

Supporting ISR at the kernel level is achieved simply by changing the kernel's own page mapping(s) to an ISR-PTE version. Overall, our modifications added  $\sim 1100$  LOC to the Linux kernel (v3.8.1). Since paging is disabled at system boot, we randomize the bootloader by encrypting the whole image according to its layout in physical memory, so that encrypted execution is enabled from the very first instruction. Care is taken, however, to ensure that when the MMU is turned on, and paging enabled, the respective keys match (i.e., before and after enabling virtual addressing).

#### 3.4.2 Hardware

All previous ISR implementations suffer either from prohibitive slowdowns, weak security, or both. Polyglot however aims to overcome both, and proper hardware support plays a crucial role in this.

Given our threat model, we face quite a few challenges. Firstly, because the attacker can read and modify program memory and can probe system buses, we can allow decryption only inside the processor. But symmetric decryption has non-trivial latency. Adding it to the instruction-fetch critical path is not practical. In the same vein, the keys themselves cannot be stored in memory in plaintext and so, have to be decrypted inside the processor. Asymmetric decryption, however, has orders of magnitude higher latency than symmetric decryption. The main design challenge is thus to absorb or amortize these overheads as much as possible. Furthermore, secure key management being a key component of any encryption scheme, has to be considered at every step of the full-system design. For Polyglot-B, since our TCB is just the processor, we want code and keys to be encrypted at all times while outside the chip. Furthermore, it is preferable that these challenges be addressed with minimal changes in and as simple extensions of already-prevalent system architecture design. In our implementation, modifications mostly occur in the instruction page fault and instruction cache miss pathway.

#### **Instruction Page Fault.**

First we explain the basic changes required to enable the simpler version of Polyglot that does not require key-encryption, and then describe simple additions to this framework to support keyencryption.

Since keys are associated with every code page, it is convenient to fetch keys for a particular page while processing the corresponding fault. To do so, we require that last-level PTEs contain the translation as well as the associated key for code pages. The ISR PTE, thus, consists of the actual translation followed by the key for the page. To denote an ISR PTE we use a reserved value in the type field of a page-table value as shown in Figure 3.2.

Figure 3.3: ISR page fault handling flowchart.

An interesting design challenge now is that since ISR PTEs are longer than a word and do not otherwise conform to a power-of-two alignment, the traditional method of offset-based PTE fetching does not work. We solved this by extending the original page walk scheme by one more level of indirection. Instead of storing the physical address of another table to offset into, we store the physical address of the ISR PTE entry itself at the penultimate level. This design allows the OS to arrange these entries in whichever way it deems convenient – either as a contiguous table, or as discrete entries in memory. The hardware page-walk scheme is agnostic to this organization.