Hardware-Software Co-design for Practical Memory Safety

Mohamed Tarek Bnziad Mohamed Hassan

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences

**COLUMBIA UNIVERSITY**

#### © 2022

Mohamed Tarek Bnziad Mohamed Hassan All Rights Reserved

#### Abstract

# Hardware-Software Co-design for Practical Memory Safety Mohamed Tarek Bnziad Mohamed Hassan

A vast amount of software, from low-level systems code to high-performance applications, is written in memory-unsafe languages such as C and C++. The lack of memory safety in C/C++ can lead to severe consequences; a simple buffer overflow can result in code or data corruption anywhere in the program memory [1]. The problem is even worse in systems that constantly operate on inputs of unknown trustworthiness. For example, in 2021 a memory safety vulnerability was discovered in sudo, a near-ubiquitous utility available on major Unix-like operating systems [2]. The vulnerability, which remained silent for over 10 years, allows any unprivileged user to gain root privileges on a victim machine using a default sudo configuration. As memory-safe languages are unlikely to displace C/C++ in the near future, efficient memory safety mechanisms for both existing and future C/C++ code are needed.

Both industry and academia have proposed various techniques to address the C/C++ memory safety problem over the last three decades, either by software-only or hardware-assisted solutions. Software-only techniques such as Google's AddressSanitizer [3] are used to detect memory errors during the testing phase before products are shipped. While sanitizers have been shown to be effective at detecting memory errors with little effort, they typically suffer from high runtime overheads and increased memory footprint. Hardware-assisted solutions such as Oracle's Application Data Integrity (ADI) [4] and ARM's Memory Tagging Extension (MTE) [5] have much lower performance overheads, but they do not offer complete protection. Academic proposals manage to

minimize the performance costs of memory safety defenses while maintaining fine-grained security protection. Unfortunately, state-of-the-art solutions require complex metadata that increases the program memory footprint, complicates the hardware design, and breaks compatibility with the rest of the system (e.g., unprotected libraries).

To address these problems, the research within this thesis innovates in the realm of compiler transformations and hardware extensions to improve the state of the art in memory safety solutions. Specifically, this thesis shows that *leveraging common software trends and rethinking computer microarchitectures can efficiently circumvent the problems of traditional memory safety solutions for C and C++.* First, I present a novel cache line formatting technique, dubbed Califorms [6]. Califorms builds on a concept called memory blocklisting, which prohibits a program from accessing certain memory regions based on program semantics. State-of-the-art hardware-assisted memory blocklisting, while much faster than software blocklisting, creates memory fragmentation for each use of the blocklisted location. To prevent this issue, Califorms encodes the metadata, which is used to identify the blocklisted locations, in the blocklisted (i.e., dead) locations themselves. This inlined metadata can be then integrated into the microarchitecture by changing the cache line format. As a result, both the metadata and data are fetched together, eliminating the need for extra memory accesses. Hence, Califorms reduces the performance overheads of memory safety while providing byte-granular protection and maintaining very low hardware overheads.

Secondly, I explore how leveraging common software trends can reduce the performance and memory costs of memory permitlisting (also known as base & bounds). Thus, I present No-FAT [7], a novel technique for enforcing spatial and temporal memory safety. The key observation that enables No-FAT is the increasing adoption of binning allocators. No-FAT, when used with a binning allocator, is able to *implicitly* derive an allocation's bounds information (i.e., the base address and size) from the pointer itself without relying on expensive metadata. Moreover, as No-FAT's memory instructions are aware of allocation bounds information, No-FAT effectively mitigates certain speculative attacks (e.g., Spectre-V1, which is also known as bounds checking bypass) with no additional cost. While No-FAT successfully detects memory safety violations, it falls

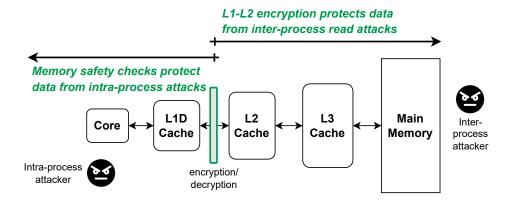

short against physical attacks. Hence, I propose C-5 [8], an architecture that complements No-FAT with strong data encryption. C-5 strictly uses access control in the L1 cache and encrypts program data at the L1-L2 cache interface. As a result, C-5 mitigates both in-process and physical attacks without burdening system performance.

In addition to memory blocklisting and permitlisting, a cost-effective way to alleviate the memory safety threats is by deploying exploit mitigation techniques (e.g., Intel's CET [9] and ARM's PAC [10]). Unfortunately, current exploit mitigations offer incomplete security protection in order to save on performance. This thesis investigates potential opportunities to boost the security guarantees of exploit mitigations while maintaining their low overheads. Thus, I present ZeRØ [11], a hardware primitive that preserves pointer integrity at no performance cost, effectively mitigating pointer manipulation attacks such as ROP, COP, JOP, COOP, and DOP. ZeRØ proposes unique memory instructions and a novel metadata encoding scheme to protect code and data pointers from memory safety violations. The combination of instructions and metadata allows ZeRØ to avoid explicitly tagging every word in memory. On 64-bit systems, ZeRØ encodes the pointer type and location in the currently unused upper pointer bits. This way ZeRØ reduces the performance overheads of enforcing pointer integrity to zero while requiring simple hardware modifications.

Finally, although current mitigation techniques excel at providing efficient protection for highend devices, they typically suffer from significant performance and energy overheads when ported to the embedded domain. As a result, there is a need for developing new defenses that (1) have low overheads, (2) provide high security coverage, and (3) are especially designed for embedded devices. To achieve these goals I present EPI, an efficient pointer integrity mechanism that is tailored to microcontrollers and embedded devices [12]. Similar to ZeRØ, EPI assigns unique tags to different program assets and uses unique memory instructions for accessing them. However, EPI uses a 32-bit friendly encoding scheme to inline the tags within the program data. EPI introduces runtime overheads of less than 1%, making it viable for embedded and low-resource systems.

### **Table of Contents**

| List of F | igures . | vii                                               |

|-----------|----------|---------------------------------------------------|

| List of T | Tables . | iz                                                |

| Abbrevi   | ations . |                                                   |

| Publicat  | ions     | x                                                 |

| Acknow    | ledgme   | ntsxii                                            |

| Dedicati  | ion      | xv                                                |

| Preface   |          | xv                                                |

| I Int     | roduct   | zion 1                                            |

| Chapter   | 1: Intr  | oduction                                          |

| 1.1       | What I   | s Memory Safety?                                  |

| 1.2       | Why Is   | S Memory Safety Still A Concern?                  |

|           | 1.2.1    | Memory-Safe Languages                             |

|           | 1.2.2    | Testing & Verification                            |

|           | 1.2.3    | Hardware-Based Mitigations                        |

| 1.3       | Why A    | are Current Hardware-Based Solutions Impractical? |

| 1.4       | •        | Statement & Contributions                         |

|           | 1.4.1    | Califorms                                         |

|           | 1.4.2    | No-FAT                                            |

|           | 1.4.3    | C-5                                               |

|           | 1.4.4    | ZeRØ                                              |

|           | 1.4.5    | EPI 11                                            |

| 1.5       | Thesis   | Organization                                      |

| Chanter   | 2. Rac   | ok ground                                         |

| 2.1  | Progra | Im Components                                               |

|------|--------|-------------------------------------------------------------|

|      | 2.1.1  | Code                                                        |

|      | 2.1.2  | Globals                                                     |

|      | 2.1.3  | Stack                                                       |

|      | 2.1.4  | Heap                                                        |

| 2.2  | Memo   | ry Safety Definition                                        |

|      | 2.2.1  | Spatial Memory Safety                                       |

|      | 2.2.2  | Temporal Memory Safety                                      |

|      | 2.2.3  | Type Memory Safety                                          |

| 2.3  | Memo   | ry Safety Attacks                                           |

|      | 2.3.1  | Code Corruption                                             |

|      | 2.3.2  | Control-Flow Hijacking                                      |

|      | 2.3.3  | Data-Flow Hijacking                                         |

|      | 2.3.4  | Data Corruption                                             |

|      |        | •                                                           |

| II R | ethink | ing Microarchitectures For Efficient Memory Blocklisting 19 |

|      |        |                                                             |

| -    |        | che Line Formats                                            |

| 3.1  |        | ation                                                       |

| 3.2  |        | n Overview                                                  |

| 3.3  |        | ecture Support                                              |

|      | 3.3.1  | BLOC Instruction                                            |

|      | 3.3.2  | Privileged Exceptions                                       |

| 3.4  | Micro  | architecture Design                                         |

|      | 3.4.1  | L1 Cache: Bit Vector Approach                               |

|      | 3.4.2  | L2 Cache and Beyond: Sentinel Approach                      |

|      | 3.4.3  | L1 to/from L2 Califorms Conversion                          |

|      | 3.4.4  | Load/Store Queue Modifications                              |

| 3.5  | Softwa | are Design                                                  |

|      | 3.5.1  | Dynamic Memory Management                                   |

|      | 3.5.2  | Compiler Support                                            |

|      | 3.5.3  | Operating System Support                                    |

| 3.6  | Securi | ty Analysis                                                 |

|      | 3.6.1  | Threat Model                                                |

|      | 3.6.2  | Hardware Attacks and Mitigations                            |

|      | 3.6.3  | Software Attacks and Mitigations                            |

| 3.7              | Evalua | ation                                                           | 39 |

|------------------|--------|-----------------------------------------------------------------|----|

|                  | 3.7.1  | Hardware Overheads                                              | 39 |

|                  | 3.7.2  | Software Performance Overheads                                  | 41 |

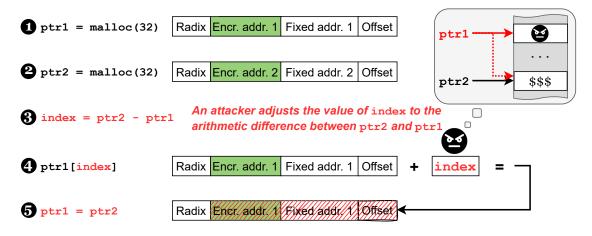

| 3.8              | Summ   | ary                                                             | 44 |

| III I<br>mitlist |        | ging Current Software Trends For Efficient Memory Per-          | 46 |

| Chapter          | 4: Arc | chitectural Support for Low Overhead Memory Safety Checks       | 47 |

| 4.1              | Motiva | ation                                                           | 48 |

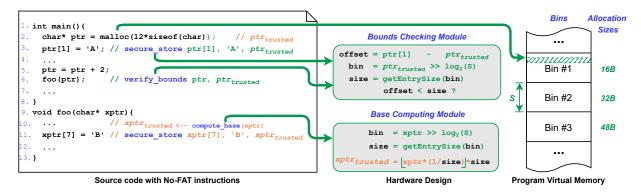

| 4.2              | Systen | n Overview                                                      | 49 |

|                  | 4.2.1  | Preliminaries                                                   | 49 |

|                  | 4.2.2  | How does No-FAT provide Inter-allocation Spatial Memory Safety? | 50 |

|                  | 4.2.3  | How does No-FAT provide Intra-allocation Spatial Memory Safety? | 52 |

|                  | 4.2.4  | How does No-FAT provide Temporal Memory Safety?                 | 53 |

|                  | 4.2.5  | Handling Procedure Calls and Nested Pointers                    | 54 |

| 4.3              | Archit | ecture Support                                                  | 56 |

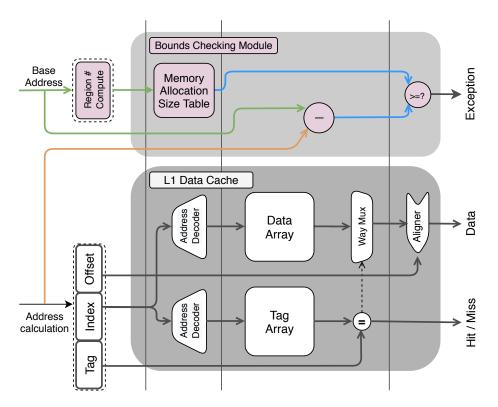

| 4.4              | Micro  | architecture Design                                             | 57 |

|                  | 4.4.1  | MAST                                                            | 57 |

|                  | 4.4.2  | Bounds Checking Module                                          | 57 |

|                  | 4.4.3  | Base Computing Module                                           | 58 |

|                  | 4.4.4  | Dedicated Register File                                         | 59 |

| 4.5              | Softwa | are Design                                                      | 59 |

|                  | 4.5.1  | Dynamic Memory Management                                       | 59 |

|                  | 4.5.2  | Compiler Support                                                | 60 |

|                  | 4.5.3  | Operating System Support                                        | 61 |

| 4.6              | Securi | ty Analysis                                                     | 61 |

|                  | 4.6.1  | Threat Model                                                    |    |

|                  | 4.6.2  | Security Discussion                                             |    |

|                  | 4.6.3  | Spectre-V1 Resiliency                                           | 64 |

|                  | 4.6.4  | Deployment Considerations                                       |    |

| 4.7              | Evalua | ntion                                                           |    |

|                  | 4.7.1  | Hardware Overheads                                              |    |

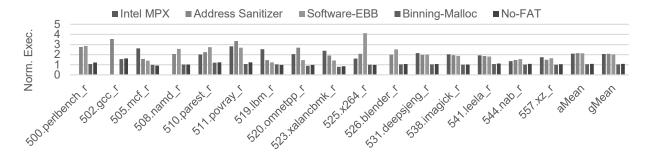

|                  | 4.7.2  | Software Performance Overheads                                  | 69 |

|                  | 4.7.3  | Software Memory Overheads                                       | 71 |

|                  | 4.7.4  | Temporal Memory Safety Analysis                                 | 72 |

|        | 4.7.5     | Buf2Ptr Analysis                                                        | 73  |

|--------|-----------|-------------------------------------------------------------------------|-----|

| 4.8    | Summ      | nary                                                                    | 74  |

| Chapte | er 5: A ( | Counter C-4 Architecture                                                | 75  |

| 5.1    | Motiva    | ation                                                                   | 76  |

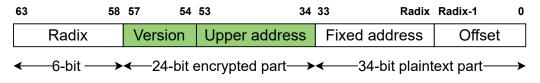

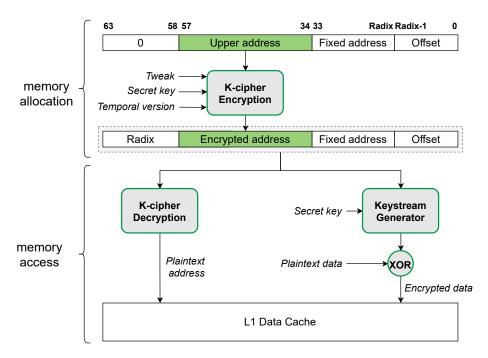

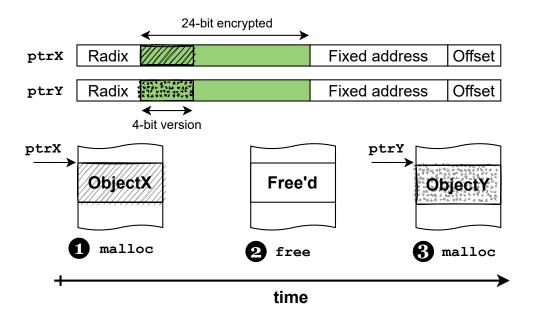

| 5.2    | How I     | Does Cryptographic Capability Computing (C <sup>3</sup> ) work?         | 76  |

|        | 5.2.1     | The Object Life-cycle in $\mathbb{C}^3$                                 | 77  |

|        | 5.2.2     | C <sup>3</sup> 's Design Choices                                        | 79  |

|        | 5.2.3     | Threat Model                                                            | 79  |

| 5.3    | C-4: A    | Assessing the Security Guarantees of Cryptographic Capability Computing | 80  |

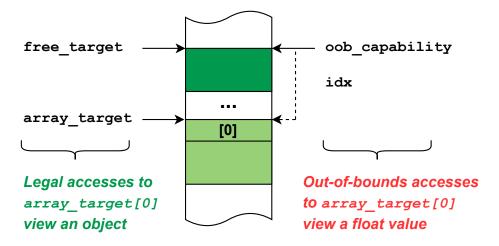

|        | 5.3.1     | Attack #1: Exploiting the XOR-based Data Encryption                     | 80  |

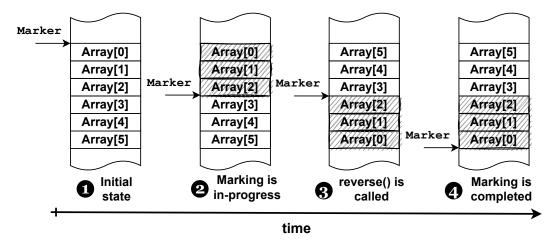

|        | 5.3.2     | Attack #2: Targeting Spatial Memory Safety                              | 82  |

|        | 5.3.3     | Attack #3: Undermining Temporal Memory Safety                           | 84  |

|        | 5.3.4     | Attack #4: Understanding the Security Coverage                          | 86  |

| 5.4    | End-to    | o-End Case Study                                                        | 87  |

|        | 5.4.1     | Vulnerability Description                                               | 87  |

|        | 5.4.2     | Baseline Exploitation Methodology                                       |     |

|        | 5.4.3     | C <sup>3</sup> Exploitation Challenges & C-4 Countermeasures            | 91  |

|        | 5.4.4     | Additional Real-World Exploits                                          | 93  |

| 5.5    | C-5: A    | A Counter C-4 Architecture                                              | 93  |

|        | 5.5.1     | Security Enhancements                                                   | 94  |

|        | 5.5.2     | Performance Optimizations                                               | 97  |

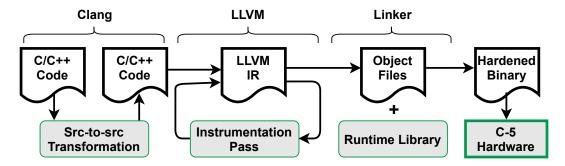

|        | 5.5.3     | C-5 Implementation                                                      | 99  |

| 5.6    | Securi    | ity Analysis                                                            | 100 |

|        | 5.6.1     | Addressing Traditional Memory Safety Violations                         | 100 |

|        | 5.6.2     | Mitigating Physical Attacks                                             | 101 |

|        | 5.6.3     | Mitigating The C-4 Attacks                                              | 102 |

|        | 5.6.4     | Preventing the end-to-end exploit                                       | 102 |

|        | 5.6.5     | Limitations                                                             | 103 |

| 5.7    | Evalua    | ation                                                                   | 103 |

|        | 5.7.1     | Evaluation Methodology                                                  | 103 |

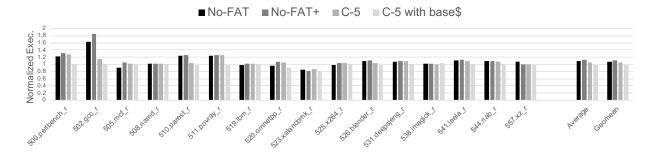

|        | 5.7.2     | SPEC CPU2017 Performance Evaluation                                     | 104 |

|        | 5.7.3     | Real-world Case Studies                                                 |     |

|        | 5.7.4     | Security Evaluation                                                     | 109 |

| 5.8    | Summ      | narv                                                                    | 110 |

| IV       | Effic  | cient | t Exploit Mitigations For Servers & Embedded Systems           | 112   |

|----------|--------|-------|----------------------------------------------------------------|-------|

| Chap     | ter 6: | Zero  | o-Overhead Resilient Operation Under Pointer Integrity Attacks | . 113 |

| 6.       | 1 M    | otiva | tion                                                           | . 114 |

| 6.       | .2 Sy  | stem  | Overview                                                       | . 114 |

|          | 6.2    | 2.1   | How Does ZeRØ Work?                                            | . 115 |

|          | 6.2    | 2.2   | Main Components                                                | . 116 |

| 6.       | .3 Ar  | chite | ecture Support                                                 | . 117 |

| 6.       | 4 M    | icroa | rchitecture Design                                             | . 119 |

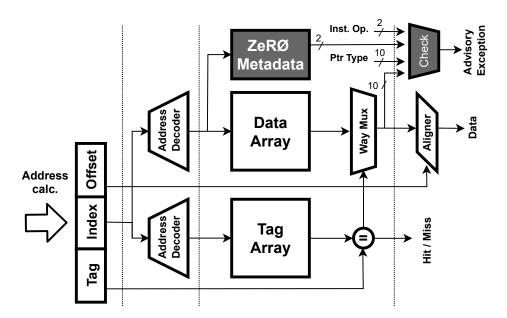

|          | 6.4    | 4.1   | L1 Data Cache Modifications                                    | . 119 |

|          | 6.4    | 4.2   | Exception Handling Circuitry                                   | . 121 |

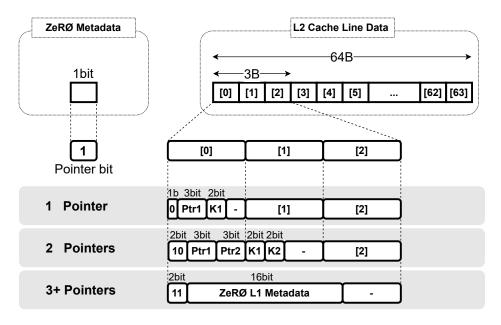

|          | 6.4    | 4.3   | L2/L3 Cache Modifications                                      | . 122 |

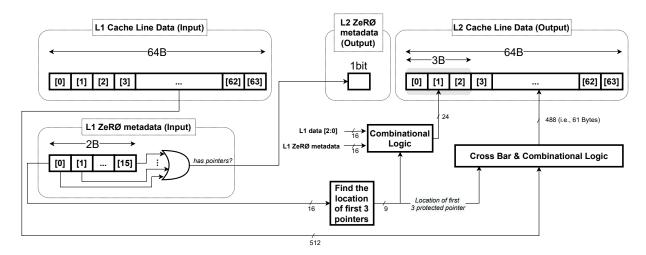

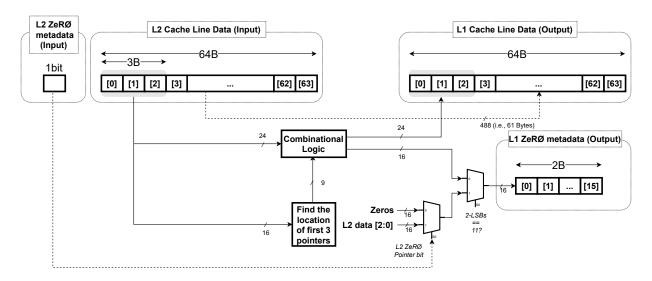

|          | 6.4    | 4.4   | L1 to/from L2 Transformation Module                            | . 123 |

|          | 6.4    | 4.5   | Load/Store Queue Modifications                                 | . 124 |

| 6.       | .5 So  | oftwa | re Design                                                      | . 125 |

|          | 6.5    | 5.1   | Memory Management                                              | . 125 |

|          | 6.5    | 5.2   | Compiler Support                                               | . 126 |

|          | 6.5    | 5.3   | Operating System Support                                       | . 126 |

| 6.       | .6 Se  | curit | y Analysis                                                     | . 128 |

|          | 6.6    | 5.1   | Threat Model                                                   | . 128 |

|          | 6.6    | 5.2   | Security Discussion                                            | . 129 |

|          | 6.6    | 5.3   | Limitations                                                    | . 131 |

| 6.       | .7 Ev  | aluat | tion                                                           | . 133 |

|          | 6.7    | 7.1   | Hardware Measurements                                          | . 133 |

|          |        | 7.2   | Software Performance                                           |       |

|          | 6.7    | 7.3   | Comparison with Prior Work                                     | . 135 |

| 6.       | .8 Su  | ımma  | ury                                                            | . 136 |

| Chan     | ter 7· | Effi  | cient Pointer Integrity For Securing Embedded Systems          | 138   |

| 7.       |        |       | tion                                                           |       |

| 7.<br>7. |        |       | Overview                                                       |       |

| , •      | 7.2    |       | Function Pointer Integrity                                     |       |

|          |        | 2.2   | Data Pointer Integrity                                         |       |

|          | 7.2    |       |                                                                |       |

|          |        |       | Return Address Integrity                                       |       |

|          |        | 2.4   | Metadata Management                                            |       |

| _        | 7.2    |       | Putting It All Together                                        |       |

| 7.       | .3 M:  | ıcroa | rchitecture Design                                             | . 145 |

|                   | 7.3.1  | Processor Modifications        | . 145      |

|-------------------|--------|--------------------------------|------------|

|                   | 7.3.2  | Memory Hierarchy Modifications | . 145      |

| 7.4               | Softwa | are Design                     | . 149      |

|                   | 7.4.1  | Software Properties            | . 149      |

|                   | 7.4.2  | Compiler Support               | . 152      |

|                   | 7.4.3  | Operating System Support       | . 152      |

| 7.5               | Securi | ity Analysis                   | . 153      |

|                   | 7.5.1  | Threat Model                   | . 154      |

|                   | 7.5.2  | Security Discussion            | . 154      |

|                   | 7.5.3  | Limitations                    | . 156      |

| 7.6               | Evalua | ation                          | . 156      |

|                   | 7.6.1  | Experimental Setup             | . 157      |

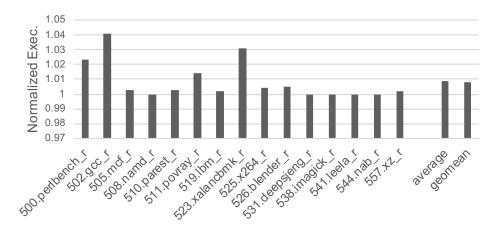

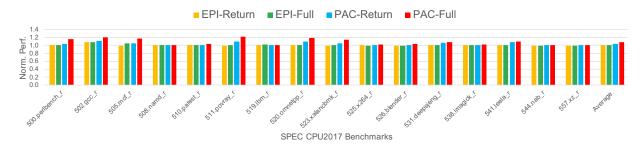

|                   | 7.6.2  | Performance Results            | . 157      |

|                   | 7.6.3  | Comparison with ARM's PAC      | . 158      |

|                   | 7.6.4  | Hardware Overheads             | . 159      |

| 7.7               | Summ   | nary                           | . 160      |

| ory Sa<br>Chapter | •      | elated Work                    | <b>161</b> |

| _                 |        |                                |            |

| 8.1               |        | ory Safety Error Detection     |            |

|                   | 8.1.1  | Memory Blocklisting            |            |

|                   | 8.1.2  | Memory Tagging                 |            |

|                   | 8.1.3  | Memory Permitlisting           |            |

| 8.2               |        | ory Safety Exploit Mitigation  |            |

|                   | 8.2.1  | Shadow Stack-Based Techniques  |            |

|                   | 8.2.2  | Encryption-Based Techniques    | . 170      |

| VI (              | Conclu | ısion                          | 172        |

|                   |        | onclusion                      | . 173      |

| - 1               | 9.0.1  | Advancing Memory Blocklisting  |            |

|                   | 9.0.2  | Advancing Memory Permitlisting |            |

|                   | 9.0.3  | Advancing Exploit Mitigation   |            |

|                   |        |                                |            |

| Referen           | CAC    |                                | 176        |

## **List of Figures**

| 1.1  | Timeline for memory safety exploitation techniques and mitigations                | 3  |

|------|-----------------------------------------------------------------------------------|----|

| 2.1  | The main components of a program's address space                                  | 13 |

| 2.2  | Memory corruption root causes, targets, and end results                           | 15 |

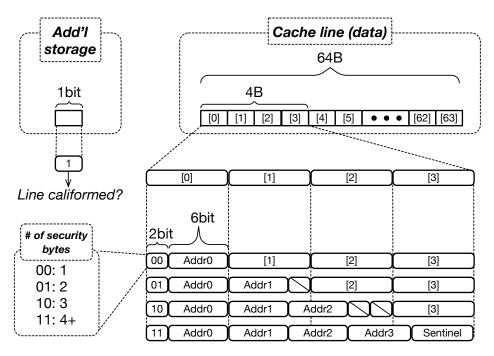

| 3.1  | A high level overview of how Califorms works                                      | 21 |

| 3.2  | Califorms Insertion Polices                                                       | 22 |

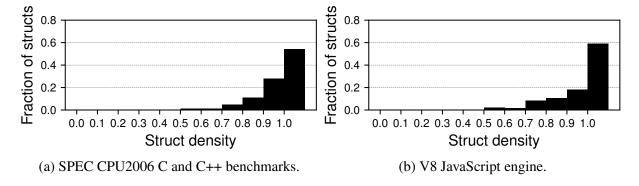

| 3.3  | Struct density histogram of SPEC CPU2006 benchmarks and the V8 engine             | 23 |

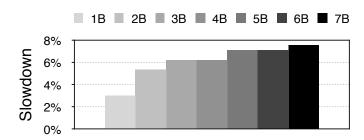

| 3.4  | Performance overhead with additional paddings for every field within structs      | 23 |

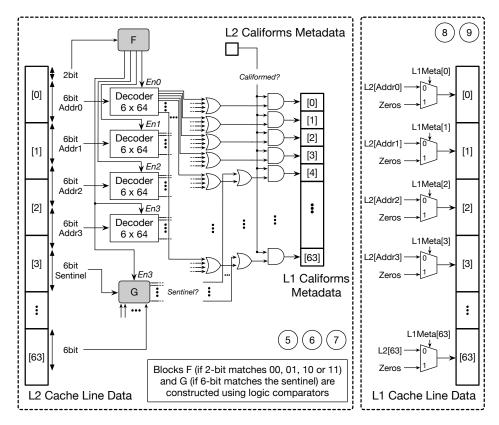

| 3.5  | Califorms-bitvector Format                                                        | 28 |

| 3.6  | Pipeline diagram for the L1 cache hit operation with Califorms                    | 28 |

| 3.7  | Califorms-sentinel Format.                                                        | 29 |

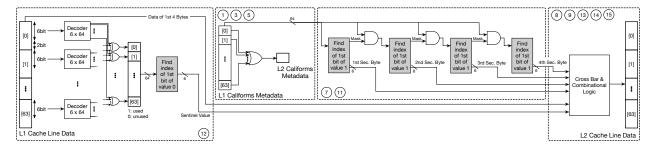

| 3.8  | Logic diagram for Califorms conversion from the L1 cache to L2 cache              | 29 |

| 3.9  | Logic diagram of Califorms conversion from the L2 cache to L1 cache               | 31 |

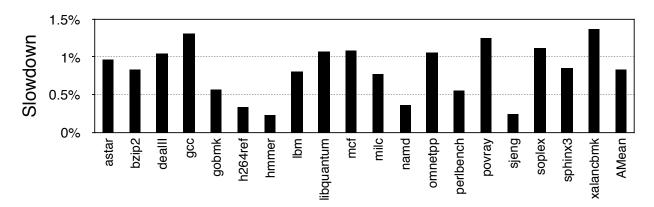

| 3.10 | Califorms slowdown with additional one-cycle access latency for L2 and L3 caches. | 41 |

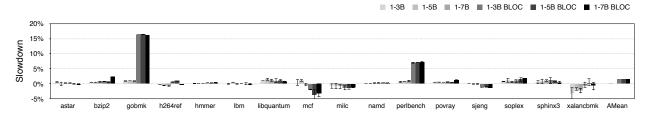

| 3.11 | Slowdown of the Califorms opportunistic policy and full insertion policy          | 43 |

| 3.12 | Slowdown of the Califorms intelligent insert policy                               | 43 |

| 4.1  | A high level overview of how No-FAT enforces spatial memory safety                | 52 |

| 4.2  | Pipeline diagram for the L1 cache hit operation with No-FAT                       | 58 |

| 4.3  | No-FAT performance overheads on the SPEC CPU2017 benchmarks                       | 71 |

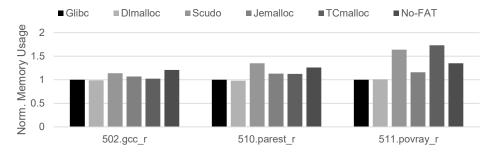

| 4.4  | Memory usage for different memory allocators                                      | 71 |

| 5.1  | The $C^3$ pointer format as proposed in the original paper                        | 77 |

| 5.2  | A high level overview of how $C^3$ works                                          | 78 |

|      |                                                                                   |    |

| 5.3  | Targeting $C^3$ 's spatial memory safety                                                  |

|------|-------------------------------------------------------------------------------------------|

| 5.4  | Undermining C <sup>3</sup> 's temporal memory safety                                      |

| 5.5  | A high-level overview of CVE-2018-4192                                                    |

| 5.6  | A visualization of how the addrof primitive works                                         |

| 5.7  | A high level overview of how C-5 works                                                    |

| 5.8  | C-5's temporal memory safety extension                                                    |

| 5.9  | C-5's implementation overview                                                             |

| 5.10 | Performance overheads for different No-FAT and C-5 variants                               |

| 5.11 | Slowdowns with additional 6-cycles access latency for the L2 cache for C-5 107            |

| 5.12 | Nginx performance evaluation with C-5                                                     |

| 5.13 | Duktape performance evaluation with C-5                                                   |

| 6.1  | A high level overview of how ZeRØ's pointer integrity mechanism works 115                 |

| 6.2  | ZeRØ's metadata encoding in the L1 data cache                                             |

| 6.3  | Pipeline diagram for the L1 cache hit operation with ZeRØ                                 |

| 6.4  | ZeRØ's metadata encoding in L2/L3 data cache and main memory                              |

| 6.5  | Block diagram of the ZeRØ's L1-to-L2 transformation module                                |

| 6.6  | Block diagram of the ZeRØ's L2-to-L1 transformation module                                |

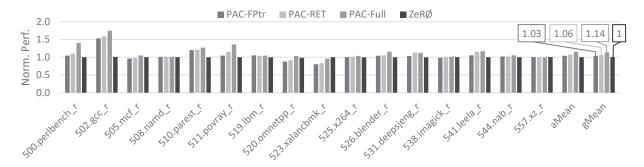

| 6.7  | Performance overheads of ZeRØ and three different ARM's PAC configurations 136 $^{\circ}$ |

| 7.1  | Embedded systems market trend from 2013 to 2019                                           |

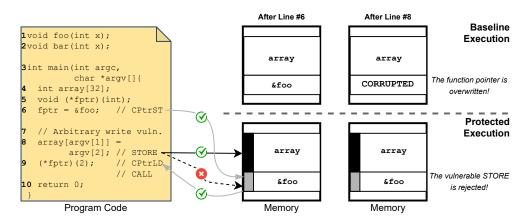

| 7.2  | A sample C application highlighting how EPI protects function pointers 141                |

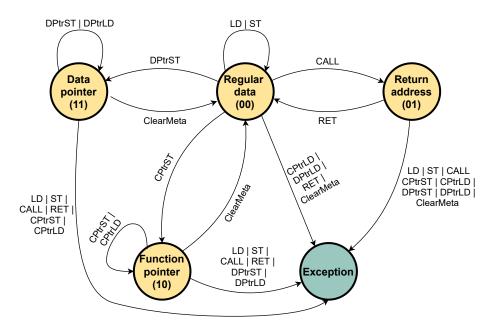

| 7.3  | Finite state machine of the different EPI metadata and instructions                       |

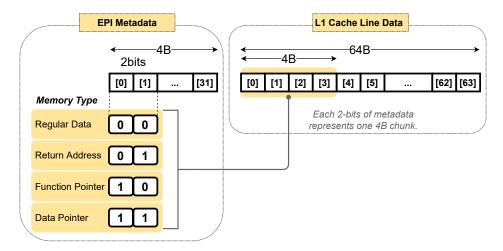

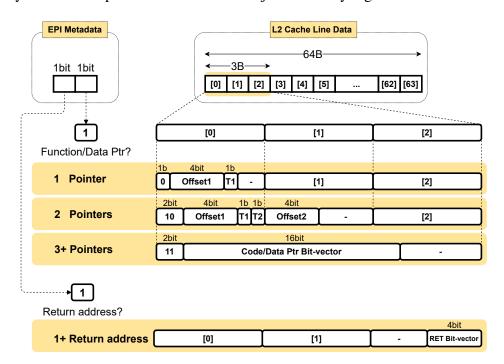

| 7.4  | EPI's metadata encoding in the L1 data cache on 32-bit architectures                      |

| 7.5  | EPI's metadata encoding in the L2 cache and main memory                                   |

| 7.6  | Different pointers layout on 32-bit architectures after applying EPI's optimizations. 151 |

| 7.7  | Performance overheads of the SPEC CPU2017 workloads for EPI and ARM's PAC. 158            |

### **List of Tables**

| 3.1 | BLOC instruction K-map                                                     |

|-----|----------------------------------------------------------------------------|

| 3.2 | Area, delay and power overheads of Califorms                               |

| 3.3 | Hardware configuration of the simulated system for Califorms               |

| 4.1 | Area, delay and power overheads of No-FAT                                  |

| 4.2 | Memory usage for SPEC CPU2017 benchmarks                                   |

| 4.3 | Configuration sizes per each bin in the No-FAT binning memory allocator 72 |

| 4.4 | Number of heap allocations that require extra padding bytes with No-FAT 73 |

| 5.1 | C-5's ISA extensions                                                       |

| 5.2 | C-5's base address cache sensitivity analysis                              |

| 5.3 | Simulation parameters for C-5 data encryption evaluation                   |

| 5.4 | RIPE Results Summary                                                       |

| 5.5 | Security Microbenchmarks Summary                                           |

| 6.1 | Actions taken on various instructions with ZeRØ                            |

| 6.2 | Area, delay and power overheads of ZeRØ                                    |

| 6.3 | Number of unique LLVM function and data pointer types                      |

| 8.1 | Categorization of prior work on spatial memory safety                      |

| 8.2 | Comparison with prior work on memory safety error detection                |

| 8.3 | Comparison with prior work on memory safety exploit mitigation             |

#### **Abbreviations**

**ARM PAC ARM Pointer Authentication**

**ARM MTE ARM Memory Tagging Extension**

ASan AddressSanitizer

BLOC Blocklisting Location

Buf2Ptr Buffer to Pointer

Cryptographic Capability Computing

C-4 Compromising Cryptographic Capability Computing

C-5 Counter C-4 Architecture

Califorms Cache Line Formats

Intel CET Intel Control-flow Enforcement Technology

CFI Control Flow Integrity

CFG Control Flow Graph

COP Call Oriented Programming

COOP Counterfeit Object Oriented Programming

CHERI Capability Hardware Enhanced RISC Instructions

CPtrST Code Pointer Store

CPtrLD Code Pointer Load

CRA Code Reuse Attack

CPI Code Pointer Integrity

DFI Data Flow Integrity

**DOP** Data Oriented Programming

DPtrST Data Pointer Store

DPtrLD Data Pointer Load

**EPI** Efficient Pointer Integrity

**GE** Gate Equivalent

Intel MPX Intel Memory Protection eXtension

JOP Jump Oriented Programming

MAST Memory Allocation Size Table

REST Random Embedded Secret Tokens

ROP Return Oriented Programming

SPARC ADI SPARC Application Data Integrity

UAF Use-After-Free

VLSI Very Large- Scale Integration

**Zero**-Overhead **Resilient Operation** Under Pointer Integrity Attacks

#### **Publications**

Parts of this thesis have been published earlier. The text in this thesis differs from the published versions in minor editorial changes that were made to improve readability. The following publications form the core of this thesis.

- Hiroshi Sasaki, Miguel A. Arroyo, Mohamed Tarek Ibn Ziad, Koustubha Bhat, Kanad Sinha, and Simha Sethumadhavan. "Practical Byte-Granular Memory Blacklisting using Califorms", In the Proceedings of the 52nd IEEE/ACM International Symposium on Microarchitecture (MICRO'52), Columbus, Ohio, USA, October 2019.

- Mohamed Tarek Ibn Ziad, Miguel A. Arroyo, Evgeny Manzhosov, Ryan Piersma, and Simha Sethumadhavan. "No-FAT: Architectural Support for Low Overhead Memory Safety Checks", *In the Proceedings of the 48th International Symposium on Computer Architecture (ISCA-48)*, Worldwide Event, June 2021.

- Mohamed Tarek Ibn Ziad, Miguel A. Arroyo, Evgeny Manzhosov, and Simha Sethumadhavan. "ZeRØ: Zero-Overhead Resilient Operation Under Pointer Integrity Attacks", In the Proceedings of the 48th International Symposium on Computer Architecture (ISCA-48), Worldwide Event, June 2021.

- Mohamed Tarek Ibn Ziad, Miguel A. Arroyo, Evgeny Manzhosov, Vasileios P. Kemerlis, and Simha Sethumadhavan. 'EPI: Efficient Pointer Integrity For Securing Embedded Systems", *In the Proceedings of the 2021 IEEE International Symposium on Secure and Private Execution Environment Design (SEED '21)*, Worldwide Event, September 2021.

- **Mohamed Tarek Ibn Ziad**, Evgeny Manzhosov, and Simha Sethumadhavan. "C-4: Compromising Cryptographic Capability Computing", *Currently under review*.

The following publications are not included in this thesis.

- Miguel A. Arroyo, **Mohamed Tarek Ibn Ziad**, Hidenori Kobayashi, Junfeng Yang, and Simha Sethumadhavan. "YOLO: Frequently Resetting Cyber-Physical Systems for Security", *In the Proceedings of the SPIE Defense and Commercial Sensing*, Baltimore, Maryland, USA, April 2019.

- Mohamed Tarek Ibn Ziad, Miguel A. Arroyo, Evgeny Manzhosov, Vasileios P. Kemerlis, and Simha Sethumadhavan. "Using Name Confusion to Enhance Security", *Technical Report*, arXiv: 1911.02038, August 2020.

- **Mohamed Tarek Ibn Ziad**, Miguel A. Arroyo, and Simha Sethumadhavan. "SPAM: Stateless Permutation of Application Memory", *Technical Report*, arXiv: 2007.13808, September 2020.

- Evgeny Manzhosov, Adam Hastings, Meghna Pancholi, Ryan Piersma, Mohamed Tarek

Ibn Ziad and Simha Sethumadhavan. "MUSE: Multi-Use Error Correction Codes", *Technical Report*, arXiv: 2107.09245, July 2021.

#### Acknowledgements

All praise belongs to Allah, Lord of all the worlds, the Gracious, the Merciful. I would like to thank God Almighty for bestowing upon me the chance, strength, and ability to complete this work. I want to take this opportunity to express my deep gratitude to the people who guided, helped, and encouraged me throughout my doctorate journey.

First, I am sincerely thankful to my advisor, Simha Sethumadhavan, for his kindness, guidance, and support over the past five years. Despite his many responsibilities, he was always available to answer my questions and dispel my concerns. I am grateful for all the technical and non-technical discussions we had together. I learned many lessons from him on both a professional and personal level. Thank you for teaching me how to be a true researcher.

During my time at Columbia University, I was fortunate to work with great colleagues, without whom none of my projects would have been completed. I would like to thank Miguel Arroyo for spending numerous days and nights working with me on building software infrastructures, debugging complex programs, and brainstorming new research ideas. I also thank Evgeny Manzhosov for helping me run microarchitectural simulations and create hardware prototypes. Additional thanks to my research collaborators—Hiroshi Sasaki, Kanad Sinha, Koustubha Bhat, Ryan Piersma, and Vasileios Kemerlis for contributing to my thesis publications. I also thank the past and the present members of the Computer Architecture and Security Technologies Lab (CASTL)—Adrian Tang, Yipeng Huang, Adam Hastings, Abhishek Shah, Meghna Pancholi, and Andreas Kellas for the interesting thoughts and rich discussions.

Over the past two summers, I was fortunate to have two (virtual) internships, in which I had the pleasure to interact with awesome folks in industry, present my work, receive thoughtful feedback, and get a taste of real-world challenges. I wish to thank my internship mentors from Qualcomm—Can Acar, Arvind Krishnaswamy, and Victor van der Veen for their help and support during Summer 2020. I also thank my NVIDIA mentors—Aamer Jaleel, Mark Stephenson, Michael Sullivan, and Steve Keckler for giving me the opportunity to apply my research work to GPUs and providing me with ultimate support during Summer 2021.

I would like to thank my committee members—Steven Bellovin, Martha Kim, Vasileios Kemerlis, and Santosh Nagarakatte for taking time from their busy schedule to participate in this dissertation. I would also like to thank Michael Sikorski, Suman Jana, Eleni Drinea, and Janet Kayfetz for teaching me great classes at Columbia University. Many thanks to Maria Joanta, Jessica Rosa, Cynthia Meekins, and the rest of the departmental staff at the CS department for helping me navigate the administrative matters smoothly. Thanks to Mohamed Watheq El-Kharashi, my first mentor at Ain Shams University, Egypt, for providing me with endless support during my undergraduate studies and inspiring me to pursue this career path.

Before all of that, I will always be grateful to my father Tarek Mohamed Hassan and my mother Nesrin Ahmed Radwan. Despite being more than 5,000 miles away from me, they have always been by my side throughput this PhD journey, sharing my successes and failures, and praying for me to shine. I would have never been in this place today without their love, support, and motivation. I am grateful for them forever. Finally, I am thankful to my soul mate and wife, Dina Abdulwahid, who traveled across the world to be with me. Thank you for caring so much for me. Your unconditional love is the fuel that keeps me going through all the struggles in my life.

To Mom & Dad and my wife, Dina.

#### **Preface**

This document is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences, Columbia University.

In this dissertation, I use "we" almost exclusively throughout as this work was accomplished in collaboration with many others, without whose help the work would not have been possible. In some cases, I use "I" whenever the text is derived from my own conclusions and explanations, which I am fully responsible for the content.

## Part I

## Introduction

#### **Chapter 1: Introduction**

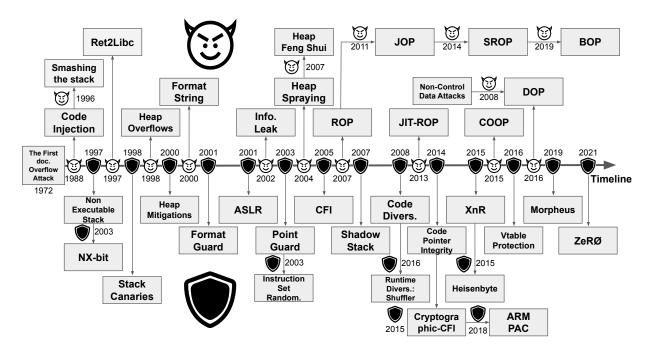

The C and C++ programming languages are the gold standard for implementing a wide range of software systems such as safety critical firmware, operating system kernels, and network protocol stacks for performance and flexibility reasons. As these languages do not guarantee the validity of memory accesses (i.e., enforce memory safety), seemingly benign program bugs can lead to silent memory corruption, difficult-to-diagnose crashes, and, most importantly, security exploitation. Attackers can compromise the security of the whole computing ecosystem by exploiting a memory safety error with a suitably crafted input. Since the first documented overflow attack in 1972 [13], there has been a long-lasting arms race between attackers and defenders, as shown in Figure 1.1. New attacks are followed by potential mitigations that aim at preventing the attackers' malicious effects while current mitigations are followed by novel attacks that propose new approaches for bypassing the deployed mitigations. Despite massive advances in exploit mitigations, memory safety errors have risen to be the most exploited vulnerabilities because current mitigations do not address the root cause of the problem, which is the lack of memory safety.

#### 1.1 What Is Memory Safety?

Memory safety is a program property that guarantees memory objects can only be accessed between their intended bounds, during their lifetime, and given their original (or compatible) type. Violating any of these requirements results in a memory corruption. For example, accessing objects beyond their intended bounds is called *spatial memory safety violation* (e.g., buffer overflow). On the other hand, accessing objects beyond their lifetime is called *temporal memory safety violation* (e.g., use-after-free and uninitialized reads). Finally, accessing objects with an incompatible type is referred to as *type confusion*, which can lead to both spatial and temporal violations.

Figure 1.1: Timeline for memory safety exploitation techniques (marked with demons) and mitigations (marked with shields).

Unfortunately, memory safety vulnerabilities are common. They are easy for programmers to introduce unintentionally, especially in large code bases and systems with complex logic. For example, Microsoft recently revealed that the root cause of around 70% of all exploits targeting their products is software memory safety violations [14]. Similarly, roughly 70% of all serious security bugs that have been fixed in the Google Chrome stable branch since 2015 are memory safety bugs, with half of them being use-after-free vulnerabilities [15]. Moreover, the Project Zero team at Google reports that memory corruption issues are the root-cause of 68% of listed CVEs for zero-day vulnerabilities between 2014 and 2019 [16]. With the increasing number of memory safety vulnerabilities discovered each year, a natural question to ask is: why does the memory safety problem persist despite the large efforts done by software vendors?

#### 1.2 Why Is Memory Safety Still A Concern?

To better understand why memory safety threats have not been completely resolved till now, we need to have a look on the available solutions so far.

#### 1.2.1 Memory-Safe Languages

One possible solution to the memory (un)safety problem is to refrain from using languages that rely on programmers to manually manage memory (i.e., C/C++). Instead, developers can use languages that provide automatic memory management (i.e., memory safe languages), such as Java, Python, and Rust. While those languages are widely-adopted, they are not going to replace C/C++ anytime soon for the following reasons.

- **Performance.** C offers high performance as it allows the programmer to directly interact with the underlying hardware. Alternative safe languages use automatic memory management, which adds extra overheads that are not acceptable, especially for real time systems.

- Communication. C is more suitable for system level code as it allows communication between different entities via memory. For example, a program can write to a memory-mapped location that will be consumed externally by another device in the system. Memory-safe languages do not guarantee this unless the entire system is written with them and compiled as a whole program.

- Completeness. Even for safe languages, the automatic memory management runtimes themselves are written in C and C++. The runtimes may have bugs that can be exposed through programs written in memory safe languages.

- Maturity. Existing developer skills and the huge ecosystem of tools and libraries around C and C++ means that shifting to new languages would be a slow and long-term process. We may have to wait at least as long as it took for C/C++ to become mainstream (i.e., decades).

- Legacy Code. There is a vast amount of legacy C code deployed throughout the world in operating systems, web browsers, shared libraries, and embedded software. Such systems consist of millions of lines of C code, preventing the complete transition away from C or its variants anytime soon.

The above reasons necessitate the development of memory safety solutions for C and C++ applications.

#### 1.2.2 Testing & Verification

To address the threat of memory safety violations, software testing tools (e.g., Google's AddressSanitizer [3]) and fuzz testing are widely deployed. In software fuzz testing binaries are instrumented with a tool like AddressSanitizer in order to detect memory safety vulnerabilities, then run with inputs mutated from a set of exemplary inputs in the hopes of detecting bugs before deployment. Google has reported that it has been performing fuzzing on about 25,000 machines continuously since 2016, which has resulted in the identification of many critical bugs in software such as Google Chrome and several open source projects [17]. Assuming 15 cents per CPU hour for large memory machines—a requirement for reasonable performance on fuzz testing—the investment in software fuzzing for detecting memory errors could be close to a billion dollars at just one company.

Despite a Herculean effort by software vendors, memory safety vulnerabilities continue to slip through, ending up in deployed systems. Recognizing that pre-deployment fuzz tests can never be complete, companies have also proposed post-deployment crowdsourced fuzz testing [18, 19, 20, 21]. For instance, Google recently proposed fuzzing Android software in the field on user phones when they are plugged into power. Assuming that these tests run when phones are being charged, and assuming most users leave their phone charged overnight, on a global scale, the amount of energy invested in producing reliable software may be even higher than the amount of time running the software with crowdsourced testing. Thus, developing more efficient memory error detectors can have significant green benefits in addition to improving security and reliability.

#### 1.2.3 Hardware-Based Mitigations

Both academia [22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32] and industry [4, 33, 5, 9, 10] have proposed various hardware-based techniques to address the C/C++ memory safety problem over

the last three decades. Prior work can be broadly categorized into the following four classes:

- **Memory Blocklisting.** This class of memory safety techniques (also known as tripwires) aims to detect overflows by marking the memory regions on either side of an allocation, and flagging accesses to them. For example, REST [30] stores a predetermined 8–64B random number, dubbed a token, in the memory to be invalidated. Spatial memory safety violations are detected by comparing cache lines with the token when they are fetched.

- **Memory Permitlisting.** This class of memory safety solutions (also known as base & bounds) attaches bounds metadata to every pointer or allocation. The metadata can be stored in a shadow (also known as disjoint) memory region (e.g., Hardbound [26], Intel's MPX [33], CHEx86 [31], and AOS [32]) or be marshaled with the pointer by extending its size (e.g., CHERI [29]).

- **Memory Tagging.** This class of memory safety techniques associates a "color" with newly allocated memory, and stores the same color in the upper bits of the data pointer that is used to access the allocated memory. At runtime, the hardware enforces spatial memory safety by comparing the colors of the pointer and accessed memory. For example, SPARC's ADI [4] assigns 4-bit colors to every 64B of memory (i.e., limiting the minimum allocation size to 64B), while ARM's MTE [5] uses 4-bit colors per every 16B of memory [34]. Since metadata bits are acquired along with the corresponding data, no extra memory operations are needed.

- Exploit Mitigation. This class of defenses neither detects nor prevents memory safety violations. Instead, exploit mitigations focus on preventing the attackers from manipulating main program assets (e.g., return addresses and function pointers) to protect the victim machine. Examples include Intel's CET [9], which uses a shadow stack to protect return addresses and ARM's PAC [10], which uses cryptographic message authentication codes to protect the integrity of pointers.

The main advantage of hardware-assisted solutions is its low performance overheads compared to software-based techniques. Thus, hardware solutions can be used as always-on mitigations to catch memory safety bugs in the field, if those bugs escape testing. Unfortunately, state-of-the-art hardware proposals suffer from other limitations.

#### 1.3 Why Are Current Hardware-Based Solutions Impractical?

Current hardware-based memory safety proposals suffer from one or more of the following limitations, making them impractical to use in deployed systems:

- Complex metadata management. Techniques that store the metadata (e.g., per pointer base and bounds information) in disjoint shadow memory [26, 33, 32, 31] require extra memory accesses per pointer load/store to fetch and update the metadata. Besides the performance cost, frequently accessing the disjoint metadata may introduce atomicity problems for multithreading applications. A practical memory safety solution needs to efficiently manage and access its own metadata.

- Breaking binary compatibility. To avoid disjointly storing the metadata, some techniques (also known as FAT pointers [29, 35]) increase the pointer width to include the metadata. Using FAT pointers changes objects layouts in memory and breaks compatibility with the rest of the system (e.g., unprotected libraries). A practical memory safety solution needs to be compatible with the other system entities without introducing (de)serialization penalties.

- **Incomplete protection.** Memory tagging techniques associate a tag with newly allocated memory, and store the same tag in the upper bits of the data pointer that is used to access the allocated memory. Due to the tag's limited size, memory tagging solutions offer low entropy for temporal protection and non-adjacent spatial violations. A practical memory safety solution needs to provide strong guarantees against different memory safety threats.

- **Side-channel resiliency.** Speculative side-channel attacks (also known as Spectre) represent a major concern to current memory safety techniques, as Spectre can be used to undermine

their security guarantees. For example, attackers can infer the memory tag value of some memory region without triggering a memory tagging violation and use that to bypass memory tagging solutions [36]. A practical memory safety solution needs to consider speculative side-channel attacks and ensure they cannot be used to bypass the solution itself.

#### 1.4 Thesis Statement & Contributions

In light of the above discussion, this dissertation makes the following thesis statement:

Leveraging common software trends and rethinking computer microarchitectures can efficiently circumvent the problems of traditional memory safety solutions for C and C++.

To support the above thesis statement, this dissertation makes the following contributions:

#### 1.4.1 Califorms

The first contribution of this thesis is novel Cache Line Formats (Califorms) [6]. Califorms uses a two-fold approach for reducing memory safety overheads. First, instead of checking access bounds for each pointer access, Califorms blocklists all memory locations that should never be accessed. This reduces the additional work required to enforce memory safety, such as comparing bounds. Second, Califorms uses a novel metadata storage scheme for storing blocklisted information. The key observation is that by using dead memory spaces in the program, we can store necessary memory safety metadata for free for nearly half of the program's objects. These dead spaces can occur for several reasons, including language alignment requirements. When we cannot find naturally occurring dead spaces, we automatically insert them using compiler transformation. In order to distinguish the dead bytes from normal bytes in memory, Califorms uses a compressed encoding that requires one bit per each 64B cache line. If an attacker accesses these dead (i.e., blocklisted) regions, we detect this rogue access without any additional metadata accesses as our metadata resides inline.

Experimental results from the SPEC CPU2006 benchmark suite indicate that the overheads of Califorms are quite low: software overheads range from 2 to 14% slowdown (or alternatively, 1.02x to 1.14x performance overhead) depending on the amount and location of padding bytes used. The hardware induced overheads are also negligible, on average less than 1%. These overheads are substantially lower compared to the state-of-the-art software or hardware supported schemes (viz., 2.2x performance and 1.1x memory overheads for EffectiveSan [37], and 1.7x performance and 2.1x memory overheads for Intel's MPX [38]).

#### 1.4.2 No-FAT

The second contribution of this thesis is a novel technique, dubbed No-FAT [7], for enforcing spatial and temporal memory safety by implicitly deriving the metadata information from the pointer itself. The key observation that enables No-FAT is the increasing adoption of binning allocators. We observe that current memory allocators use bags of pages (called bins), where each bin allocates objects of the same size. Using bins enables the allocator to quickly serve allocation requests and increases performance by maintaining allocation locality [39, 40, 41, 42]. No-FAT, when used with a binning allocator, is able to *implicitly* derive allocations bounds information (i.e., the base address and size) from the pointer itself without relying on expensive metadata. The hardware/software contract has to be tweaked slightly to facilitate the cooperation of No-FAT with binning allocators: the standard allocation sizes used by a binning allocator need to be supplied to the hardware and special load and store instructions are created to access the allocation sizes. In other words, the memory allocation size (e.g., malloc size) becomes an architectural feature.

No-FAT introduces an average of 8% performance overheads on the SPEC CPU2017 benchmark suite. No-FAT also provides resilience against the growing threat of speculative execution attacks. For example, Spectre-V1 [43] attacks exploit speculative execution to access out-of-bounds memory, effectively bypassing software based bounds checks. No-FAT's memory instructions are aware of allocation bounds information. Thus, allocation bounds information can be used to verify if memory accesses are within valid bounds even for speculatively executed instructions.

#### 1.4.3 C-5

During program execution, user data can be manipulated from within the victim program (e.g., via an inter-process side-channel attack). A recent work from Intel Labs, called Cryptographic Capability Computing (C³), claims to provide resiliency against in-process and physical attacks [44]. In this thesis, I conduct a detailed assessment of the C³'s security claims. I uncover four different attack vectors against C³, dubbed C-4, and show how these attacks can bypass the C³'s spatial and temporal memory safety guarantees, in addition to breaking its data confidentiality. My attacks exploit C³'s fundamental design choices, such as (1) using a fixed one-time pad for per-object data encryption, (2) lacking bounds checking on pointer arithmetic and usages, (3) providing low entropy against temporal safety violations, and (4) leaving the application's stack, global, and intra-allocation objects unprotected. Naively addressing the proposed attacks will require redesigning C³ to use bounds checking and a stronger cipher, which will result in high performance overheads and negate C³'s stateless and compatibility claims.

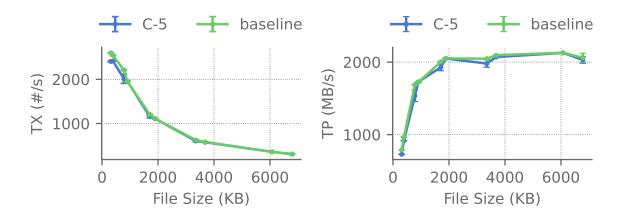

Thus, the third contribution of this thesis is C-5, a Counter C-4 Architecture [8]. C-5 integrates strong data encryption with No-FAT to mitigate both in-process and physical attacks without burdening the system performance. Our evaluation results using the SPEC CPU2017 benchmark suite show that Counter C-4 Architecture introduces no runtime cost. Furthermore, we evaluate C-5 on the Nginx web server [45] and observe negligible overheads on the transfer rate and throughput for various file sizes.

#### 1.4.4 ZeRØ

The aforementioned three contributions of this thesis focus on detecting memory safety errors to secure software written in C and C++. Another prominent way of thwarting memory safety attackers is by using exploit mitigation techniques. Due to their low overheads, hardware vendors have invested in deploying exploit mitigations such as Intel's CET [9] and ARM's PAC [10]. So, can leveraging software properties and rethinking microarchitectures help to enhance the security

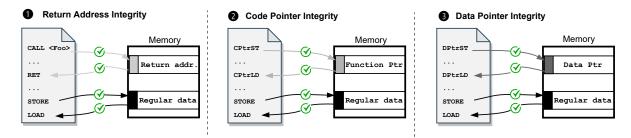

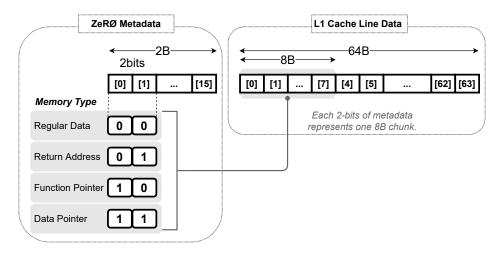

guarantees of exploit mitigations while maintaining their low overheads? The answer is "yes". The fourth contribution of this thesis is ZeRØ, a hardware primitive that provides zero-overhead resilient operation under pointer integrity attacks [11]. ZeRØ leverages the currently unused upper bits in 64-bit pointers to store metadata that identifies different pointer types and distinguish them from regular non-pointer data. The hardware then uses special memory access instructions to access pointers based on their encoded types and hence prevents any malicious memory accesses (via buffer overflows for example) from corrupting pointers.

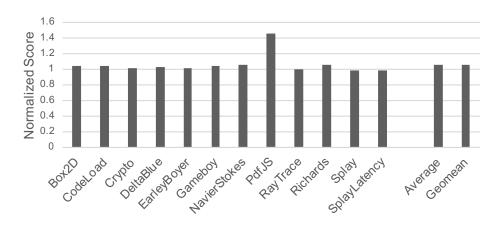

ZeRØ uses a novel metadata encoding scheme that allows it to precisely store all the required metadata to identify different program assets with a single bit per every cacheline in L2 and main memory (less than 0.2% memory overheads). Additionally, ZeRØ avoids crashing the victim program upon detecting an attack. Instead, ZeRØ raises an advisory exception to the operating system and continues program execution after skipping the violating memory access. This prevents the attacker from abusing ZeRØ to launch a denial-of-service attack. Our experimental results on the SPEC CPU2017 benchmark suite indicate that the software overheads of ZeRØ are 0% compared to a baseline. Additionally, our VLSI implementation results show that ZeRØ can be efficiently added to modern processors with negligible performance, area, and power overheads. Unlike other pointer authentication solutions, ZeRØ does not need to dedicate an energy budget to cryptographic co-processors [46, 10, 47] or standalone shadow stacks [9].

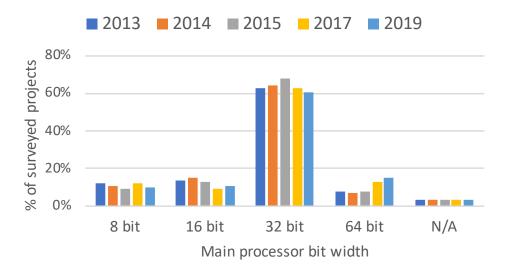

#### 1.4.5 EPI

Embedded systems interact with many aspects of our daily lives, ranging from cell phones and life saving medical devices to aircraft and satellite systems. Due to their resource-constrained nature, embedded applications and firmwares are typically written in C to take advantage of its direct memory management and high performance, making them vulnerable to memory corruption attacks. Unfortunately, state-of-the-art exploit mitigation techniques are mainly designed for 64-bit processors and thus perform poorly when deployed on non 64-bit processors, the common choice for embedded systems [48, 49]. As a result, there is a need for solutions to the problem of securing

embedded 32-bit systems with minimal performance, power, and area overheads. Hence, my fifth contribution is Efficient Pointer Integrity (EPI), a hardware-based technique that mitigates memory safety-based attacks by ensuring the integrity of valuable application assets (i.e., pointers) [12].

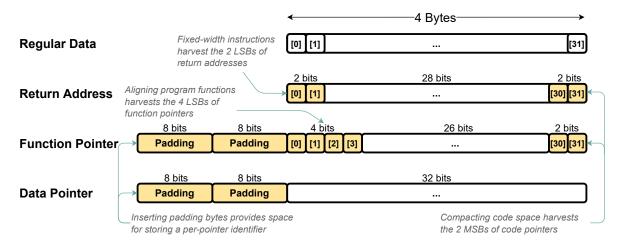

Similarly to ZeRØ, EPI assigns unique tags to different program assets and uses unique memory instructions for accessing them. Unlike ZeRØ, which relies on the currently unused upper bits in 64-bit pointers to inline its metadata, EPI implements a novel metadata encoding scheme that is tailored for 32-bit architectures. The key observation that enables our EPI encoding is that leveraging common software properties allows for harvesting extra bits from pointers on 32-bit architectures. Examples for such properties include aligning stack frames and program functions, compacting code space, and inserting padding bytes. Our experimental results show that EPI's software introduces an average of 0.88% runtime overheads on the SPEC CPU2017 benchmark suite while having negligible latency and energy overheads.

#### 1.5 Thesis Organization

The rest of this thesis is organized as follows: Chapter 2 provides an overview on program segments and memory safety in the C and C++ programming languages. Chapter 3 presents Califorms as an efficient memory blocklisting technique. Chapter 4 summarizes the key components of my permitlisting solution, No-FAT. Next, Chapter 5 discusses the C-5 architecture for mitigating both in-process and physical attacks. Afterwards, I illustrate my exploit mitigation technique, ZeRØ in Chapter 6 and its 32-bit variant, EPI in Chapter 7. Chapter 8 outlines how the techniques described in this thesis are different compared to prior work in the area of memory safety error detection and exploit mitigation. Finally, Chapter 9 concludes the thesis.

#### **Chapter 2: Background**

This chapter provides the necessary background information on the different concepts that will be needed over the course of this thesis. First, I summarize the main components of a computer program . Then, I introduce the memory safety problem in C and C++. Afterwards, I provide an overview of memory corruption attacks to further motivate the need for stronger defenses.

#### 2.1 Program Components

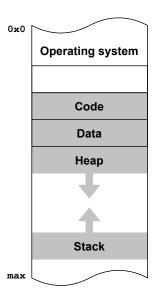

As memory safety vulnerabilities can affect any segment of a program's memory, this section summarizes the main components of a program's address space. Figure 2.1 shows the memory layout of a typical C program. The top of the address space (i.e., addresses closer to  $0\times0$ ), is reserved for the operating system. The remaining parts are usable by the user-land process and include the program's code and data sections in addition to the dynamically changing regions of memory—the heap and the stack.

Figure 2.1: The main components of a program's address space.

#### 2.1.1 Code

The code segment (also known as the .text section) is used to store the program instructions that need to be executed at runtime. This segment is typically marked as read-only in order to prevent attackers (or benign program errors) from modifying the instructions.

#### 2.1.2 Globals

Global variables are seen by the entire program and are typically stored on the .data and .bss memory segments. Specifically, the .data segment stores global variables and static variables that are initialized by the programmer. On the other hand, the .bss segment contains uninitialized static data, i.e., global variables and local static variables that are initialized to zero or do not have explicit initialization in the program source code. For example, a global variable declared as int k = 7; would be stored in the .data segment, whereas a global variable declared int m; would be stored in the .bss segment.

#### 2.1.3 Stack

Local variables, which are used by individual program functions, are stored in the stack. When a function is called, the return address (and the caller saved registers) are pushed to the stack. The newly called function then allocates room on the stack for storing its own local variables. This way the stack grows (and shrinks) dynamically as the program runs. The *stack pointer* is used to track the top of the stack during program execution.

#### 2.1.4 Heap

The heap part of a program's address space is used to store dynamically allocated memory. It is managed by memory management functions such as malloc, calloc, realloc, and free which are provided by a memory allocator. A memory allocator is responsible for partitioning the heap memory space and serving the requested allocation sizes in a timely manner while minimizing internal and external fragmentation.

Memory allocators can be categorized into two main categories: binning and coalescing. Binning memory allocators divide the available space into fixed-size regions, where each region is used to allocate objects of a pre-determined size. Thus, the memory size returned to a program is rounded up to one of the standard sizes offered by the allocator. Examples of binning memory allocators include Jemalloc [40], Microsoft's Mimalloc [42], and Google's TCmalloc [39]. On the other hand, coalescing memory allocators dynamically join and split memory regions depending on the requested chunk size. Thus, they can provide the exact amount of memory requested by the program at the cost of an additional allocation header to store its size. An example for coalescing memory allocators is Dlmalloc [50]. In general, memory allocators use system calls, such as brk, sbrk, and mmap for expanding the heap size.

#### 2.2 Memory Safety Definition

For a C or C++ application to be memory safe, all memory objects should only be accessed: (1) between their intended bounds, (2) during their lifetime, and (3) given their original (or compatible) type. Violating any of the above requirements can lead to silent memory corruption, difficult-to-diagnose crashes, and, most importantly, security exploitation [1].

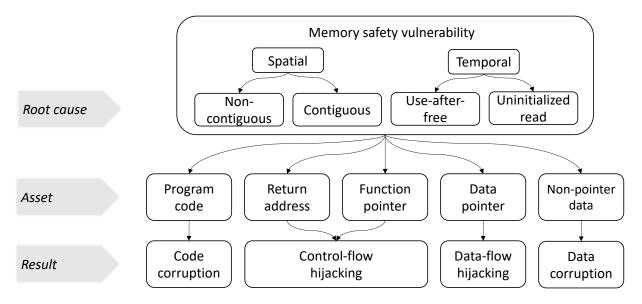

Figure 2.2: Memory corruption root causes, targets, and end results.

#### 2.2.1 Spatial Memory Safety

This class of memory safety vulnerabilities occurs when a pointer is used to access an object beyond its intended bounds (i.e., base address and size) [51]. Examples include buffer under-/overflows, in which the application writes beyond the buffer's original bounds, causing a memory corruption in a different memory object. As shown in Figure 2.2, spatial violations can be further categorized into contiguous violations (in which the attacker overwrites an adjacent buffer) or a non-contiguous violation (in which the attacker overwrites arbitrary locations in memory). Finally, if the victim buffer is a field within a C struct or a member within a C++ class, such a violation is referred to as an intra-object spatial memory safety violation.

#### 2.2.2 Temporal Memory Safety

This type of memory safety violations occurs when a pointer is used to access an object beyond its lifetime (e.g., use-after-free or uninitialized read). In use-after-free vulnerabilities the application uses a dangling pointer to access a heap object after it is deleted, or a stack object after its stack frame has been destroyed. For uninitialized reads, the programmer allocates an object and starts reading from it before writing anything to it. As a result, previous contents of the object might be leaked, violating memory safety.

#### 2.2.3 Type Memory Safety

This class of memory safety violations (also known as type confusion) occurs when a memory location is accessed with an incompatible type. For example, the program first allocates (or initializes) a memory object using one type, and then accesses the same object later using a type that is incompatible with the original type due to an unsafe typecasting. Type confusion can trigger a spatial memory safety violation if the sizes of the two confused objects do not match. It can also trigger a temporal memory safety violation if the same memory region was allocated to one object and then assigned to an object of a different type after the original object was deleted.

#### 2.3 Memory Safety Attacks

No matter what memory safety vulnerability a program has, an attacker can exploit it to manipulate one of the program assets, as shown in Figure 2.2. Valuable assets include program code, return addresses on the stack, function and data pointers on the heap, and non-pointer data (i.e., local variables and struct fields). Based on what asset is manipulated, an attacker can achieve different end results.

#### 2.3.1 Code Corruption

Traditional approaches for exploiting memory vulnerabilities aimed at either (i) overwriting program instructions in memory with an attacker's payload or (ii) dumping the attacker's code discretely to the program stack and executing it. Nowadays, code corruption attacks are ineffective due to the widespread deployment of W^X [52]. In other words, an attacker cannot overwrite program data (i.e., code is marked as readable and executable but not writable) and cannot write and execute their own code (i.e., data is marked as readable and writable but not executable).

#### 2.3.2 Control-Flow Hijacking

This line of attacks, which are also known as code reuse attacks (CRAs), exploits memory vulnerabilities to overwrite code pointers stored in memory. Corrupting a code pointer can cause a control-flow transfer to anywhere in executable memory. Code pointers include return addresses on the stack and function pointers anywhere in memory. As code pointers are stored in program memory (stack and heap), they are a common target for attackers. For example, return oriented programming (ROP) [53, 54] corrupts return addresses, whereas call- and jump-oriented programming [55, 56] corrupt function pointers (or indirect code addresses in general).

To mount a CRA, the attacker has to first analyze the code to identify the attack gadgets, or sequences of instructions in the victim program that end with a return or jump instruction. Second, the attacker uses a memory corruption vulnerability to inject a sequence of target addresses corre-

sponding to a sequence of gadgets. When the function returns (or a code pointer is dereferenced), it moves to the location of the first gadget. As that gadget terminates with a control flow instruction (e.g., return), it transfers program execution to the next gadget, and so on. As CRAs execute existing instructions belonging to the program, they are not prevented by W^X.

#### 2.3.3 Data-Flow Hijacking

In contrast to control-flow hijacking attacks, data-oriented programming (DOP) attacks can cause malicious end results without changing the control flow of the program. Prior works show that manipulating data pointers in memory is sufficient for the attacker to achieve arbitrary computations on program input [57, 58, 59]. As DOP attacks do not alter the program control flow, they can easily bypass all control-flow integrity solutions. Thus, DOP is an appealing attack technique for future run-time exploitation defenses.

#### 2.3.4 Data Corruption

This last class of attacks targets non-pointer data items while stored in memory. Examples include manipulating program flags to bypass selective checks and changing configuration parameters [60]. Mitigating non-pointer data corruption attacks requires full memory safety solutions, which traditionally come with high performance overheads.

### Part II

# Rethinking Microarchitectures For Efficient Memory Blocklisting

#### **Chapter 3: Cache Line Formats**

Historically, program memory safety violations have provided a significant opportunity for exploitation by attackers. To address this threat, software checking tools [3] and commercial hardware support for memory safety [4, 33] have enabled programmers to detect and fix memory safety violations before deploying software. Current software and hardware-supported solutions excel at providing coarse-grained inter-object memory safety, which involves detecting memory access beyond arrays and heap allocated regions (malloc'd struct and class instances). However, these solutions are not suitable for fine-grained memory safety (i.e., intra-object memory safety or detecting overflows within objects, such as fields within a struct, or members within a class) due to the high performance overheads and/or need for making intrusive changes to the source code [51]. For instance, a recent work that aims to provide intra-object overflow protection functionality incurs a 2.2x performance overhead [37]. These overheads are problematic because they not only reduce the number of pre-deployment tests that can be performed, but also impede post-deployment continuous monitoring, which researchers have pointed out is necessary for detecting benign and malicious memory safety violations [34]. Thus, a low overhead memory safety solution that can enable continuous monitoring and provide complete program safety has been elusive.

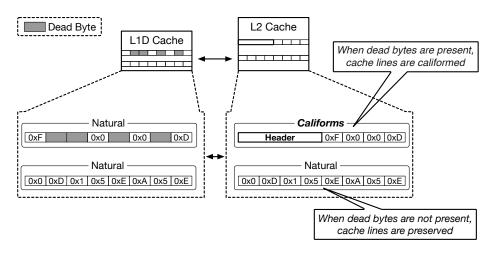

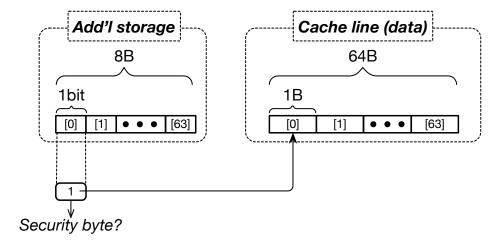

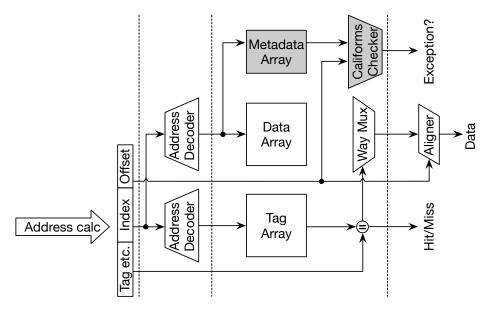

In this chapter I propose Califorms, a novel hardware primitive that allows blocklisting of a memory location (i.e., if accessed due to programming errors or malicious attempts, it reports a privileged exception) at *byte granularity* with low area and performance overheads. The main obstacle to blocklisting a memory region at a fine granularity (e.g., to prevent intra-object overflows) is the overhead of maintaining metadata. We solve this problem based on the following key observation: a blocklisted region need not store its metadata (indicating it is blocklisted) separately, but can rather store it within itself (since it contains no useful data!). With this principle, we utilize existing or added bytes between object elements to blocklist a region. This in-place compact data

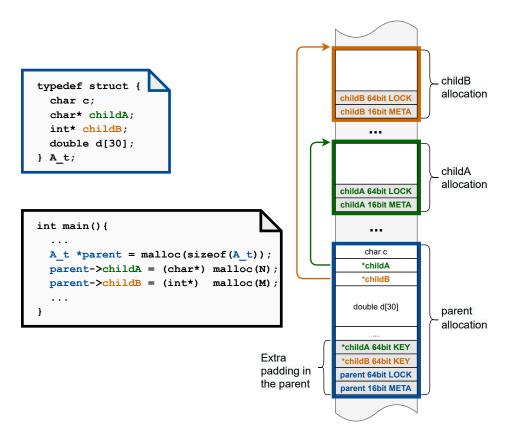

Figure 3.1: A high level overview of how Califorms works. Califorms offers memory safety by detecting accesses to dead bytes in memory. Dead bytes are not stored beyond the L1 data cache and identified using a special header in the L2 cache (and beyond) resulting in very low overhead. The conversion between these formats happens when lines are filled or spilled between the L1 and L2 caches. The absence of dead bytes results in the cache lines stored in the same natural format across the memory system.

structure avoids additional operations for accessing the metadata, making it very performant in comparison.

The challenge lies in how to reduce the additional hardware overhead required to identify normal data versus metadata. A naive implementation requires additional one bit (to specify normal data or metadata) per byte, which results in 12.5% area overhead. We manage to reduce the overhead substantially, to one bit per cache line (typically 64 bytes, thus area overhead of 0.2%), by changing how data is stored within a cache line. For cache lines which contain metadata (within blocklisted bytes), the actual data is stored following the "header", which indicates the location of blocklisted bytes, as shown in Figure 3.1.

The remainder of this chapter is organized as follows. Section 3.1 provides further motivation for Califorms. Section 3.2 explains the full system overview of Califorms. Section 3.3 discusses the Califorms architectural support. Section 3.4 details the microarchitectural design of Califorms whereas Section 3.5 specifies its software design. Section 3.6 analyzes the Califorms security guarantees. Section 3.7 evaluates the hardware and software overheads of Califorms. Section 3.8 summarizes the chapter.

#### 3.1 Motivation

```

struct A {

struct A_opportunistic {      struct A_full {

struct A_intelligent {

char c;

char c;

/* we protect every field

char c;

int i:

* with random

/* compiler inserts

int ::

char buf [64];

* padding bytes

* security bytes */

/* we protect boundaries

* for alignment */

char security_bytes[2];

void (*fp)();

* of arrays and pointers

char padding_bytes[3];

char c;

* with random

int i;

char security_bytes[1];

* security bytes */

char buf [64];

int i:

char security_bytes[3];

void (*fp)();

char security_bytes[3];

char buf [64];

char buf [64];

char security_bytes[2];

char security_bytes[2];

void (*fp)();

void (*fp)();

char security_bytes[3];

char security_bytes[1];

(a) Original.

(b) Opportunistic.

(d) Intelligent.

(c) Full.

```

Figure 3.2: Califorms Insertion Polices. (a) Original source code and examples of three security bytes harvesting strategies: (b) *opportunistic* uses the existing padding bytes as security bytes, (c) *full* protect every field within the struct with security bytes, and (d) *intelligent* surrounds arrays and pointers with security bytes.