# CircuitSim

Andrew Yang Case Schemmer Faustina Cheng Jary Tolentino Ming Gong Overview

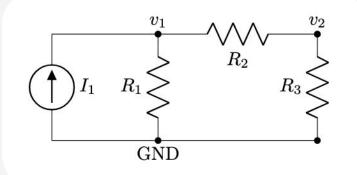

## (Modified) Node Voltage Analysis

Kirchhoff's Current Law:

$$\frac{v_1}{R_1} + \frac{v_1 - v_2}{R_2} - I_1 = 0$$

$$\frac{v_2}{R_2} + \frac{v_2 - v_1}{R_3} = 0$$

System of Equations:

$$\begin{cases} G_1v_1 + G_2(v_1 - v_2) = I_1 \\ G_3v_2 + G_2(v_2 - v_1) = 0 \end{cases}$$

$$\begin{bmatrix} G_1 + G_2 & -G_2 \\ -G_2 & G_2 + G_3 \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \end{bmatrix} = \begin{bmatrix} I_1 \\ 0 \end{bmatrix}$$

$$G\mathbf{v} = \mathbf{I}$$

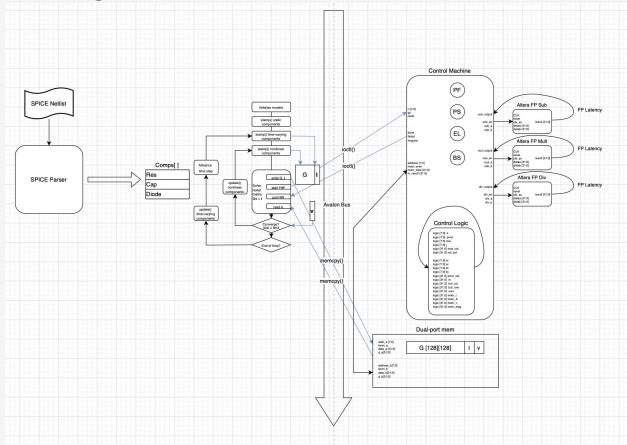

# **Overall Design**

Driver:

- 1. Takes in input file (SPICE netlist)

- a. Circuit components + transient analysis parameters

- 2. Translates the components into matrix representation

- 3. Matrix solver loop

- a. Matrix is written to FPGA memory

- b. FPGA performs Gaussian Elimination

- c. FPGA writes results

- 4. Writes to CSV file (time, node/voltage values)

Overview

# **Input Parsing**

Input: SPICE deck

\* Components

V1 1 0 DC 5;

R1 1 2 10;

L1 2 3 1e-3;

C1 3 0 1e-6;

\* Simple LRC

.TRAN 5e-6 0.50

\* End of Netlist

.END

#### Parse:

add\_vsrc(...)

add\_res(...)

add\_ind(...)

add\_cap(...)

#### Component Array:

Vsrc type: Linear stamp\_lin: vsrc\_stamp n1:1 n2:0 ni:4 dc\_value: 5

#### Res

type: Static stamp\_lin: res\_stamp n1: 1 n2: 2 resistance: 10

Ind type: Linear stamp\_lin: ind\_stamp update: ind\_update n1: 2 n2: 3 L: 1e-3 dt: 5e-6 i\_prev: 0 v\_prev: 0

#### Cap

type: Linear stamp\_lin: cap\_stamp update: ind\_update n1: 3 n2: 0 C: 1e-6 dt: 5e-6 i\_prev: 0 v\_prev: 0

# **Input Parsing**

We support the definition of:

- Voltage and current sources

- Voltage controlled voltage and current sources

- Resistors

- Capacitors

- Inductors

- Diodes

- NMOS and PMOS

Miscellaneous

- .TRAN (time information for transient analysis)

- Comments

Models

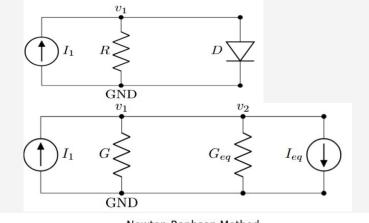

# Diode

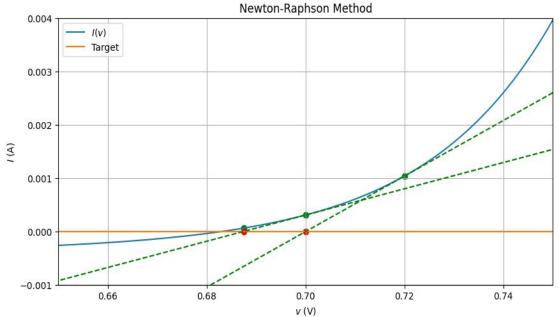

Newton's method

$$i_d = I_s(e^{v_d/V_t} - 1)$$

$$G_{eq} \equiv \frac{di_d}{dv_d} = \frac{I_s}{V_t} e^{v_{d0}/V_t}$$

$$i_d \approx i_{d0} + G_{eq}(v_d - v_{d0})$$

$$= (i_{d0} - G_{eq}v_{d0}) + G_{eq}v_d$$

- 1. Stamp

- 2. Solve

- 3. Update

Models

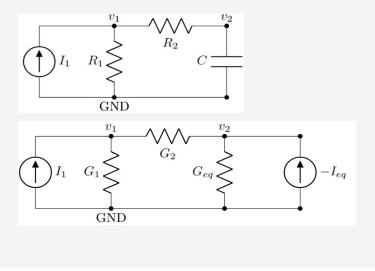

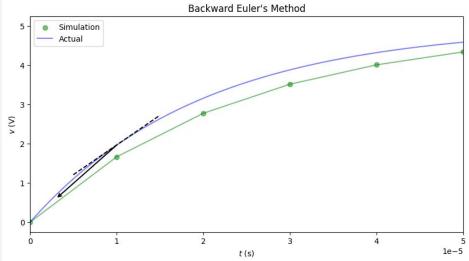

# Capacitor

Make a time step approximation

$$\begin{split} i(t) &= C \frac{dv_C}{dt} = C \frac{d(v_2 - 0)}{dt} \\ i(t_0 + \Delta t) &\approx C \frac{v_2(t_0 + \Delta t) - v_2(t_0)}{\Delta t} \\ v_2(t_0 + \Delta t) &= v_2(t_0) + \frac{\Delta t}{C} i(t_0 + \Delta t) \\ v_2(t) &= v_2(t_0) + \frac{\Delta t}{C} i(t) \end{split}$$

Models

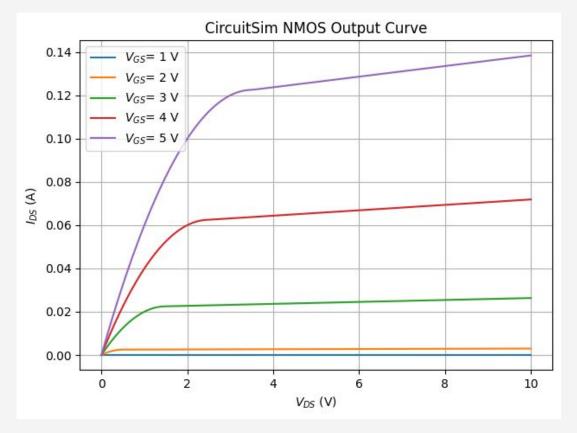

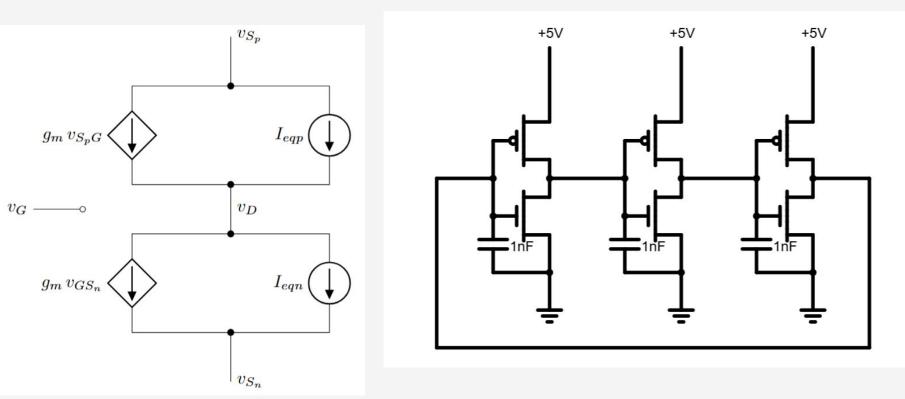

# **MOSFETs**

Piecewise nonlinear equation Multivariable linear models

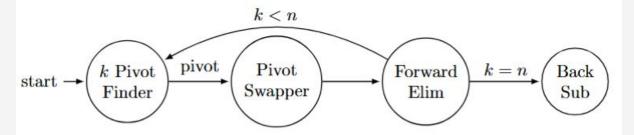

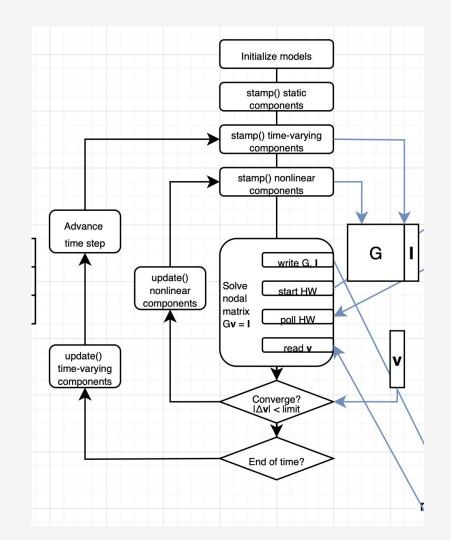

# **Matrix Solver**

For each timestep:

- Stamp static components

- While (not converged)

- Stamp linear components

- Copy G and I to FPGA

- ioctl()

- Solves matrix on hardware

- Read **v** from FPGA

Gaussian Hardware

Theory

Gaussian Elimination:

$$\begin{bmatrix} 1 & -2 & 1 \\ -2 & 1 & -1 \\ 1 & -1 & 0 \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} 1 \\ 0 \\ 5 \end{bmatrix}$$

$$\begin{bmatrix} -2 & 1 & -1 \\ 1 & -2 & 1 \\ 1 & -1 & 0 \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} 0 \\ 5 \\ 1 \end{bmatrix}$$

$$\begin{bmatrix} -2 & 1 & -1 \\ 0 & -1.5 & 0.5 \\ 0 & -0.5 & -0.5 \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} 0 \\ 1 \\ 5 \end{bmatrix}$$

$$\begin{bmatrix} -2 & 1 & -1 \\ 0 & -1.5 & 0.5 \\ 0 & 0 & -2/3 \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} 0 \\ 1 \\ 14/3 \end{bmatrix}$$

Gaussian Hardware

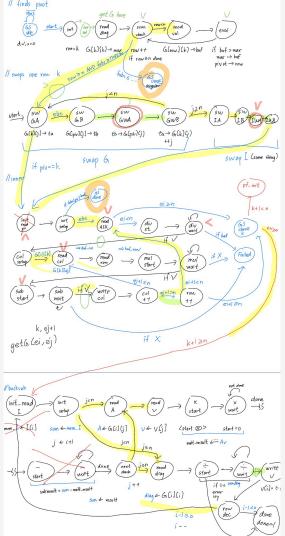

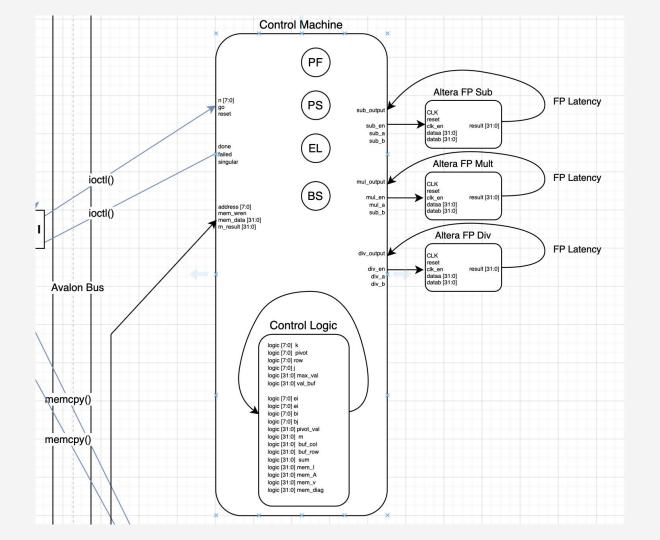

#### **State Machine**

11

## State Block Diagram

# State Block Diagram

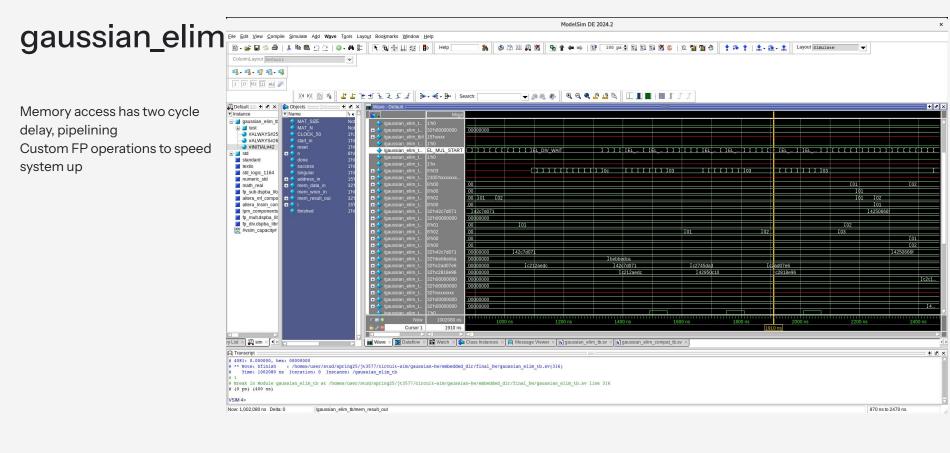

## **FP IP**

Intel FPGA, set FP to work for 50MHz clock and had corresponding latencies

| Wave - Default :        |         |     |         |  |      |  |  |  |   |  |   |           |

|-------------------------|---------|-----|---------|--|------|--|--|--|---|--|---|-----------|

| 🔬 🗸                     | Msgs    |     |         |  |      |  |  |  |   |  |   |           |

| /test_div_tb/CLOC       | 1'h0    |     |         |  |      |  |  |  |   |  |   |           |

| 😟 🥠 /test_div_tb/div_a  | 7.50000 | -X  | 7.50000 |  |      |  |  |  |   |  |   |           |

| 🖽 🥠 /test_div_tb/div_b  | 2.50000 | ×   | 2.50000 |  |      |  |  |  |   |  |   | المسمع ال |

| /test_div_tb/div_en     |         |     |         |  |      |  |  |  |   |  |   |           |

|                         | 1'h0    |     |         |  |      |  |  |  | - |  |   |           |

| 🚛 🔶 /test_div_tb/div_re | 3.00000 | (+0 |         |  | QNAN |  |  |  |   |  | х | 3.00000   |

|                         |         |     |         |  |      |  |  |  |   |  |   |           |

Interface

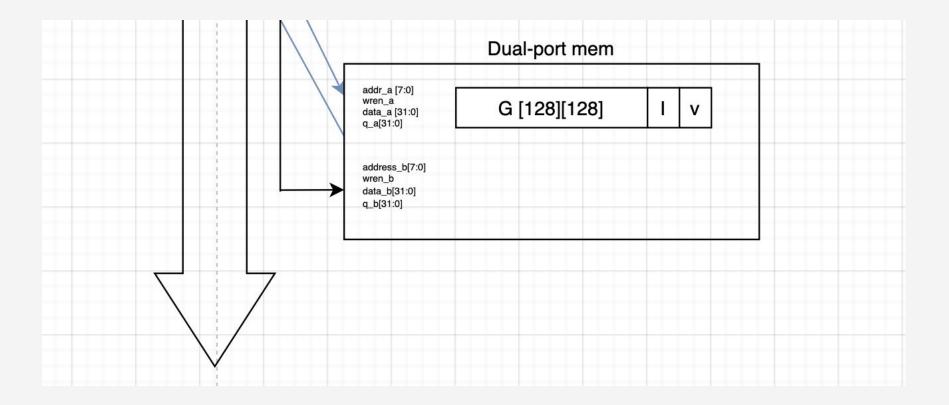

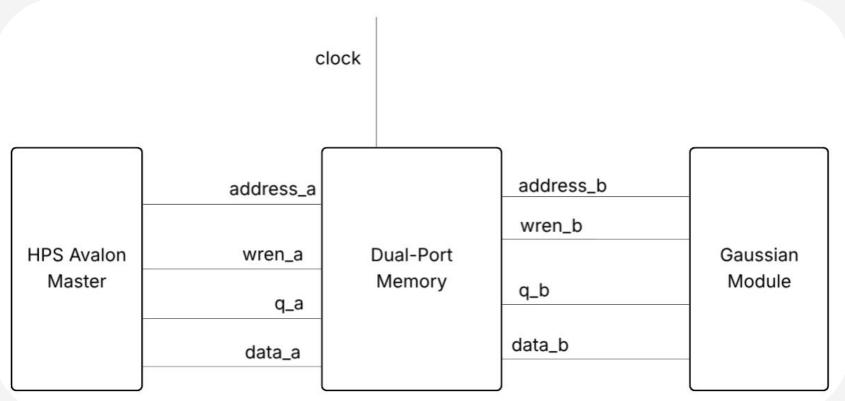

# M10K Memory

Interface

# Control Signal ioctl()

|   |   |                 | Matrix dim (8 bits) |  |  |  |

|---|---|-----------------|---------------------|--|--|--|

| G | R | Unused (6 bits) |                     |  |  |  |

| D | Е | S               | Unused (5 bits)     |  |  |  |

# **Platform Designer**

| Use | Connections | Name                                                                                                                           | Description                                                                                        | Export                                                                                                         | Clock                                                        | Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | End                        |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| ~   |             | ⊟ clk_0                                                                                                                        | Clock Source                                                                                       |                                                                                                                |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

|     |             |                                                                                                                                | Clock Input<br>Reset Input<br>Clock Output<br>Reset Output                                         | clk<br>reset<br>Double-click to<br>Double-click to                                                             | exported<br>clk_0                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

| ×   |             | moniory                                                                                                                        | Arria V/Cyclone V Hard Proce<br>Clock Output<br>Conduit<br>Conduit<br>Reset Output                 | Double-click to<br>hps_ddr3<br>hps<br>Double-click to                                                          | hps_0_h2                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

|     |             | h2f_axi_clock<br>h2f_axi_master<br>f2h_axi_clock<br>f2h_axi_slave<br>h2f_lw_axi_clock<br>h2f_lw_axi_clock<br>h2f_lw_axi_master | Clock Input<br>AXI Master<br>Clock Input<br>AXI Slave<br>Clock Input<br>AXI Master                 | Double-click to<br>Double-click to<br>Double-click to<br>Double-click to<br>Double-click to<br>Double-click to | clk_0<br>[h2f_axi<br>clk_0<br>[f2h_axi<br>clk_0<br>[h2f_lw_a | al and a second s |                            |

|     |             | gaussian_0<br>clock<br>reset<br>csr<br>mem                                                                                     | gaussian<br>Clock Input<br>Reset Input<br>Avalon Memory Mapped Slave<br>Avalon Memory Mapped Slave | Double-click to<br>Double-click to<br>Double-click to<br>Double-click to                                       | clk_0<br>[clock]<br>[clock]<br>[clock]                       | 0x0000_0000     0x0000 0000     0x0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x0000_0003<br>0x0001 ffff |

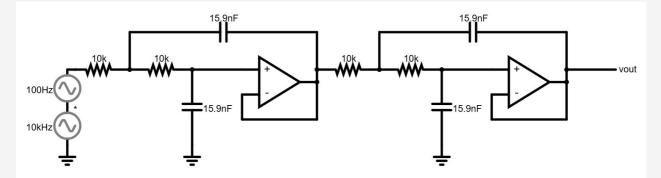

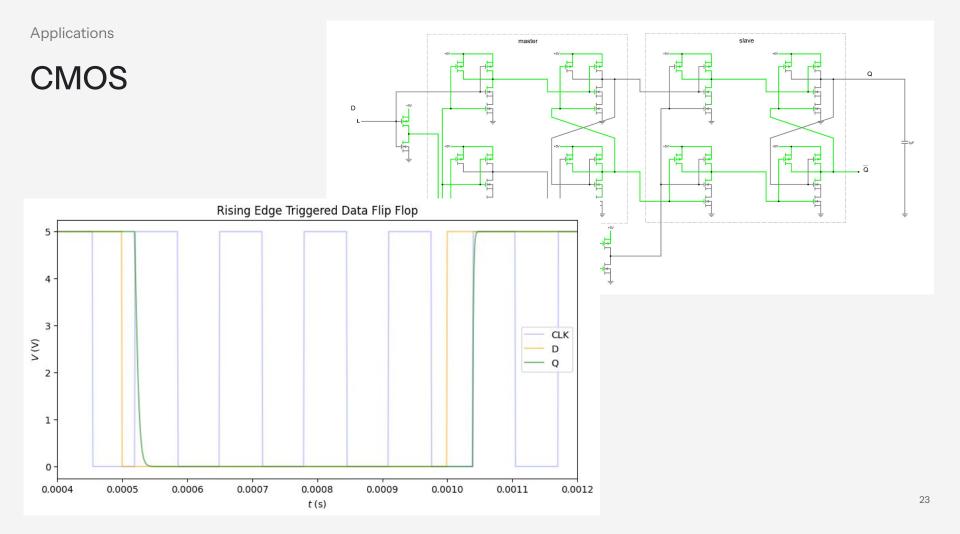

Applications

#### **4th-Order Filter**

Applications

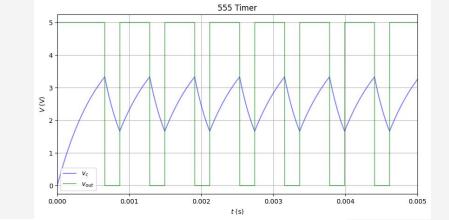

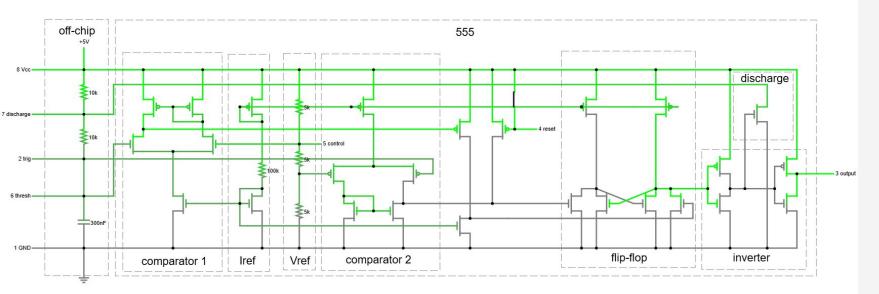

# 555 Hybrid Chip

Applications

### **Failure Modes**

# Acknowledgements

Stephen Edwards

Peiran Wang

https://www.h-schmidt.net/FloatConverter/IEEE754.html