#### **CSEE W3827**

# Fundamentals of Computer Systems Homework Assignment 2

### **SOLUTION**

Prof. Stephen A. Edwards

Columbia University

Due June 18th, 2015 at 5:30 PM

Write your name and UNI on your solutions

Show your work for each problem; we are more interested in how you get the answer than whether you get the right answer.

You may use Logisim to draw your circuits. We also suggest you use Logisim to verify them.

1. (20 pts.) A sequential circuit with two D flip-flops  $S_0$  and  $S_1$ , two inputs X and Y, and one output Z behaves according to these equations:

$$S_0' = \overline{X}Y + XS_0$$

$S_1' = XS_1 + \overline{X}S_0$   $Z = XS_0$

- (a) Draw the corresponding circuit. Label each of the signals mentioned above.

- (b) Derive the state table (next state and output as a function of present state and input).

- (c) Draw the corresponding bubble-and-arc diagram.

## Circuit 1(a) XS1 !XSO XS0 X x1 $S_0$ !XY

Y x 1

| Table 1: State Table |       |   |    |   |         |   |              |

|----------------------|-------|---|----|---|---------|---|--------------|

|                      | S1 S0 |   | ΧY |   | S1' S0' |   | $\mathbf{Z}$ |

|                      | 0     | 0 | 0  | 0 | 0       | 0 | 0            |

|                      | 0     | 0 | 0  | 1 | 0       | 1 | 0            |

|                      | 0     | 0 | 1  | 0 | 0       | 0 | 0            |

|                      | 0     | 0 | 1  | 1 | 0       | 0 | 0            |

|                      | 0     | 1 | 0  | 0 | 1       | 0 | 0            |

|                      | 0     | 1 | 0  | 1 | 1       | 1 | 0            |

|                      | 0     | 1 | 1  | 0 | 0       | 1 | 1            |

|                      | 0     | 1 | 1  | 1 | 0       | 1 | 1            |

|                      | 1     | 0 | 0  | 0 | 0       | 0 | 0            |

|                      | 1     | 0 | 0  | 1 | 0       | 1 | 0            |

|                      | 1     | 0 | 1  | 0 | 1       | 0 | 0            |

|                      | 1     | 0 | 1  | 1 | 1       | 0 | 0            |

|                      | 1     | 1 | 0  | 0 | 1       | 0 | 0            |

|                      | 1     | 1 | 0  | 1 | 1       | 1 | 0            |

|                      | 1     | 1 | 1  | 0 | 1       | 1 | 1            |

|                      | 1     | 1 | 1  | 1 | 1       | 1 | 1            |

| •                    |       |   |    |   |         |   |              |

2. (20 pts.) Determine the logic for a synchronous 4-bit counter that counts  $0,1,\ldots,9,10,11,0,1,\ldots$  in binary. It should have four outputs  $Q_1,\,Q_2,\,Q_4,\,Q_8$ , (the subscripts indicate the value of each bit) each

driven directly by a flip-flop.

Write Boolean expressions of the form  $D_i = Q_i \oplus (\cdots)$  for each flip-flop's input. ( $\oplus$  is XOR) You do not have to submit a schematic

$$\begin{array}{lll} 0000 \\ 0001 \\ 0010 \\ 0011 \\ 0011 \\ \end{array} \qquad \begin{array}{lll} D_1 = Q_1 \, \oplus \, 1 \\ 0\\ 0011 \\ \end{array} \qquad \begin{array}{lll} D_2 = Q_2 \, \oplus \, Q_1 \\ 0\\ 1000 \\ 0101 \\ 0110 \\ \end{array} \qquad \begin{array}{lll} D_4 = Q_4 \, \oplus \, (\sim Q_8 Q_2 Q_1) \\ 0\\ 0111 \\ 1000 \\ 1001 \\ \end{array} \qquad \begin{array}{lll} D_8 = Q_8 \, \oplus \, (Q_4 Q_2 Q_1 + Q_8 Q_2 Q_1) \\ \end{array} \qquad \begin{array}{lll} An \ alternate \ solution \ for \ D_8 \ is: \\ D_8 = Q_8 \, \oplus \, (Q_4 Q_2 Q_1 + Q_8 \sim Q_4 Q_2 Q_1) \\ \end{array}$$

for this problem.

1011

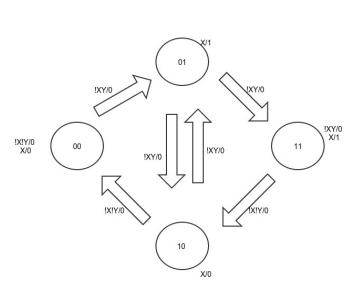

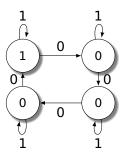

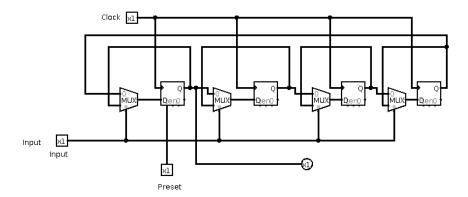

3. (20 pts.) Using just four flip-flops and four two-input muxes, draw a circuit for the following Moore state machine with a single input and single output. Use a one-hot encoding. Each state is labeled with the value of the output.

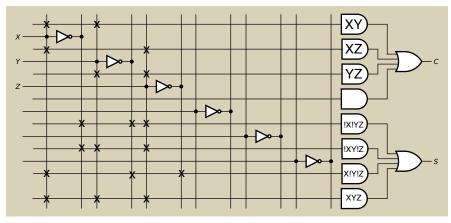

4. (20 pts.) Show how to implement a full-carry adder using the PLA drawn below.

Hint: write the expressions for S and C in sum-of-products form then draw crosses to indicate connections on the AND plane.

$$C = YZ + XZ + XY$$

$$S = !X!YZ + !XY!Z + X!Y!Z + XYZ$$

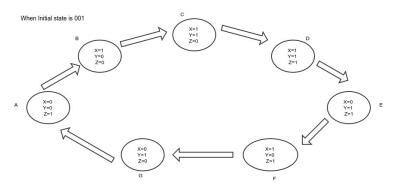

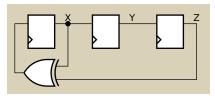

5. (20 pts.) The circuit below is called a linear-feedback shift register. Draw a bubble-and-arc diagram representing its behavior. Start from both the state X = 0, Y = 0, Z = 1 and the all-zeros state.

#### Solution to Problem 5