# Serial Communications CSEE W4840

Prof. Stephen A. Edwards

**Columbia University**

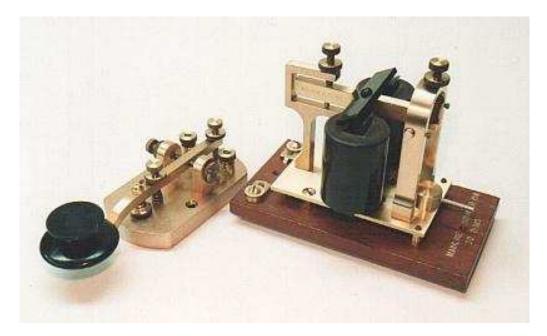

# **Early Serial Communication**

#### Morse code key

|      |                   | 200 | *   |

|------|-------------------|-----|-----|

| Lett | ers               |     | 1   |

| Α    | •—                |     | 1   |

| В    |                   | ,   | 2   |

| C    | -•-•              |     | 3   |

| D    | •                 |     | 4   |

| E    | •                 |     | 5   |

| F    | •••               |     | 6   |

| G    |                   |     | - 5 |

| H    |                   |     | 8   |

| I    | ••                |     | 9   |

| J    | •                 |     | (   |

| K    | -•-               |     |     |

| L    |                   |     |     |

| M    | <del></del>       |     |     |

| N    | - •               |     |     |

| 0    |                   |     |     |

| P    | ••                |     |     |

| Q    |                   |     |     |

| R    | • •               |     |     |

| S    |                   |     |     |

| T    | _                 |     |     |

| U    | • • —             |     |     |

| V    | • • • —           |     |     |

| W    | •                 |     |     |

| X    | $- \cdot \cdot -$ |     |     |

| Y    | $- \cdot$         |     |     |

| **   |                   |     |     |

| Nun | nbers     |

|-----|-----------|

| 1   | •         |

| 2   | • •       |

| 3   | •••       |

| 4   | • • • • — |

| 5   |           |

| 5   |           |

| 7   | ••        |

| 8   | •         |

| 9   | •         |

| 0   |           |

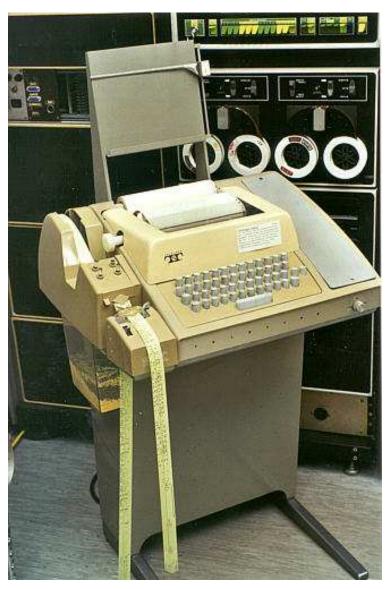

# **Later Serial Communication**

**Data Terminal Equipment**

Data

Communications

Equipment

#### **RS-232**

Defined in early 1960s Serial, Asynchronous, Full-duplex, Voltage-based, point-to-point, 100 ft+ cables

$$\begin{pmatrix} -3V \\ MARK = 1 \\ -12V \end{pmatrix}$$

# **RS-232 Signals**

#### Signal DB-9 DTE ... Meaning

|     | pin | DCE               |                                 |

|-----|-----|-------------------|---------------------------------|

| RxD | 2   | <del></del>       | Data received by DTE            |

| TxD | 3   | $\longrightarrow$ | Data sent by DTE                |

| SG  | 5   |                   | Ground                          |

| DSR | 6   | $\leftarrow$      | Data Set Ready (I'm alive)      |

| DTR | 4   | $\longrightarrow$ | Data Terminal Ready (me, too)   |

| DCD | 1   | <del>&lt;</del>   | Carrier Detect (hear a carrier) |

| RTS | 7   | $\longrightarrow$ | Request To Send (Yo?)           |

| CTS | 8   | $\leftarrow$      | Clear To Send (Yo!)             |

| RI  | 9   | $\leftarrow$      | Ring Indicator                  |

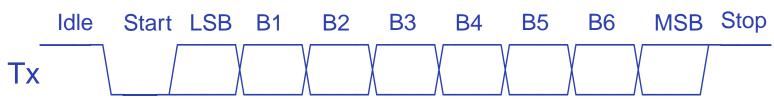

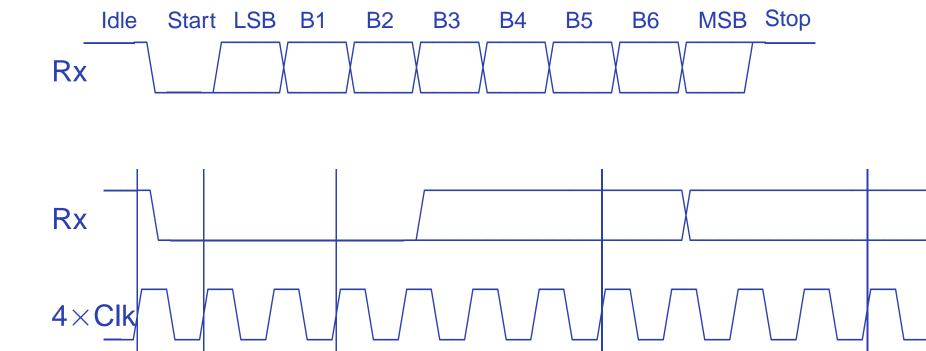

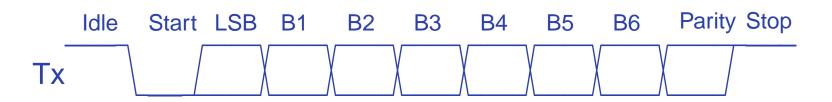

# Receiving RS-232

Start

Sample

Most UARTs actually use 16× clocks

Sample

Sample

### **Variants**

Parity bit: (Even = true when even number of 1s)

Two stop bits:

#### **Baud Rate**

Baud: bits per second

**Baud Application**

110 ASR-33 Teletype

300 Early acoustic modems

1200 Direct-coupled modems c. 1980

2400 Modems c. 1990

9600 Serial terminals

19200

38400 Typical maximum

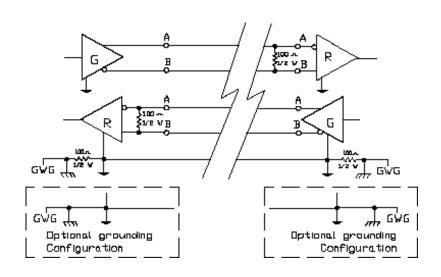

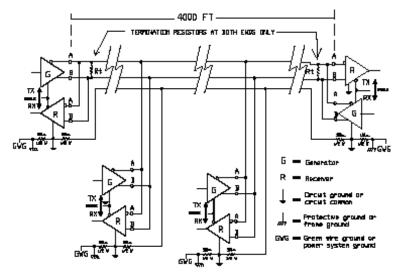

# **Physical Variants**

Connectors: DB-25, DB-9, Mini DIN-8

RS-422: Differential signaling

RS-485: Bus-like

#### **OPB UART Lite**

Serial port peripheral for the Microblaze

Full duplex operation

16-character transmit and receive FIFOs

Parameters that can be set at build time:

Parameter Value

Base Address 0xFEFF0100

High Address 0xFEFF01FF

Baud Rate 9600

Bits per frame 8

Parity None

# **OPB UART Lite Registers**

| Address    | Role                              |

|------------|-----------------------------------|

| 0xFEFF0100 | Read characters from Receive FIFO |

| 0xFEFF0104 | Write characters to Receive FIFO  |

| 0xFEFF0108 | Status register (read only)       |

| 0xFEFF010C | Control register (write only)     |

# Status and Control Registers

| Bit | Status              | Control           |  |

|-----|---------------------|-------------------|--|

| 24  | Parity Error        | _                 |  |

| 25  | Framing Error       | _                 |  |

| 26  | Overrun Error       | -                 |  |

| 27  | Interrupts Enabled  | Enable Interrupts |  |

| 28  | Tx buffer full      | -                 |  |

| 29  | Tx buffer empty     | -                 |  |

| 30  | Rx buffer full      | Clear Rx buffer   |  |

| 31  | Rx buffer non-empty | Clear Tx buffer   |  |

Non-empty Rx buffer or emptying of Tx buffer generates an interrupt.

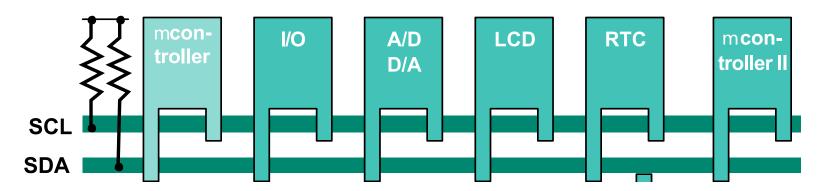

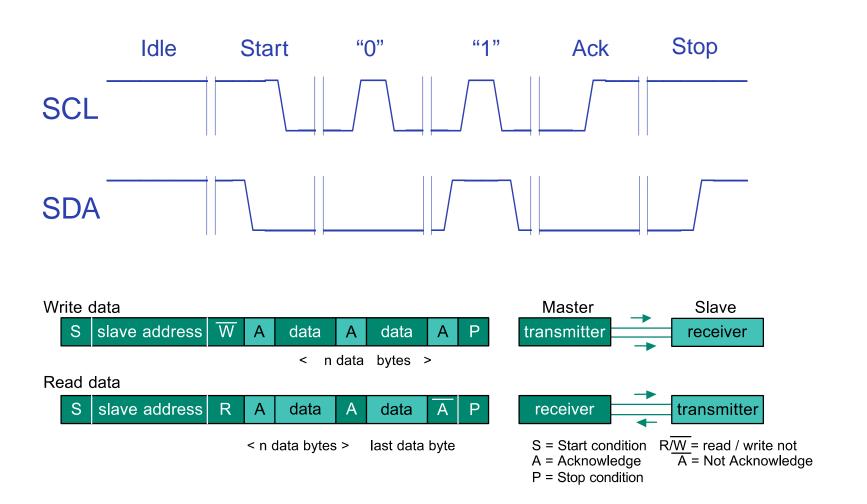

# The I<sup>2</sup>C Bus

Philips invented the Inter-IC bus c. 1980 as a very cheap way to communicate slowly among chips

E.g., good for setting control registers

100, 400, and 3400 kHz bitrates

SCL: Clock, generated by a single master

SDA: Data, controlled by either master or slaves

# I<sup>2</sup>C Bus Transaction

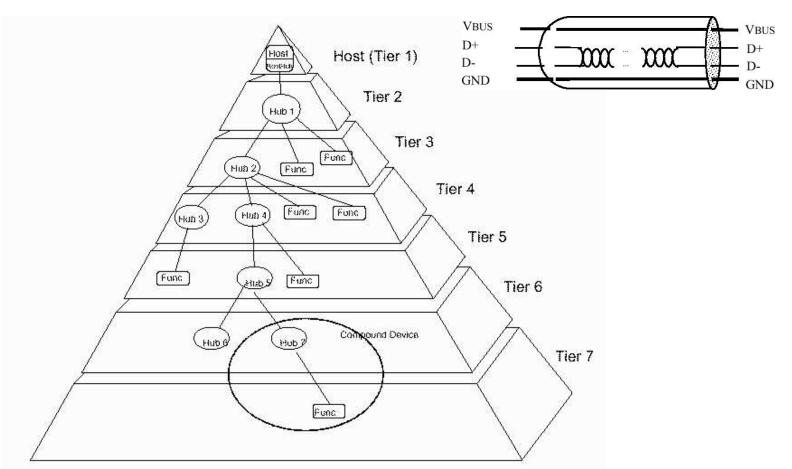

#### **USB: Universal Serial Bus**

1.5 Mbps, 12 Mbps, and 480 Mbps (USB 2.0)Point-to-point, differential, twisted pair3–5m maximum cable length

#### **USB Connectors**

#### Series "A" Connectors

Series "A" plugs are always oriented upstream towards the Host System

"A" Plugs (From the USB Device)

"A" Receptacles

(Downstream Output

from the USB Host or

Hub)

#### Series "B" Connectors

Series "B" plugs are always oriented downstream towards the USB Device

"B" Plugs (From the Host System)

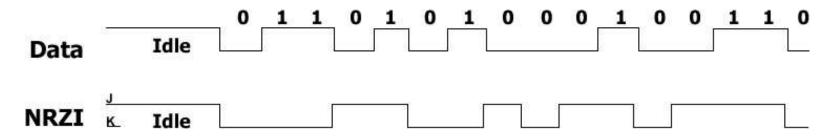

# **USB** signaling

NRZI: 0 = toggle, 1 = no change

Bit stuffing: 0 automatically inserted after six consecutive 1s

Each packet prefixed by a SYNC field: 3 0s followed by two 1s

Low- vs. full-speed devices identified by different pull-ups on D+/D- lines

#### **USB Packets**

Always start with SYNC

Then 4-bit type, 4-bit type complemented

2 bits distinguish Token, Data, Handshake, and Special, other two bits select sub-types

Then data, depending on packet type

Data checked using a CRC

Addresses (1-128) assigned by bus master, each with 16 possible endpoints

#### **USB Bus Protocol**

Polled bus: host initiates all transfers.

Most transactions involve three packets:

- "Token" packet from host requesting data

- Data packet from target

- Acknowledge from host

Supports both streams of bytes and structured messages (e.g., control changes).

# **USB Data Flow Types**

- Control

For configuration, etc.

- Bulk Data

Arbitrary data stream: bursty

- Interrupt Data

Timely, reliable delivery of data. Usually events.

- Isochronous Data

For streaming real-time transfer: prenegotiated bandwidth and latency

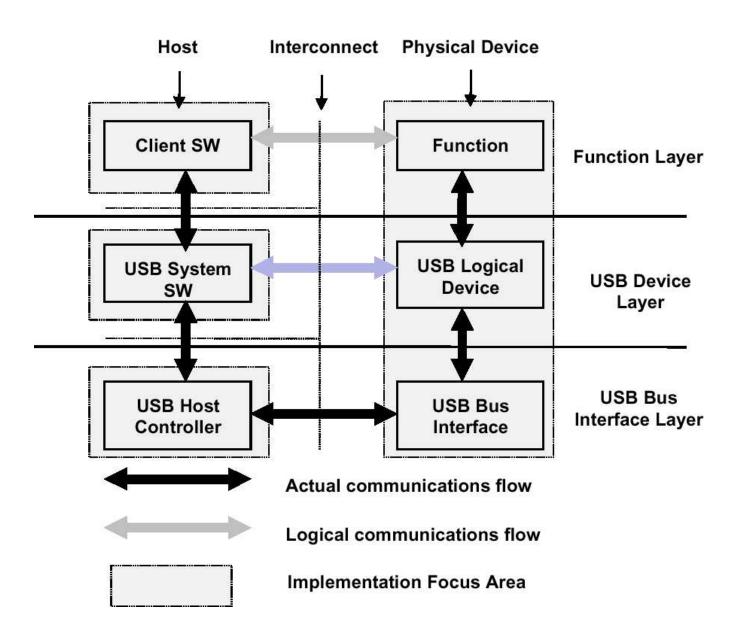

# Layered Architecture

#### **USB: Flash Card Device**

```

Bus 001 Device 002: ID 05e3:0760 Genesys Logic, Inc.

bcdUSB

2.00

bMaxPacketSize0

64

idVendor

0x05e3 Genesys Logic, Inc.

idProduct

0 \times 0760

bcdDevice

1.14

iManufacturer

2 Genesys

3 Flash Reader

iProduct

iSerial

4 002364

Configuration Descriptor:

bNumInterfaces

300mA

MaxPower

Interface Descriptor:

bNumEndpoints

bInterfaceClass

8 Mass Storage

bInterfaceSubClass

6 SCSI

bInterfaceProtocol

80 Bulk (Zip)

Endpoint Descriptor:

bEndpointAddress

0x81

EP 1 IN

bmAttributes

Transfer Type

Bulk

Synch Type

none

wMaxPacketSize

64

Endpoint Descriptor:

bLength

bDescriptorType

bEndpointAddress

0x02

EP 2 OUT

bmAttributes

Transfer Type

Bulk

Synch Type

none

wMaxPacketSize

64

Language IDs: (length=4)

0409 English(US)

```

#### **USB: Mouse Device**

```

Bus 002 Device 002: ID 04b4:0001 Cypress Semiconductor Mouse

Device Descriptor:

bcdUSB

1.00

idVendor

0x04b4 Cypress Semiconductor

idProduct

0 \times 0001 Mouse

bcdDevice

4.90

iManufacturer

1 Adomax Sem.

2 USB Mouse

iProduct

iSerial

Configuration Descriptor:

bNumInterfaces

bmAttributes

0xa0

Remote Wakeup

100mA

MaxPower

Interface Descriptor:

bNumEndpoints

bInterfaceClass

3 Human Interface Devices

bInterfaceSubClass

1 Boot Interface Subclass

bInterfaceProtocol

2 Mouse

iInterface

5 EndPoint1 Interrupt Pipe

HID Device Descriptor:

bDescriptorType

34 Report

wDescriptorLength

52

Endpoint Descriptor:

bEndpointAddress

0x81

EP 1 IN

bmAttributes

Transfer Type

Interrupt

Synch Type

none

wMaxPacketSize

10

bInterval

Language IDs: (length=4)

0409 English(US)

```

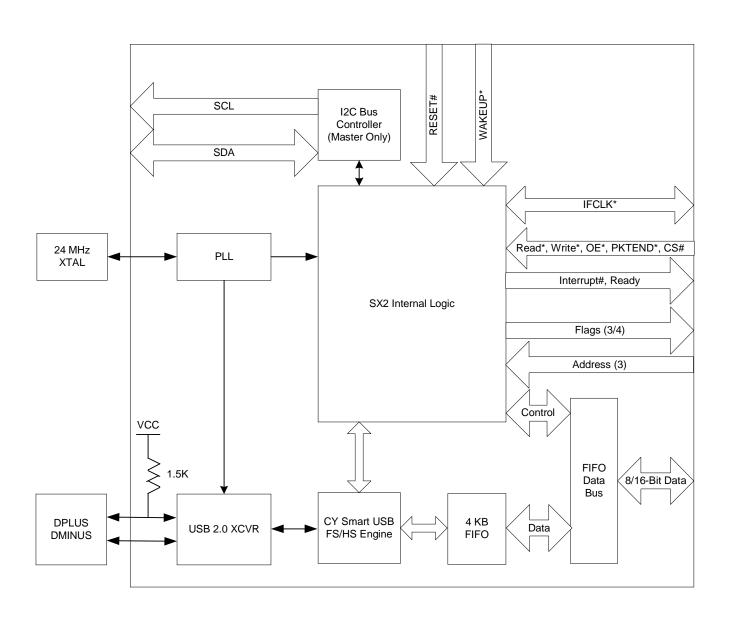

# The CY7C68001 USB interface

## The CY7C68001 USB interface

Operates as a peripheral (i.e., not a host)

Operates at 12 or 480 Mbps speeds

Control endpoint 0

Four other user-configurable endpoints

4 kB FIFO buffer

500 bytes of descriptor RAM (Vendor, Product)

I<sup>2</sup>C bus interface for configuration from EEPROM

(Unused on the XSB board—processor must configure)

## CY7C68001 software interface

Five memory locations: one for each FIFO, one for control registers

Internal registers written by first applying address to control register, then reading or writing data to control register.

33 different configuration registers, including 500-byte descriptor "register"