### **Processors, FPGAs, and ASICs CSEE W4840**

Prof. Stephen A. Edwards

Columbia University

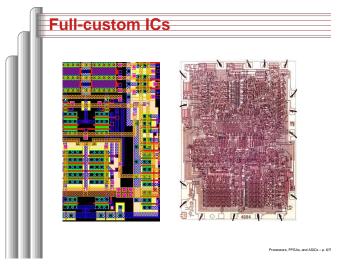

### **Spectrum of IC choices** Flexibility You choose polygons (Intel) Full Custom circuit (Sony) **ASIC** Gate Array wires logic network **FPGA** logic function PLD GP Processor program (e.g., Pentium) SP Processor program (e.g., DSP) Multifunction settings (e.g., Ethernet) Fixed-function part number (e.g., 74LS00)

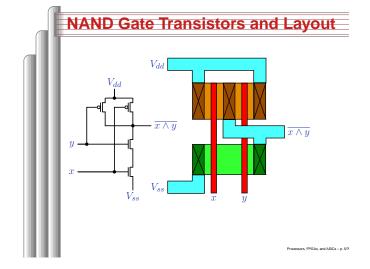

# **NMOS Transistor Cross Section**

### **Inverter Transistors and Layout**

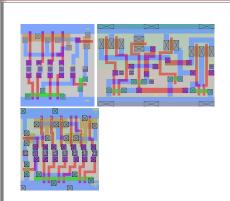

### Standard Cell ASICs

### Standard Cell ASICs

### **Channeled Gate Arrays**

### **Sea-of-Gates Gate Arrays**

## FPGAs: Floorplan

**FPGAs: Routing**

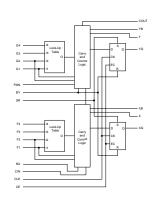

### FPGAs: CLB

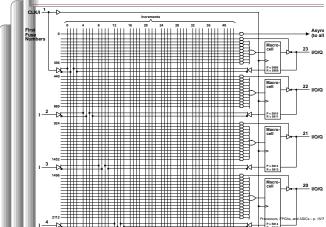

### PLAs/CPLDs: The 22v10

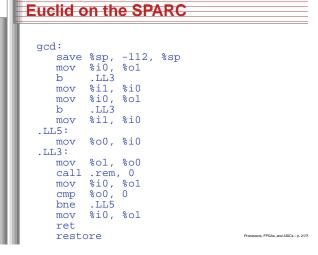

### **Example: Euclid's Algorithm**

```

int gcd(int m, int n)

int r;

while ((r = m % n) != 0) {

m = ni

n = r_i

return n;

```

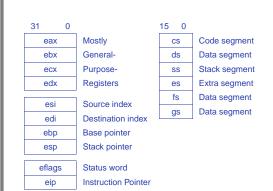

### i386 Programmer's Model

### **Euclid on the i386**

```

gcd: pushl %ebp

movl %esp,%ebp

pushl %ebx

movl 8(%ebp),%eax

movl 12(%ebp),%ecx

.L6

jmp

%ecx,%eax

.L4: movl

movl %ebx,%ecx

.L6: cltd

idivl %ecx

movl %edx, %ebx

test1 %edx, %edx

.L4

jne

movl

%ecx,%eax

-4(%ebp),%ebx

movl

leave

ret

```

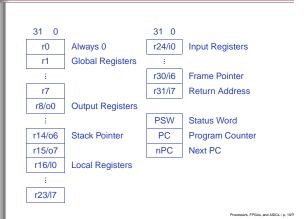

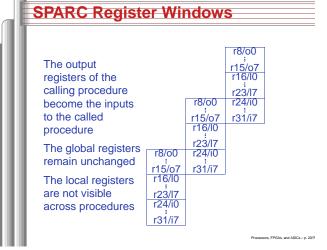

SPARC Programmer's Model

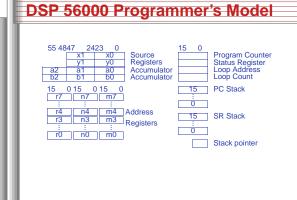

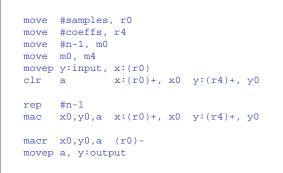

FIR Filter in 56000

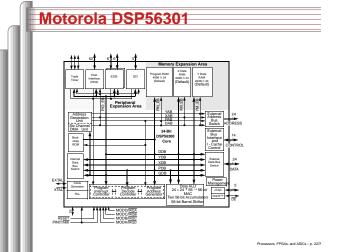

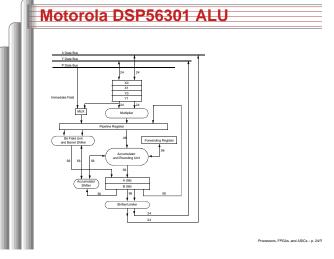

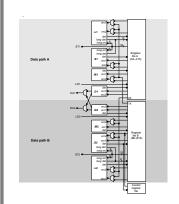

### Motorola DSP56301 AGU Low Address ALU XAB YAB PAB Triple Multiplexer R0 R4 R1 R5 R2 R6 R3 R7 R3 R7 Address ALU M4 N4 M5 N5 M6 N6 N7 N7

### FIR in One 'C6 Assembly Instruction

```

Load a halfword (16 bits)

Do this on unit D1

FIRLOOP:

LDH .D1 *A1++, A2 ; Fetch next sample

LDH .D2 *B1++, B2 ; Fetch next coeff.

[B0] SUB .L2 B0, 1, B0 ; Decrement count

[B0] B .S2 FIRLOOP ; Branch if non-zero

MPY .M1X A2, B2, A3 ; Sample × Coeff.

ADD .L1 A4, A3, A4 ; Accumulate result

Use the cross path

Predicated instruction (only if B0 non-zero)

Run these instruction in parallel

```

Processors EDGAs and ASICs - p. 29

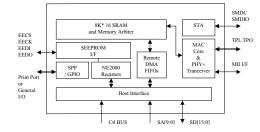

### **AX88796 Ethernet Controller**

Processors EDGAs and ASICs

### **Ethernet Controller Registers**

Command Register Command Register (CR) Page Start Register (PSTART) (PSTART) Page Stop Register Page Stop Register (PSTOP) (PSTOP) (BNRY) (BNRY) Transmit Page Start Address Transmit Status Register Transmit Byte Count Register 0 (TBCR0) (NCR) Current Page Register Fransmit Byte Count Register 1 (CPR) TBCR1) Interrupt Status Register Interrupt Status Register (CRDA0) RSAR0) Current Remote DMA Address Remote Start Address Register 1 (CRDA1) (RSAR1) Remote Byte Count 0 ( RBCR0 ) 0AH (RBCR1) Receive Status Register Receive Configuration Register.

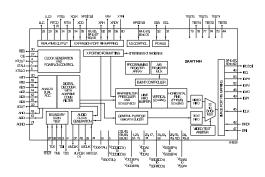

### Philips SAA7114H Video Decoder

Processors. FPGAs, and ASICs = p. 31/7

### SAA7114H Registers, page 1 of 7 (!)

| REGISTERFUNCTION                    | ADDR.<br>(HEX) | D7             | D6     | D5     | D4             | D3     | D2     | D1     | D0             |

|-------------------------------------|----------------|----------------|--------|--------|----------------|--------|--------|--------|----------------|

| Chip version: register 00H          |                |                |        |        |                | •      |        |        |                |

| Chip version (read only)            | 00             | ID07           | E006   | ID05   | ID04           | -      | -      | -      | -              |

| Video decoder: registers 01H t      | b 2FH          |                | •      |        | •              | •      |        |        |                |

| FRONTIEND PART: REGISTERS 01H       | то 05Н         |                |        |        |                |        |        |        |                |

| Horizontal increment delay          | 01             | (9)            | (0)    | (0)    | (1)            | DE13   | IDBL2  | IDEL1  | IDEL()         |

| Analog input control 1              | 02             | FUSE1          | FUSEO  | GUDL1  | GUDLO          | MCDE3  | MODE2  | MODE1  | MODE0          |

| Analog input control 2              | 03             | (1)            | HLNRS  | VBSL   | WPOFF          | HOLDG  | GAFIX  | G4428  | GAM8           |

| Analog input control 3              | 04             | GA117          | GAM6   | GAM5   | GAI14          | GAItt3 | GN12   | GAI11  | GAN10          |

| Analog input control 4              | 05             | GA <b>1</b> 27 | GAL26  | GA125  | GA <b>1</b> 24 | GA123  | GA122  | GAI21  | GA <b>12</b> 0 |

| DECCORR PART: REGISTERS 06H T       | o2FH           |                |        |        |                |        |        |        |                |

| Horizontallsyncstart                | 06             | HS87           | HSB6   | HSB5   | HSB4           | HSB3   | HSB2   | HSB1   | HSBO           |

| Horizontalisync stop                | 07             | HSS7           | HS96   | HBS5   | HSS4           | HSS3   | HSS2   | HSS1   | HSS0           |

| Synccontrol                         | 08             | AUFD           | FSEL.  | FOET   | HTC1           | HTC0   | HPLL   | VNOH   | VNOto          |

| Luminance control                   | 09             | BYPS           | YOOMB  | LDEL   | LUBW           | LUFI3  | LUFI2  | ЩЯtt   | LUFI0          |

| Luminance brightness control        | 0A             | DBRI7          | DBR16  | DBRIS  | DBR#4          | DBRIB  | DBRM2  | DERM   | DBRID          |

| Luminance contrast control          | 08             | DCGN7          | D000N6 | DCON5  | DCC0N4         | DOONS  | DOON2  | DCONI  | 2020           |

| Orrominance saturation control      | OC.            | DSAT7          | DSAT6  | DSAT6  | DSAT4          | DSAT3  | DSAT2  | DSAT1  | DSATO          |

| Chrominance hue control             | 00             | HJEC7          | HJE08  | HLEC5  | HJEC4          | HUEC3  | HUEC2  | HJEC1  | HJE00          |

| Chrominance control 1               | Œ              | COTO           | CSTD2  | CSTD1  | CSTDO          | DCVF   | FCTC   | (0)    | CCCMB          |

| Chrominance gain control            | 0F             | ACGC           | CGAIN6 | CGAIN5 | CGAIN4         | OGAINS | OGAIN2 | CGAINI | CGAINO         |

| Orrominance control 2               | 10             | OFFU1          | OFFU0  | OFFV1  | OFFV0          | CHBW   | LCBW2  | LCBW1  | LCBM0          |

| Mode/dellay control                 | 11             | 0000           | RTP1   | HDBL1  | HDBL0          | RTPO   | YDEL2  | YDEL1  | YDBLO          |

| RT signal control                   | 12             | RTSE13         | RTSE12 | RTSE11 | RTSE10         | RTSE03 | RTSE02 | RTSE01 | RTSECO         |

| RTX-portaulputaonitol               | 13             | FITCE          | XRHS   | XFMS1  | XFMS0          | HLSEL. | OFTS2  | OFTS1  | OFTS0          |

| Analog/AEC/compatibility<br>control | 14             | CW69           | UPTCV  | AOBL1  | AOSL0          | XIOUTE | OLDSB  | AP(K1  | APOKO          |

| VGATE start, FID change             | 15             | VSTA7          | VSTA6  | VSTA5  | VSTA4          | VSTAG  | VSTA2  | VSTA1  | VSTA0          |

| VGATEstop                           | 16             | VST07          | VSTO6  | VST05  | VSTO4          | VSTC3  | VSTO2  | VSTO1  | VSTCO          |

| Miscellaneous/VGATE MSBs            | 17             | LLCE           | LLC2E  | (10    | (1)            | (1)    | VGPS   | VSTO8  | VSTA8          |

Processors, FPGAs, and ASICs - p. 32

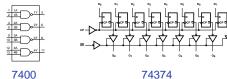

### Fixed-function: The 7400 series

(RCR)

Quad NAND Gate

Octal D Flip-Flop

ocessors, FPGAs, and ASICs - p. 33/?