The release of ESP is the results of years of research with the SLD group at Columbia University, department of Computer Science. This project combines a flexible system architecture with a design methodology to overtake the challenges of heterogeneous system integration.

Thanks to ESP, engineers can focus on the design of specialized accelerators that are key to improving the performance of their target applications and leave the integration process into a complete embedded system to ESP.

An instance of ESP can have one ore more processor cores, chosen between the ETH Zurich Ariane RISC-V 64 bits core and the Cobham Gaisler AB Leon3 SPARC 32-bits core.

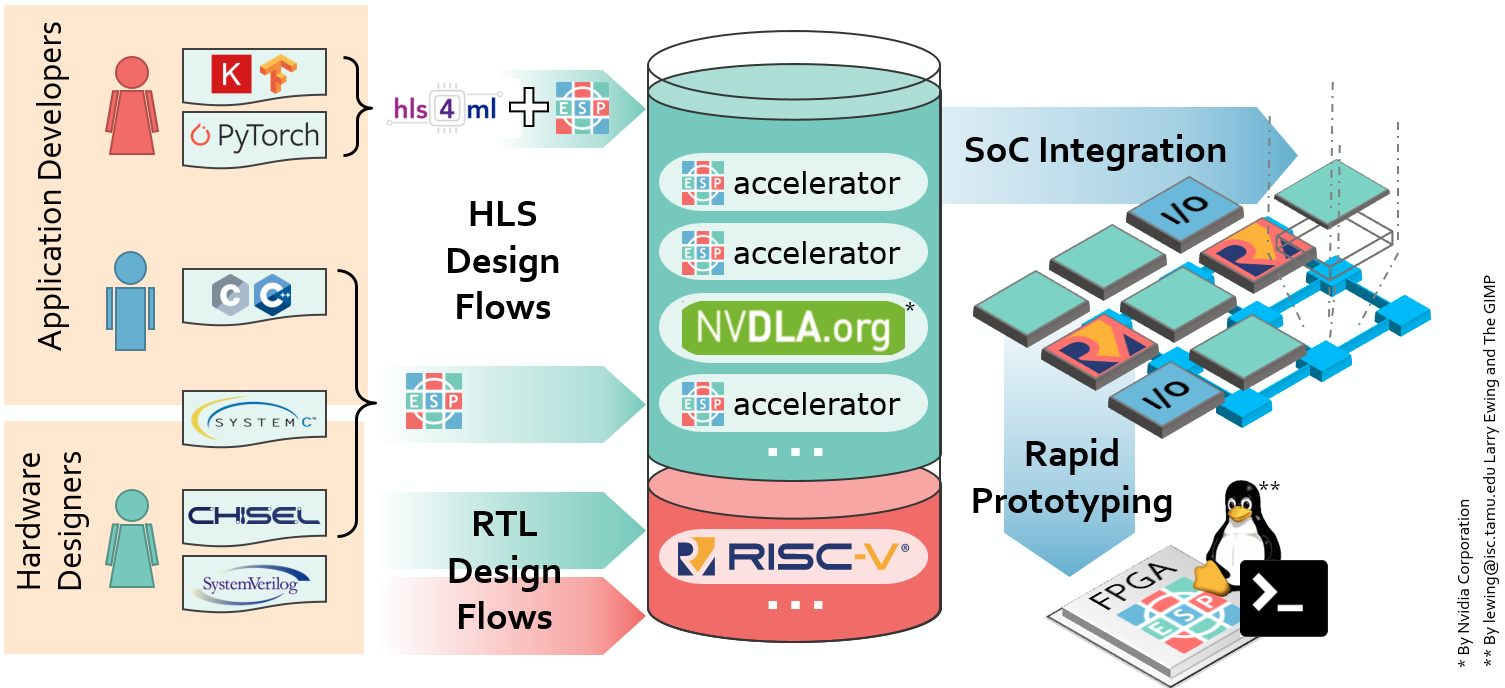

Currently supported specification entry points for accelerators are SystemC, Chisel and RTL, but we will be soon releasing examples of accelerators design flows based on C and machine-learning API, such as Keras and PyTorch.