# Scanning the Technology:

# Applications of Asynchronous Circuits

C. H. (Kees) van Berkel, Mark B. Josephs, and Steven M. Nowick

Abstract— A comparison with synchronous circuits suggests four opportunities for the application of asynchronous circuits: high performance, low power, improved noise and EMC properties, and a natural match with heterogeneous system timing. In this overview article each opportunity is reviewed in some detail, illustrated by examples, compared with synchronous alternatives, and accompanied by numerous pointers to the literature. Conditions for applying asynchronous circuit technology, such as the existence and availability of CAD tools, circuit libraries, and effective test approaches, are discussed briefly. Asynchronous circuits do offer advantages for many applications, and their design methods and tools are now starting to become mature.

Keywords—Asynchronous circuits, asynchronous systems, high performance, low power, low noise, heterogeneous timing, CAD tools, testability.

# I. Introduction

Today, the semiconductor industry is giving serious consideration to the adoption of asynchronous circuit technology. Up until now, asynchronous circuits have been applied commercially only as small subcircuits, often as peripherals to controllers. Examples include counters, timers, wake-up circuits, arbiters, interrupt controllers, fifos, bus controllers, and interfaces (e.g. RS-232, SCSI, UART). The need for such asynchronous circuits stems largely from intrinsically asynchronous specifications.

During the last decade there has been a revival in research on asynchronous circuits [1], [2]. Emphasis is now shifting from asynchronous-in-the-small to asynchronous VLSI circuits and systems. Asynchronous VLSI is now progressing from a fashionable academic research topic to a viable solution to a number of digital VLSI design challenges. A first, entirely asynchronous IC has recently appeared on the market (Section IV).

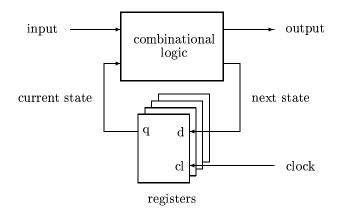

The added value of asynchronous circuit technology can best be understood by reviewing the key properties of synchronous circuits. A synchronous circuit in its simplest form is shown in Figure 1. The current state of the circuit is stored in an array of registers. The next state is computed from the current state and inputs by a combinational logic circuit. When the clock signal makes a transition, say

This work was supported by the European Commission under Working Group 21949 ACiD-WG as part of the ESPRIT Fourth Framework.

This work was also supported by the National Science Foundation under Grant nos. MIP-9501880 and CCR-97-34803.

C.H. van Berkel is with Philips Research Laboratories, 5656 AA Eindhoven, The Netherlands, and with Eindhoven University of Technology, 5600 MB Eindhoven, The Netherlands.

M.B. Josephs is with the Centre for Concurrent Systems and VLSI, School of CISM, South Bank University, London SE1 0AA, England. S.M. Nowick is with the Department of Computer Science, Columbia University, New York NY 10027 USA.

Fig. 1. Synchronous circuit.

from low to high, the registers are *enabled*, and the next state is copied into the registers, thus becoming the current state. Each register bit generally comprises two latches, usually cascaded into a master-slave flip-flop. In such a synchronous circuit:

- 1. The longest path in the combinational logic determines the minimum clock period, whereas during a typical clock cycle the circuit may in fact become quiescent well before the next clock signal.

- 2. Each register dissipates energy during each clock cycle, regardless of the extent of the change in state. If dynamic logic is used, the combinational logic dissipates clock power during each clock cycle as well.

- 3. The clock modulates the overall supply current, causing peaks in power-supply noise and in electromagnetic emission to occur at the clock frequency and higher harmonics thereof.

- 4. All functional sub-modules operate in lock-step, a requirement that seems increasingly at odds with the growing significance of interconnect delays and the heterogeneous nature of systems-on-a-chip architecture

The corresponding *opportunities* for application of asynchronous circuits are:

- 1. high performance (Section II),

- 2. low power dissipation (Section III),

- 3. low noise and low electro-magnetic emission (Section IV), and

- 4. a good match with heterogeneous system timing (Section V).

Section VI addresses design tools for asynchronous circuits, cell libraries, and testability issues. For an introduction to the modeling and design of asynchronous circuits the reader is referred to [3] in this issue.

#### II. ASYNCHRONOUS FOR HIGH PERFORMANCE

In an asynchronous circuit the next computation step can start immediately after the previous step has completed: there is no need to wait for a transition of the clock signal. This leads, potentially, to a fundamental performance advantage for asynchronous circuits, an advantage that increases with the variability in delays associated with these computation steps. However, part of this advantage is canceled by the overhead required to detect the completion of a step. Furthermore, it may be difficult to translate local timing variability into a global system performance advantage. In this section we explore these data-dependencies of delays, and present a number of successful demonstrations of asynchronous performance advantages.

### Data-dependent delays

The delay of the combinational logic circuit in Figure 1 depends on the current state and the value of the primary inputs. The worst-case delay, plus some margin for flip-flop delays and clock skew, is then a lower bound for the clock period of a synchronous circuit. Thus, the actual delay is always less (and sometimes much less) than the clock period.

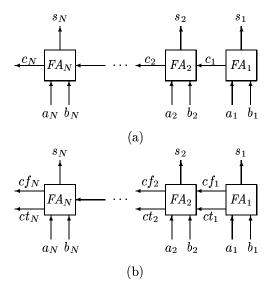

Fig. 2. N-bit ripple-carry adder (a) and a self-timed version (b).

A simple example is an N-bit ripple-carry adder (Figure 2). The worst-case delay occurs when 1 is added to  $2^N - 1$ . Then the carry ripples from  $FA_1$  to  $FA_N$ . In the best case there is no carry ripple at all, as, for example, when adding 1 to 0. Assuming random inputs, the average length of the longest carry-propagation chain is bounded by  $\log_2 N$  [4]<sup>1</sup>. For a 32-bit wide ripple-carry adder the average length is therefore 5, but the clock period must be 6 times longer! On the other hand, the average length determines the average-case delay of an asynchronous ripple-carry adder, which we consider next.

In an asynchronous circuit this variation in delays can be exploited by detecting the actual completion of the addition. Most practical solutions use double-rail encoding of the carry signal (Figure 2(b)); the addition has completed when all internal carry-signals have been computed [6], [5]. That is, when each pair  $(cf_i, ct_i)$  has made a monotonous transition from (0,0) to (0,1) (carry = false) or to (1,0)(carry = true). A variant of this scheme is applied in [7, this issue. Double-rail encoding of the carry signal has also been applied to a carry bypass adder [8]. When inputs and outputs are double-rail encoded as well, the completion can be observed from the outputs of the adder [4], [9]. A quite different technique, with similar objectives, is speculative completion: so-called abort-logic is used to select among a number of fixed delay-lines depending on the input values of a combinational circuit. In [10] this technique is introduced and applied to a carry lookahead adder.

The asynchronous adders discussed above nicely demonstrate how data-dependent delays can be exploited to obtain a superior *average-case* delay compared to the fixed (worst case) delay of the equivalent synchronous adder. This performance advantage is maximal for the ripple-carry adder, and becomes more modest for adder organizations with carry acceleration, such as carry lookahead adders and carry select adders [11].

In some specific applications the large data-dependent variations in delays naturally lead to elegant and efficient asynchronous solutions. For example, Yun et al [8] describe a differential equation solver based on adders and multipliers with superior average-case delays. Benes et al [12] describe a high-speed software decompression engine for embedded processors. The engine exploits the large variations in delays so typical for Huffman decoders. For similar reasons Intel is investigating asynchronous instruction decoders [13]. In [14, this issue] performance benefits are pursued for microprogrammed control organizations.

# Elastic pipelines

In general it is not easy to translate a local asynchronous advantage in average-case performance into a system-level performance advantage. Today's synchronous circuits are heavily pipelined and retimed. Critical paths are nicely balanced and little room is left to obtain an asynchronous benefit. Moreover, an asynchronous benefit of this kind must be balanced against a possible overhead in completion signaling and asynchronous control.

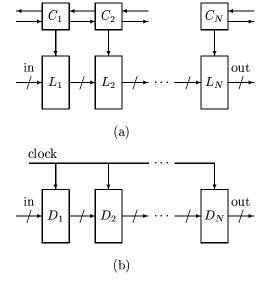

The comparison of a so-called micropipeline and a clocked shift-register is interesting in addressing performance issues. In its most basic form, a micropipeline [15] is an elastic first-in-first-out buffer, constructed as a cascade of identical stages. Each stage consists of a latch L and a controller C, as in Figure 3(a). The controller communicates exclusively with the controllers of the immediately preceding and succeeding stages by means of handshake signaling [4], and controls the state of the data latches (transparent or opaque). Between the request and the next acknowledge phase the corresponding data wires must be kept stable.

<sup>&</sup>lt;sup>1</sup>In practice this average may be somewhat larger, as shown in [5] for an ALU in a microprocessor.

Fig. 3. N-place micropipeline (a) versus an N-place clocked shift register (b).

Maximum throughput of a micropipeline is obtained when it is half full, in which case alternatingly data is transferred from the even stages to the odd stages and from the odd to the even stages. When used as a high-throughput shift-register, the effective capacity of a 2N-place micropipeline is thus reduced to N. One could say that the latches in stage i+1 are used as slave latches to those in stage i.

Work at SUN Research (see [16] in this issue) shows that, with a carefully designed controller circuit, the throughput of a micropipeline can approach that of a synchronous shift register. The number of data latches of a 2N-place micropipeline equals that of an N place shift register (a master latch plus a slave latch per bit). Hence the micropipeline solution is costlier, given the additional control circuitry C.

These additional costs, which can be relatively modest when compared to the costs of a wide data path, buy three interesting — and potentially useful — bonuses. Firstly, when not used at the maximum throughput, the 2N-place micropipeline has a higher capacity, up to 2Nplaces. (When completely full, a new vacancy created at the fifo's output will crawl back to the input). Secondly, the latency per stage is only a small fraction of the cycle time. For example, when a micropipeline is empty, data falls through the (then transparent) latches at a rate of a few gate delays per stage. Thirdly, there is the elasticity of an asynchronous fifo. As a result, it can for example be used when connected to functional units with variable computation times, such as the adder discussed above. Also, micropipeline-like buffers can be used to interface between a data producer and a data consumer operating at different speeds. However, this elasticity also makes it harder in general to analyze the performance of asynchronous circuits, as is done in [17] in this issue.

The self-timed dividers of [18], [19] and the AMULET

microprocessor [20, this issue] are based on micropipelines. Connecting two micropipelines running in opposite directions, and connecting them stage-by-stage in fact results in an innovative concept for a microprocessor architecture [21]. A group at CalTech designed an asynchronous version of the MIPS R3000 [22]. They expect high performance in part by fine-grained pipelining techniques; the number of instructions in the pipeline is dynamic, depending on specific instruction sequences.

# Quantifying circuit performance

Quantifying the performance of synchronous and asynchronous circuits can be tricky [23], and is often a source of confusion. A clocked circuit is usually guaranteed to run at a specified maximum frequency over some range in ambient temperature and supply voltage. Furthermore, there is also a considerable variation between the worst-case and the best-case CMOS process corners. When combined, this results in a safety margin or "derating factor" of about a factor 2. This means that, under typical conditions, many chips could run at about twice the clock frequency specified!

An asynchronous circuit, in contrast, when not delayed by its environment, runs as fast as it goes. It slows down when heated, or when the supply voltage drops. Furthermore, by measuring its performance, one in effect also measures the quality of the CMOS processing. Hence, measured asynchronous performance will vary from one fabrication run to another. Note that when the circuit's specification contains strict requirements on throughputs or response times, the asynchronous performance is subject to the same derating factor as used for synchronous circuits. Beware!

#### III. ASYNCHRONOUS FOR LOW POWER

A quiescent circuit only consumes a leakage current. For most CMOS circuits this leakage current is negligible compared to the dynamic current for that circuit in an active mode. A synchronous circuit is either quiescent (i.e. the clock is turned off) or active entirely (i.e. clock on). An asynchronous circuit, in contrast, only consumes energy when and where active. Any subcircuit is quiescent until activated. After completion of its task, it returns to a quiescent, almost non-dissipating state until a next activation. In this section the potential for low power consumption of asynchronous circuits is reviewed, including a number of successful demonstrations. However, it is not obvious to what extent this advantage is fundamentally asynchronous. Synchronous techniques such as clock gating may achieve similar benefits, but have their limitations.

## Dissipating when and where active

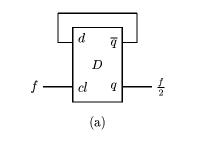

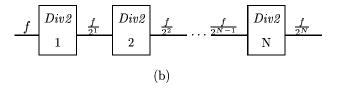

The classic example of a low-power asynchronous circuit is a frequency divider. A D-flip-flop with its inverted output fed back to its input divides an incoming (clock) frequency by two (Figure 4(a)). A cascade of N such divide-by-two elements (Figure 4(b)) divides the incoming frequency by  $2^N$ . The second element runs at only half

Fig. 4. Divide-by-2 element (a) and divide-by- $2^N$  circuit (b).

the rate of the first one and hence dissipates only half the power; the third one dissipates only a quarter, and so on. Hence, the entire asynchronous cascade consumes, over a given period of time, slightly less than twice the power of its head element, independent of N. That is, a fixed power dissipation is obtained. In contrast, a similar synchronous divider would dissipate  $in\ proportion\ to\ N$ . A cascade of 15 such divide-by-two elements is used in watches to convert a 32 kHz crystal clock down to a 1 Hz clock.

Similar asynchronous schemes with similar advantages have been applied to modulo-N counters [24], [25]. A counter with loadable N with these properties is presented in this issue, as part of a low-power asynchronous pager circuit [26].

One way of looking at this low-power property is that only active modules dissipate power. Modules that are not active resort automatically and instantaneously to a standby mode; this is true at arbitrary granularity both in time and in function. A number of examples of how asynchronous techniques help to reduce power consumption are explored in [27].

The potential of asynchronous for low-power depends on the application. For example, in a digital filter where the clock rate equals the data rate, all flip-flops and all combinational circuits are active during each clock cycle. Then little or nothing can be gained by implementing the filter as an asynchronous circuit. However, in many digital-signal processing functions the clock rate exceeds the data (signal) rate by a large factor, sometimes by several orders of magnitude <sup>2</sup>. In such circuits, only a small fraction of registers change state during a clock cycle. Furthermore, this fraction may be highly data dependent.

One application for which asynchronous circuits can save power is Reed-Solomon error correctors operating at audio rates [28], as demonstrated at Philips Research Laboratories. In [29], two different asynchronous realizations of this decoder (single-rail and double-rail) are compared with a synchronous (product) version. The single rail was clearly superior and consumed five times less power than the synchronous version.

A second example is the infrared communications receiver IC designed at Hewlett-Packard/Stanford [30]. The receiver IC draws only leakage current while waiting for incoming data, but can start up as soon as a signal arrives so that it loses no data. Also, most modules operate well below the maximum frequency of operation.

The filter bank for a digital hearing aid was the subject of another successful demonstration, this time by the Technical University of Denmark in cooperation with Oticon Inc. They re-implemented an existing filter bank as a fully asynchronous circuit ([31] and [7] in this issue). The result is a factor five less power consumption.

A fourth application is a pager in which several power-hungry subcircuits were redesigned as asynchronous circuits, as shown later in this issue [26].

#### Low-power processors

Several groups have taken up the gauntlet to explore and exploit this low-power potential for full-fledged programmable processors. In such processors, circuit activity may vary considerably depending on the particular instruction (sequences) and on the occurrence of exceptions. Below, the promising results on four such processors are described: a modern RISC processor, a multi-media processor, a micro-controller, and a programmable digital signal processor.

The University of Manchester designed the AMULET2e, an embedded system chip incorporating a 32-bit ARM-compatible asynchronous core, a cache, and several other system functions [32], [33] [20, this issue]. Quite significant is that the synchronous versions of the ARM are already well known for their low power consumption. Accordingly, the reduction in power per MIPS is modest. However, power consumption in the asynchronous idle mode is a different story. The absence of a high-frequency oscillator and PLL offers a quite unique combination of two features:  $\mu$ W power consumption and instant response to an external interrupt. There is no need to stop an oscillator and a PLL, and to deal with their slow restart and stabilization.

A collaborative effort of Sharp Corporation and the Universities of Osaka and Kochi resulted in a self-timed data-driven multi-media processor [34], [35] [36, this issue]. The processor comprises 8 programmable, data-driven processing elements, connected by an elastic router. Target applications include future digital television receivers. It has an impressive peak performance of 8600 MOPS with a power consumption below 1 W (0.25  $\mu \rm m$  CMOS @ 2.5 V). The power consumption of the individual processing elements scales with their loads.

Philips Semiconductors together with Philips Research redesigned the 80C51 microcontroller. The asynchronous version [37] consumes about four times less power than its synchronous counterpart.

Finally, Cogency redesigned a programmable Digital Signal Processor [38], consuming about half the power of its

<sup>&</sup>lt;sup>2</sup>The clock frequency is chosen that high to accommodate sequential algorithms that share resources over subsequent computation steps.

synchronous counterpart.

Most asynchronous circuits have the property that their performance scales continuously with the supply voltage over a wide range. In a number of cases, correct circuit operation has been demonstrated from sub-threshold to oxide-breakdown supply voltages! This makes asynchronous circuits very suitable for adaptive scaling of the supply voltage [39], [40]. Such schemes can also work for synchronous circuits, but then the clock frequencies must scale simultaneously.

The number of published asynchronous low-power circuits is growing rapidly. In increasingly many cases there are careful comparisons with existing synchronous solutions. However, these comparisons are not always against an optimal low-power synchronous circuit. Moreover, there is also considerable progress in reducing the power in clocked circuits, for example by introducing multiple clocks or by locally gating clocks. Clock gating, also known as conditional clocking, has recently been applied to advanced high-performance microprocessors [41], [42]. Synthesis of clock-gating circuitry can to some extent be automated [43], [44]. Although the results are sometimes impressive (a four-fold reduction of the power consumption in a floating point unit [41]), it is also noted that clock gating complicates functional validation and timing verification, and that the extra gate used to qualify the clock can potentially introduce critical skews.

In summary, asynchronous operation by itself does not imply low power [45], but often suggests low-power opportunities based on the observation that asynchronous circuits only consumes power when and where active.

# IV. ASYNCHRONOUS FOR LOW NOISE AND LOW EMISSION

Subcircuits of a system may interact in unintended and often subtle ways. For example, a digital subcircuit generates voltage noise on the power-supply lines or induces currents in the silicon substrate. This noise may affect the performance of an analog-to-digital converter connected so as to draw power from the same source or that is integrated on the same substrate. Another example is that of a digital subcircuit that emits electro-magnetic radiation at its clock frequency (and the higher harmonic frequencies), and a radio receiver sub-circuit that mistakes this radiation for a radio signal.

Due to the absence of a clock, asynchronous circuits may have better noise and EMC (Electro-Magnetic Compatibility) properties [28] than synchronous circuits. This advantage can be appreciated by analyzing the supply current of a clocked circuit in both the time and frequency domains.

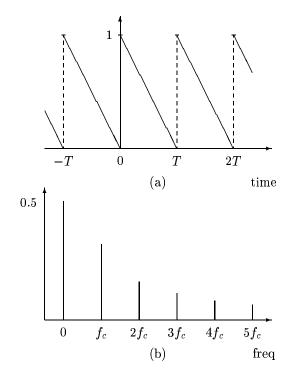

Circuit activity of a clocked circuit is usually maximal shortly after the productive clock edge. It gradually fades away and the circuit must become totally quiescent before the next productive clock edge. Viewed differently, the clock signal modulates the supply current as depicted schematically in Figure 5(a). Due to parasitic resistance and inductance in the on-chip and off-chip supply wiring this causes noise on the on-chip power and ground lines.

Fig. 5. Approximation of the supply current  $I_{dd}$  of a clocked circuit in the time domain (a) and in the frequency domain (b).

Local drops in the supply-voltage have impact on performance, and excessive noise may even impact circuit reliability.

Another problem becomes manifest when the supply current is analyzed in the frequency domain. The supply current of Figure 5(a) can be rewritten as

$$\frac{1}{2} - \frac{1}{\pi} \left( \sin \omega_c t + \frac{1}{2} \sin 2\omega_c t + \frac{1}{3} \sin 3\omega_c t + \cdots \right).$$

with  $\omega_c=2\pi f_c$ . Hence, the clock causes a discrete contribution to the frequency spectrum of the supply current. The amplitude of this spectrum is shown in Figure 5(b). The coefficients at  $nf_c$  with (n>1) denote the so-called harmonic amplitudes.<sup>3</sup> Voltage drops across parasitic inductances as well as the emitted electro-magnetic fields are proportional to the first time derivative of the supply current. Hence, the amplitudes of the higher harmonics of the EM emission hardly drop at all below a few GHz! These higher harmonics may interfere with antennas and sensitive analogue circuits, including radio circuits from FM (100 MHz) to portable phones (1-2 GHz). For example, a tuner may mistake a particular harmonic of a clock frequency for a local FM station. The effects of interference can be reduced by means of (costly) shielding measures.

Note that harmonics are generally distinct, sharp peaks because of the high quality of applied oscillators. In practice the spectrum is continuous and time varying due to non-periodic components in the supply currents.

<sup>&</sup>lt;sup>3</sup>In contrast to Figure 5(a) the circuit is generally quiescent *well* before the productive clock edge, often as early as halfway into the clock period to accommodate derating. In the frequency domain this manifests itself by relatively smaller coefficients for the even harmonics.

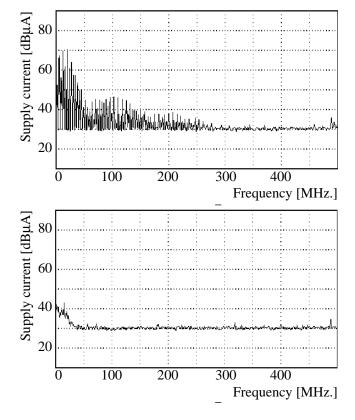

Fig. 6. Frequency spectra of the measured supply current of a synchronous version (top) and an asynchronous version (bottom) of the 80C51 microcontroller. The two microcontrollers use the same cell library, have been realized in a 0.5  $\mu$  CMOS process, and run the same test program at the same performance. (Graphs kindly provided by Philips Semiconductors Zürich.)

The frequency spectrum of the supply current of an asynchronous circuit obviously does not exhibit peaks at clock frequencies and multiples thereof. There may be spikes, but they tend to fade away when a longer integration interval is taken. Even periodic circuit behavior is less harmful; data-dependent delays invariably cause jitter, and even a modest amount of jitter causes a rapid fall-off of the harmonics.

Figure 6 shows the frequency spectra of the supply current of both the synchronous version (top) and the asynchronous version [37] (bottom) of the 80C51 microcontroller. The synchronous version clearly shows a series of harmonics of the clock frequency (here about 3.6 MHz), dominating the spectrum up to about 300 MHz. In a pager product, the harmonics generated by such a synchronous microcontroller could interfere with the very sensitive analog radio circuits. In contrast, the low emission levels of the asynchronous 80C51 makes it possible to have the microcontroller active during reception of a paging message. For this reason Philips Semiconductors has developed a family of entirely asynchronous Pager Baseband Controller ICs, based on the cited asynchronous 80C51.4 This IC has been put on the market successfully.

Note that reducing power consumption generally also reduces the energy content of these spectra. An example of a measured electro-magnetic emission spectrum of an asynchronous microprocessor can be found in this issue in [20].

The above suggests that asynchronous circuits often may be superior in EMC (Electro-Magnetic Compatibility). In some specific cases, however, the opposite may be true. For example, a synchronous circuit is known to be quiescent just before the productive clock edge, providing an excellent moment to sample an analog signal for A-to-D conversion.

The above analysis is highly simplified, and ignores for example the noise and EM emission associated with the simultaneous driving of a number of output loads. Still, EMC is becoming an increasingly important issue in electronic system design, with respect to safety, reliability, and system costs. The relative EMC merits of asynchronous circuits clearly deserves more research attention.

#### V. Heterogeneous Timing

There are two on-going trends that affect the timing of a system-on-a-chip: the relative increase of interconnect delays versus gate delays and the rapid growth of design reuse. Their combined effect results in an increasingly heterogeneous organization of system-on-a-chip timing.

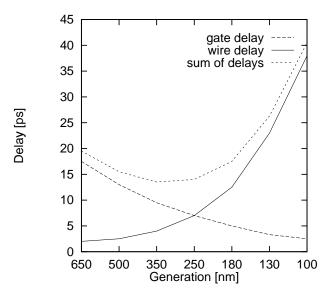

Fig. 7. Calculated gate and interconnect delay versus technology generation. The interconnect is an aluminum wire of 43  $\mu$  length and 0.8  $\mu$  thickness. Adapted from the SIA roadmap [46].

According to Figure 7, gate delays rapidly decrease with each technology generation. By contrast, the delay of a piece of interconnect of fixed modest length increases, soon leading to a dominance of interconnect delay over gate delay [47], [46]. The introduction of additional interconnect layers and new materials (copper and low dielectric constant insulators) may slow down this trend somewhat. Nevertheless, new circuits and architectures are required to circumvent these parasitic limitations. For example, across-chip communication may no longer fit within a single clock period of a processor core. Accordingly, the 1997

<sup>&</sup>lt;sup>4</sup>The IC reported in [26, in this issue] is not a member of this family of ICs.

<sup>&</sup>lt;sup>5</sup>Personal communication of the authors with Francisco Ferrer of Philips Semiconductors Zürich.

edition of the SIA roadmap predicts a divergence between "on-chip local clock frequencies" and "across-chip clock frequencies". The former outperforms the latter by a factor that gradually grows to three. The increasing role of interconnect parasitics also makes it less and less practical to distribute a single high-frequency clock across the entire IC.

The same roadmap also predicts that the fraction of the die area covered by reusing existing circuit designs will increase to as much as 90%. Moreover, complex systems-on-a-chip will accommodate blocks from different design houses (DSP cores, microcontrollers, a variety of memory blocks, MPEG decoders, modems, etc.) and blocks that must conform to standardized off-chip interfaces. The result will be a plethora of (local) clock frequencies and circuit-level timing conventions.

Heterogeneous system timing will offer considerable design challenge for system-level interconnect, including buses, fifos, switch matrices, routers, and multi-port memories. Asynchrony makes it easier to deal with interconnecting a variety of different clock frequencies, without worrying about synchronization problems, differences in clock phases and frequencies, and clock skew [48]. Hence, new opportunities will arise for asynchronous interconnect structures and protocols [49], [50], [51]. Once asynchronous on-chip interconnect structures are accepted, the threshold to introduce asynchronous clients to these interconnects is lowered as well. Also, mixed synchronous-asynchronous circuits hold promise [52], [53] and [26, in this issue].

#### VI. TOOLS, LIBRARIES, AND TESTABILITY

For a wider acceptance and application of asynchronous circuit technology, it is critical that tools for the synthesis and verification of asynchronous circuits become available. In order to make asynchronous circuits more competitive in cost, it would also be beneficial to extend standard-cell and gate-array libraries with a number of typical asynchronous circuits. Furthermore, it is absolutely essential that effective test approaches and tools be developed such that asynchronous circuits can be tested according to the same quality standards as synchronous circuits.

#### Tools

Fortunately, many of the conventional tools such as simulators, placement and routing tools, and delay extractors, are also very effective in supporting the design of asynchronous circuits. This may even apply to logic synthesis tools and timing-analysis tools for certain asynchronous design styles. By relying on a systematic design method, an entire micro-processor has been designed successfully, without dedicated asynchronous design tools [32].

Nevertheless, the manual design of asynchronous control circuits is difficult and error prone. Hazards are easily introduced, and often very hard to recognize. A tool that verifies whether a given control circuit exhibits the specified behavior, and therefore is hazard free, is especially useful [54]. In many practical circuits, the absence of hazards depends on assumptions on the relative delays of the

various circuit elements. Examples of tools to check these timing assumptions are [55], [56].

Synthesis of asynchronous control circuits is becoming a mature technology. Most computer-aided design (CAD) tools synthesize these circuits from one of two specificiation styles: burst-mode, a Mealy-type state machine description [57], [58], [59], [52]; and signal transition graphs, or STGs, a Petri-net based formalism [60], [61], [62], [63]. The synthesized circuits are hazard-free, but differ in assumption on delays. STG-based circuits are often speed-independent, allowing robust operation with weak assumptions about delays. In contrast, burst-mode circuits typically must meet somewhat stricter timing constraints (fundamental-mode assumption [64]) (which in practice are often easily met), but allow greater flexibility in the synthesis path. A number of tools have been developed for both burst-mode [57], [65], [66], [67], [59], [68] and STG [69], [60], [70], [71], [72], [73] synthesis; these have been applied to a number of real-world designs [74], [13], [8], [75], [73], [76]. An alternative approach has also been proposed, called timed circuits [77], which incorporates user-specified timing information to optimize the circuits. Compiling asynchronous circuits from higher-level programming languages has been extensively explored in [78], [79], [80] and these methods have been used to produce about two dozen functional ICs, including [81], [29], [37], [26, this issue].

It would be an error to apply a regular "synchronous" technology mapper [82] to asynchronous circuits, because the mapper may introduce hazards in an otherwise hazard-free circuit. Technology mapping for asynchronous circuits is addressed in, amongst others, [83], [84], [13] and [85] of this issue.

Performance analysis of synchronous circuits can cleanly be separated into two tasks: the measurement of the length of the critical path in the combinational logic, and the counting of the number of clock ticks required for a given task. In asynchronous circuits, however, delays are often data dependent, and are not rounded to an integer number of clock periods. Therefore, timing and performance analysis of asynchronous circuits clearly requires different techniques and are the subject of [17], [86] in this issue.

The academic research community has been very active in developing CAD tools, and many tools that support the design of asynchronous circuits are available on the Internet [87]. So far, EDA vendors have monitored these developments, but they have not yet included such tools in their product portfolios.

#### Layout libraries

Asynchronous circuits can be implemented using standard cells and gate-arrays without major problems. Although common standard-cell libraries have been optimized for the realization of synchronous circuits, they turn out to be adequate for realizing asynchronous circuits as well [29]. Nevertheless, circuit-area reductions of, say, 10% can often be achieved by optimizing common asynchronous cells such as latches, various C-elements, and mutual-exclusion elements.

A synchronous circuit organized according to Figure 1 has two features that simplify testing dramatically: it can be stopped during each clock cycle, and it is both simple and cheap to include a scan-chain through all flip-flops. Asynchronous circuits exhibit more autonomy, and given the large variety of isolated latch elements it is harder and more costly to connect them into scan chains. Accordingly, testing asynchronous circuits is harder, and the cost overhead for design-for-testability measures is higher. Nevertheless, testing specific classes of asynchronous circuits appears feasible, and progress is being made to reduce testability costs. See, for example, [88] and [89, this issue].

#### VII. CONCLUSION

In this article we have reviewed four opportunities for the application of asynchronous circuits. Our findings are summarized below.

First, by avoiding the wait until the next clock edge, asynchronous circuits exhibit average-case performance rather than worst-case performance. Furthermore, asynchronous circuits avoid the overheads and problems associated with distributing clock signals. These potential advantages must, however, be balanced against some delay overheads introduced by asynchronous control and completion detection. This balance will weigh in favor of the asynchronous alternative when the delays of the combinational logic are highly data dependent, or when for a subfunction the optimal clock frequency is simply not available on chip. Indirectly, the elasticity of asynchronous pipelines may offer other advantages, such as free buffer capacity.

Second, by enabling latches and flip-flops only when their state must be updated, asynchronous circuits consume power only when and where active. This type of power savings can also be realized by gating and pausing local clocks in synchronous circuits, however at the expense of some additional clock skew. Also, asynchronous circuit technology naturally provides power savings at arbitrary levels of granularity, and has methods and tools to guarantee absence of hazards on the latch enable wires.

Third, asynchronous circuits do not emit radiation at the clock frequency and harmonic frequencies thereof. This opportunity for asynchronous circuits is quite fundamental. Still, more study and measurements are required to quantify its significance.

Fourth, the increasing significance of parasitic interconnect resistance, the increasing reuse of building blocks, and the integration of entire systems on a few chips inevitably leads to a complex and heterogeneous on-chip timing organization. It will be less and less practical to clock all building blocks on a single, high-frequency, global clock. Here, the application of asynchronous circuits and sub-circuits probably holds most promise. Their use may well turn out to be unavoidable.

As becomes apparent from the above discussion, for each opportunity one may argue that there exists also a synchronous alternative. Indeed, in many cases these alternatives may have the desired effect to some extent. In

other cases asynchronous solutions may be more effective, cheaper, easier to realize, or simply more elegant.

Of course, an asynchronous (sub-)circuit will only make it to the market place when there is no synchronous alternative or when the asynchronous solution has a clear and substantial advantage. The improved EMC properties of the asynchronous pager IC of Philips is a good example of such an advantage. Given the rich experience developed over the last decade by a very active and productive asynchronous research community, we predict that asynchronous circuit technology will be applied more and more often. Based on this review we do not expect an asynchronous revolution, but rather a steady evolution.

#### References

- [1] Ad Peeters, "The 'Asynchronous' Bibliography (BIBTEX) database file async.bib," ftp://ftp.win.tue.nl/pub/tex/async.bib.Z, Corresponding e-mail address: async-bib@win.tue.nl.

- [2] Jim Garside, "The Asynchronous Logic Homepage," http://www.cs.man.ac.uk/amulet/async/.

- [3] Mark B. Josephs, Steven M. Nowick, and C.H. (Kees) van Berkel, "Modeling and design of asynchronous circuits," *IEEE Proceedings*, this issue.

- [4] Charles L. Seitz, "System timing," in Introduction to VLSI Systems, Carver A. Mead and Lynn A. Conway, Eds., chapter 7. Addison-Wesley, 1980.

- [5] Jim D. Garside, "A CMOS VLSI implementation of an asynchronous ALU," in Asynchronous Design Methodologies, S. Furber and M. Edwards, Eds. 1993, vol. A-28 of IFIP Transactions, pp. 181-207, Elsevier Science Publishers.

- [6] Bruce Gilchrist, J. H. Pomerene, and S. Y. Wong, "Fast carry logic for digital computers," IRE Transactions on Electronic Computers, vol. EC-4, no. 4, pp. 133-136, Dec. 1955.

- [7] L. S. Nielsen and J. Sparsø, "Designing asynchronous circuits for low power: An ifir filter bank for a digital hearing aid," *IEEE Proceedings*, this issue.

- [8] Kenneth Y. Yun, Ayoob E. Dooply, Julio Arceo, Peter A. Beerel, and Vida Vakilotojar, "The design and verification of a high-performance low-control-overhead asynchronous differential equation solver," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems. Apr. 1997, IEEE Computer Society Press.

- [9] Alain J. Martin, "Asynchronous datapaths and the design of an asynchronous adder," Formal Methods in System Design, vol. 1, no. 1, pp. 119-137, July 1992.

- [10] Steven M. Nowick, Kenneth Y. Yun, and Peter A. Beerel, "Speculative completion for the design of high-performance asynchronous dynamic adders," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems. Apr. 1997, IEEE Computer Society Press.

- [11] Neil H.E. Weste and Kamran Eshraghian, Principles of CMOS VLSI Design; A System Perspective; SECOND EDITION, Addison-Wesley Publ. Company, 1993.

- [12] Martin Benes, Andrew Wolfe, and Steven M. Nowick, "A high-speed asynchronous decompression circuit for embedded processors," in Advanced Research in VLSI, Sept. 1997.

- [13] W. Chou, P. A. Beerel, R. Ginosar, R. Kol, C. J. Myers, S. Rotem, K. Stevens, and K. Y. Yun, "Average-case optimized technology mapping of one-hot domino circuits," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems, 1998, pp. 80-91.

- [14] Hans Jacobson and Ganes Gopalakrishnan, "Applicationspecific programmable control for high performance asynchronous circuits," *IEEE Proceedings*, this issue.

- [15] Ivan E. Sutherland, "Micropipelines," Communications of the ACM, vol. 32, no. 6, pp. 720-738, June 1989.

- [16] C.E. Molnar, I.W. Jones, W.S. Coates, J.K. Lexau, S.M. Fair-banks, and I.E. Sutherland, "Two FIFO Ring Performance Experiments," *IEEE Proceedings*, this issue.

- [17] Jo Ebergen and Robert Berks, "Response time properties of linear asynchronous pipelines," *IEEE Proceedings*, this issue.

- [18] Ted E. Williams and Mark A. Horowitz, "A zero-overhead self-timed 160ns 54b CMOS divider," *IEEE Journal of Solid-State Circuits*, vol. 26, no. 11, pp. 1651–1661, Nov. 1991.

- [19] Gensoh Matsubara and Nobuhiro Ide, "A low power zerooverhead self-timed division and square root unit combining a single-rail static circuit with a dual-rail dynamic circuit," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems. Apr. 1997, IEEE Computer Society Press.

- [20] S.B. Furber, J.D. Garside, P. Riocreux, and S. Temple, "Amulet2e: An Asynchronous Embedded Controller," *IEEE Proceedings*, this issue.

- [21] Robert F. Sproull, Ivan E. Sutherland, and Charles E. Molnar, "The counterflow pipeline processor architecture," *IEEE Design & Test of Computers*, vol. 11, no. 3, pp. 48-59, Fall 1994.

- [22] Alain J. Martin, Andrew Lines, Rajit Manohar, Mika Nystroem, Paul Penzes, Robert Southworth, and Uri Cummings, "The design of an asynchronous MIPS R3000 microprocessor," in Advanced Research in VLSI, Sept. 1997.

- [23] Mark E. Dean, STRiP: A Self-Timed RISC Processor Architecture, Ph.D. thesis, Stanford University, 1992.

- [24] Kees van Berkel, "VLSI programming of a modulo-N counter with constant response time and constant power," in Asynchronous Design Methodologies, S. Furber and M. Edwards, Eds. 1993, vol. A-28 of IFIP Transactions, pp. 1-11, Elsevier Science Publishers.

- [25] Joep L. W. Kessels, "Calculational derivation of a counter with bounded response time and bounded power dissipation," Distributed Computing, vol. 8, no. 3, pp. 143-149, 1995.

- [26] Joep Kessels and Paul Marston, "Designing asynchronous standby circuits for a low-power pager," *IEEE Proceedings*, this issue.

- [27] Kees van Berkel and Martin Rem, "VLSI programming of asynchronous circuits for low power," in Asynchronous Digital Circuit Design, Graham Birtwistle and Al Davis, Eds. 1995, Workshops in Computing, pp. 152–210, Springer-Verlag.

- [28] Kees van Berkel, Ronan Burgess, Joep Kessels, Ad Peeters, Marly Roncken, and Frits Schalij, "Asynchronous circuits for low power: A DCC error corrector," *IEEE Design & Test of Computers*, vol. 11, no. 2, pp. 22-32, Summer 1994.

- [29] Kees van Berkel, Ronan Burgess, Joep Kessels, Ad Peeters, Marly Roncken, Frits Schalij, and Rik van de Wiel, "A singlerail re-implementation of a DCC error detector using a generic standard-cell library," in Asynchronous Design Methodologies. May 1995, pp. 72-79, IEEE Computer Society Press.

- [30] Alan Marshall, Bill Coates, and Polly Siegel, "Designing an asynchronous communications chip," IEEE Design & Test of Computers, vol. 11, no. 2, pp. 8–21, 1994.

- [31] L. S. Nielsen and J. Sparsø, "An 85µW asynchronous filter-bank for a digital hearing aid," in *International Solid State Circuits Conference*, Feb. 1998.

- [32] S. Furber, "Computing without clocks: Micropipelining the ARM processor," in Asynchronous Digital Circuit Design, Graham Birtwistle and Al Davis, Eds. 1995, Workshops in Computing, pp. 211-262, Springer-Verlag.

- [33] J. D. Garside, S. Temple, and R. Mehra, "The AMULET2e cache systems," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems. Mar. 1996, IEEE Computer Society Press.

- [34] Shinji Komori, Hidehiro Takata, Toshiyuki Tamura, Fumiyasu Asai, Takio Ohno, Osamu Tomisawa, Tetsuo Yamasaki, Kenji Shima, Hiroaki Nishikawa, and Hiroaki Terada, "A 40-MFLOPS 32-bit floating-point processor with elastic pipeline scheme," IEEE Journal of Solid-State Circuits, vol. 24, no. 5, pp. 1341–1347, Oct. 1989.

- [35] Hiroaki Terada, Makoto Iwata, Souichi Miyata, and Shinji Komori, "Superpipelined dynamic data-driven VLSI processors," in Advanced Topics in Dataflow Computing and Multithreading. 1995, pp. 75-85, IEEE Computer Society Press.

- [36] H. Terada, S. Miyata, and M. Iwata, "DDMPs: Self-Timed Super-Pipelined Data-Driven Multimedia Processors," IEEE Proceedings, this issue.

- [37] Hans van Gageldonk, Daniel Baumann, Kees van Berkel, Daniel Gloor, Ad Peeters, and Gerhard Stegmann, "An asynchronous low-power 80c51 microcontroller," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems, 1998, pp. 96-107.

- [38] N. C. Paver, P. Day, C. Farnsworth, D. L. Jackson, W. A. Lien, and J. Liu, "A low-power, low-noise configurable self-timed DSP," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems, 1998, pp. 32-42.

- [39] L. S. Nielsen, C. Niessen, J. Sparsø, and C. H. van Berkel, "Low-power operation using self-timed and adaptive scaling of the supply voltage," *IEEE Transactions on VLSI Systems*, vol. 2, no. 4, pp. 391–397, Dec. 1994.

- [40] Joep Kessels, "VLSI programming of a low-power asynchronous Reed-Solomon decoder for the DCC player," in Asynchronous Design Methodologies. May 1995, pp. 44-52, IEEE Computer Society Press.

- [41] Michael K. Gowan, Larry L.Biro, and Daniel B. Jackson, "Power considerations in the design of the alpha 21264 microprocessor," in Proc. ACM/IEEE Design Automation Conference, June 1998, pp. 726-731.

- [42] Vivek Tiwari et al., "Reducing power in high-performance microprocessors," in Proc. ACM/IEEE Design Automation Conference, June 1998, pp. 732-737.

- [43] L. Beninni et al., "Symbolic synthesis of clock-gating logic for power optimization of control-oriented synchronous networks," in *Proc. European Design and Test Conference*. 1997, pp. 514– 520, IEEE Computer Society Press.

- [44] Frans Theeuwen and Eric Seelen, "Power reduction through clock gating by symbolic manipulation," in VLSI: Integrated Systems on Silicon, R. Reis and L. Claesen, Eds. 1997, vol. A-28 of IFIP Transactions, pp. 389-399, Chapman & Hall.

- [45] Kees van Berkel, Hans van Gageldonk, Joep Kessels, Cees Niessen, Ad Peeters, Marly Roncken, and Rik van de Wiel, "Asynchronous does not imply low power, but ...," in Low Power CMOS Design, Anantha Chandrakasan and Robert Brodersen, Eds. IEEE Press, 1998.

- [46] Semiconductor Industry Association, "The national technology roadmap for semiconductors; technology needs," http://www.sematech.org/public/roadmap/.

- [47] Mark T. Bohr, "Interconnect scaling the real limiter to high performance ulsi," in Proceedings of the 1995 IEEE International Electron Devices Meeting, 1995, pp. 241-242.

- [48] Daniel M. Chapiro, Globally-Asynchronous Locally-Synchronous Systems, Ph.D. thesis, Stanford University, Oct. 1984.

- [49] Ivan E. Sutherland, Charles E. Molnar, Robert F. Sproull, and J. Craig Mudge, "The trimosbus," in Proceedings of the First Caltech Conference on Very Large Scale Integration, Charles L. Seitz, Ed., 1979, pp. 395-427.

- [50] W. J. Bainbridge and S. B. Furber, "Asynchronous macrocell interconnect using MARBLE," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems, 1998, pp. 122-132.

- [51] M. Greenstreet, "Implementing a STARI chip," in Proceedings of the IEEE International Conference on Computer Design. October 1995, pp. 38-43, IEEE Computer Society Press.

- [52] K.Y. Yun and D.L. Dill, "Unifying synchronous/asynchronous state machine synthesis," in Proceedings of the IEEE/ACM International Conference on Computer-Aided Design. November 1993, pp. 255-260, IEEE Computer Society Press.

- [53] Allen E. Sjogren and Chris J. Myers, "Interfacing synchronous and asynchronous modules within a high-speed pipeline," in Advanced Research in VLSI, Sept. 1997, pp. 47-61.

- [54] David L. Dill, Trace Theory for Automatic Hierarchical Verification of Speed-Independent Circuits, ACM Distinguished Dissertations. MIT Press, 1989.

- [55] A. Semenov and A. Yakovlev, "Verification of asynchronous circuits using time petri net unfolding," in 33rd ACM/IEEE Design Automation Conference, June 1996.

- [56] Radu Negulescu and Ad Peeters, "Verification of speed-dependences in single-rail handshake circuits," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems, 1998, pp. 159-170.

- [57] Steven M. Nowick and David L. Dill, "Synthesis of asynchronous state machines using a local clock," in Proc. International Conf. Computer Design (ICCD). Oct. 1991, pp. 192-197, IEEE Computer Society Press.

- [58] S.M. Nowick, "Automatic synthesis of burst-mode asynchronous controllers," Tech. Rep., Stanford University, March 1993, Ph.D. Thesis (available as Stanford University Computer Systems Laboratory technical report, CSL-TR-95-686, Dec. 95).

- [59] A. Davis, B. Coates, and K. Stevens, "Automatic synthesis of fast compact self-timed control circuits," in 1993 IFIP Work-

- ing Conference on Asynchronous Design Methodologies (Manchester, England), 1993.

- [60] L. Lavagno and A. Sangiovanni-Vincentelli, Algorithms for synthesis and testing of asynchronous circuits, Kluwer Academic,

- [61] Tam-Anh Chu, "On the models for designing vlsi asynchronous digital systems," INTEGRATION, the VLSI journal, , no. 4, pp. 99-113, 1986.

- T. H.-Y. Meng, R.W. Brodersen, and D.G. Messerschmitt, "Automatic synthesis of asynchronous circuits from high-level spec-IEEE Transactions on Computer-Aided Design of ifications. Integrated Circuits and Systems, vol. 8, no. 11, pp. 1185-1205, November 1989.

- [63] M.A. Kishinevsky, A.Y. Kondratyev, A.R. Taubin, and V.I. Varshavsky, Concurrent Hardware: The Theory and Practice of Self-Timed Design, John Wiley and Sons Ltd., 1994.

- S.H. Unger, Asynchronous Sequential Switching Circuits, Wiley-Interscience, New York, NY, 1969.

- [65] P. Kudva, G. Gopalakrishnan, and H. Jacobson, "A technique for synthesizing distributed burst-mode circuits," in 33rd ACM/IEEE Design Automation Conference, June 1996.

- [66] R.M. Fuhrer, B. Lin, and S.M. Nowick, "Symbolic hazardfree minimization and encoding of asynchronous finite state machines," in IEEE/ACM International Conference on Computer-Aided Design (ICCAD), November 1995, pp. 604-611.

- [67] K.Y. Yun and D.L. Dill, "Automatic synthesis of 3D asynchronous finite-state machines," in Proceedings of the IEEE/ACM International Conference on Computer- Aided Design. November 1992, IEEE Computer Society Press.

- M. Theobald and S. M. Nowick, "An implicit method for hazardfree two-level minimization," in Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems, 1998, pp. 58-69.

- [69] P. Beerel and T.H.-Y. Meng, "Automatic gate-level synthesis of speed-independent circuits," in Proc. International Conf. Computer-Aided Design (ICCAD). Nov. 1992, pp. 581-587, IEEE Computer Society Press.

- [70] C. Ykman-Couvreur, B. Lin, and H. De Man, "ASSASSIN: a synthesis system for asynchronous control circuits," Tech. Rep., IMEC Laboratory, September 1994, User and tutorial manual.

- [71] J. Cortadella, M. Kishinevsky, A. Kondratyev, L. Lavagno, and A. Yakovlev, "Complete state encoding based on the theory in Proceedings of the International Symposium of regions," on Advanced Research in Asynchronous Circuits and Systems (Async96). November 1996, pp. 36-47, IEEE Computer Society

- [72] A. Kondratyev, M. Kishinevsky, B. Lin, P. Vanbekbergen, and A. Yakovlev, "Basic gate implementation of speed-independent circuits," in Proceedings of the 31st ACM/IEEE Design Automation Conference. June 1994, pp. 56-62, ACM.

- [73] Jordi Cortadella, Michael Kishinevsky, Alex Kondratyev, Luciano Lavagno, and Alexandre Yakovlev, "Petrify: a tool for manipulating concurrent specifications and synthesis of asynchronous controllers," in XI Conference on Design of Integrated Circuits and Systems, Barcelona, Nov. 1996.

- [74] Bill Coates, Al Davis, and Ken Stevens, "The Post Office experience: Designing a large asynchronous chip," Integration, the VLSI journal, vol. 15, no. 3, pp. 341-366, Oct. 1993.

- [75] S.M. Nowick, M.E. Dean, D.L. Dill, and M. Horowitz, "The design of a high-performance cache controller: a case study in asynchronous synthesis," INTEGRATION, the VLSI journal, vol. 15, no. 3, pp. 241–262, October 1993.

- K.Y. Yun and D.L. Dill, "A high-performance asynchronous SCSI controller," in Proceedings of the IEEE International Conference on Computer Design. October 1995, pp. 44-49, IEEE Computer Society Press.

- [77] Chris J. Myers and Teresa H.-Y. Meng, "Synthesis of timed asynchronous circuits," IEEE Transactions on VLSI Systems, vol. 1, no. 2, pp. 106-119, June 1993.

- Erik Brunvand and Robert F. Sproull, "Translating concurrent programs into delay-insensitive circuits," in Proc. International Conf. Computer-Aided Design (ICCAD). Nov. 1989, pp. 262-265, IEEE Computer Society Press.

- [79] Alain J. Martin, "Programming in VLSI: From communicating processes to delay-insensitive circuits," in Developments in Concurrency and Communication, C. A. R. Hoare, Ed. 1990, UT Year of Programming Series, pp. 1-64, Addison-Wesley.

- [80] Kees van Berkel, Handshake Circuits: an Asynchronous Architecture for VLSI Programming, vol. 5 of International Series on Parallel Computation, Cambridge University Press, 1993.

- Alain J. Martin, Steven M. Burns, T. K. Lee, Drazen Borkovic, and Pieter J. Hazewindus, "The design of an asynchronous microprocessor," in Advanced Research in VLSI: Proceedings of the Decennial Caltech Conference on VLSI, Charles L. Seitz, Ed. 1989, pp. 351-373, MIT Press.

- K. Keutzer, "Dagon: Technology binding and local optization by dag matching," in Proc. ACM/IEEE Design Automation Conference, June 1987, pp. 341-347.

- P. Siegel, G. De Micheli, and D. Dill, "Automatic technology mapping for generalized fundamental-mode asynchronous designs," in Proc. ACM/IEEE Design Automation Conference, June 1993, pp. 61–67.

- P. A. Beerel, K. Y. Yun, and W. C. Chou, "Optimizing averagecase delay in technology mapping of burst-mode circuits," Proc. International Symposium on Advanced Research in Asynchronous Circuits and Systems. Mar. 1996, IEEE Computer Society Press.

- Alex Kondratyev, Jordi Cortadella, Michael Kishinevsky, Luciano Lavagno, and Alex Yakovlev, "Logic decomposition of speed-independend circuits," IEEE Proceedings, this issue.

- Supratik Chakraborty, David L. Dill, and Kenneth Y. Yun, "Min-max timing analysis and an application to asynchronous circuits,"  $IEEE\ Proceedings,$  this issue.

- Rahardjo Jim Garside, "Asynchronous tools available on the internet," http://www.cs.man.ac.uk/amulet/async/async\_tools.html.

- Henrik Hulgaard, Steven M. Burns, and Gaetano Borriello, "Testing asynchronous circuits: A survey," Integration, the VLSI journal, vol. 19, no. 3, pp. 111-131, Nov. 1995. M. Roncken, "Defect-oriented testability for asynchronous cir-

- cuits," IEEE Proceedings, this issue.