### Fundamentals of Computer Systems Combinational Logic

Martha A. Kim

**Columbia University**

Fall 2013

Combinational circuits are stateless.

Their output is a function *only* of the current input.

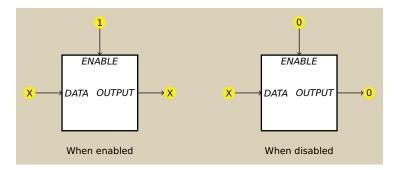

#### **Overview: Enabler**

An enabler has two inputs:

- data: can be several bits, but 1 bit examples for now

- enable/disable: 1 bit on/off switch

When enabled, the circuit's output is its input data. When disabled, the output is 0.

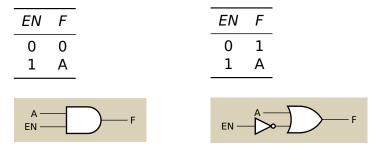

#### **Enabler Implementation**

*Note abbreviated truth table: input, A, listed in output column*

In both cases, output is enabled when EN = 1, but they handle the disabled (EN = 0) cases differently.

#### **Overview: Decoder**

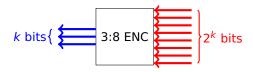

A decoder takes a k - bit input and produces  $2^k$  single-bit outputs.

The input determines which output will be 1, all others 0. This representation is called *one-hot encoding*.

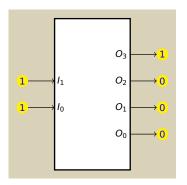

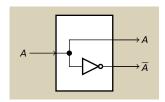

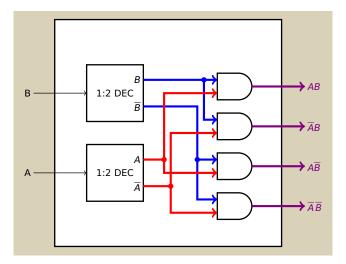

#### The smallest decoder: one bit input, two bit outputs

#### 2:4 Decoder

Decoder outputs are simply minterms. Those values can be constructed as a flat schematic (manageable at small sizes) or hierarchically, as below.

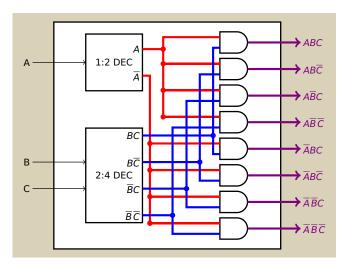

#### 3:8 Decoder

### Applying *hierarchical design* again, the 2:4 DEC helps construct a 3:8 DEC.

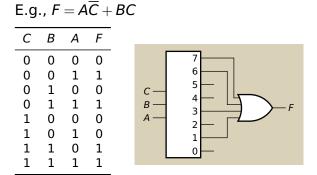

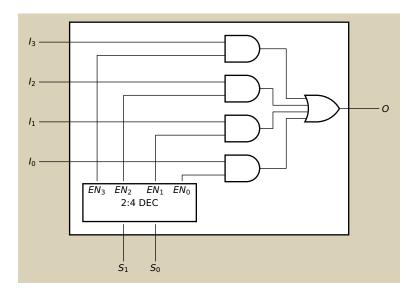

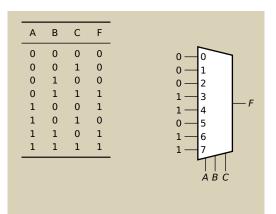

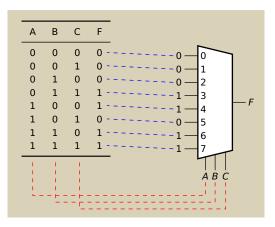

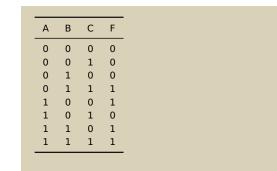

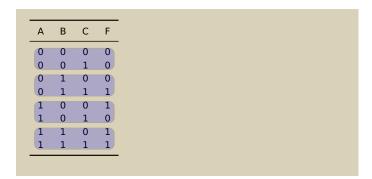

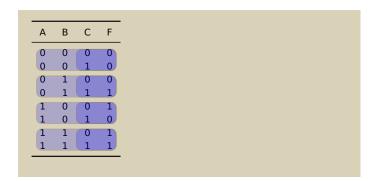

#### Implementing a function with a decoder

Warning: Easy, but not a minimal circuit.

#### **Encoders and Decoders**

| BCD |   |   |   | One-Hot |   |   |   |   |   |   |

|-----|---|---|---|---------|---|---|---|---|---|---|

| 0   | 0 | 0 | 0 | 0       | 0 | 0 | 0 | 0 | 0 | 1 |

| 0   | 0 | 1 | 0 | 0       | 0 | 0 | 0 | 0 | 1 | 0 |

| 0   | 1 | 0 | 0 | 0       | 0 | 0 | 0 | 1 | 0 | 0 |

| 0   | 1 | 1 | 0 | 0       | 0 | 0 | 1 | 0 | 0 | 0 |

| 1   | 0 | 0 | 0 | 0       | 0 | 1 | 0 | 0 | 0 | 0 |

| 1   | 0 | 1 | 0 | 0       | 1 | 0 | 0 | 0 | 0 | 0 |

| 1   | 1 | 0 | 0 | 1       | 0 | 0 | 0 | 0 | 0 | 0 |

| 1   | 1 | 1 | 1 | 0       | 0 | 0 | 0 | 0 | 0 | 0 |

#### **Priority Encoder**

An encoder designed to accept any input bit pattern.

|   |   |   |   |   | $O_1$                 |   |

|---|---|---|---|---|-----------------------|---|

| 0 | 0 | 0 | 0 | 0 | X<br>0<br>0<br>1<br>1 | Х |

| 0 | 0 | 0 | 1 | 1 | 0                     | 0 |

| 0 | 0 | 1 | Х | 1 | 0                     | 1 |

| 0 | 1 | Х | Х | 1 | 1                     | 0 |

| 1 | Х | Х | Х | 1 | 1                     | 1 |

$$V = I_3 + I_2 + I_1 + I_0$$

$$O_1 = I_3 + \overline{I_3}I_2$$

$$O_0 = I_3 + \overline{I_3}I_2I_1$$

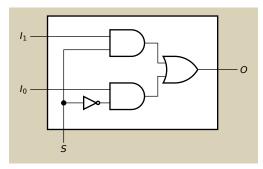

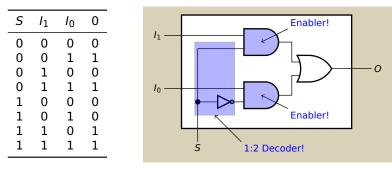

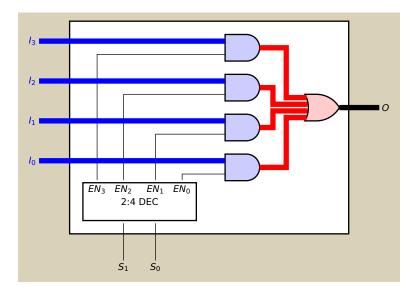

#### Overview: Multiplexer (or Mux)

A mux has a k - bit selector input and  $2^k$  data inputs (multi or single bit).

It outputs a single data output, which has the value of one of the data inputs, according to the selector.

There are a handful of implementation strategies.

E.g., a truth table and k-map are feasible for a design of this size.

| S | $I_1$ | <i>I</i> 0 | 0 |

|---|-------|------------|---|

| 0 | 0     | 0          | 0 |

| 0 | 0     | 1          | 1 |

| 0 | 1     | 0          | 0 |

| 0 | 1     | 1          | 1 |

| 1 | 0     | 0          | 0 |

| 1 | 0     | 1          | 0 |

| 1 | 1     | 0          | 1 |

| 1 | 1     | 1          | 1 |

There are a handful of implementation strategies.

E.g., a truth table and k-map are feasible for a design of this size.

There are a handful of implementation strategies.

E.g., a truth table and k-map are feasible for a design of this size.

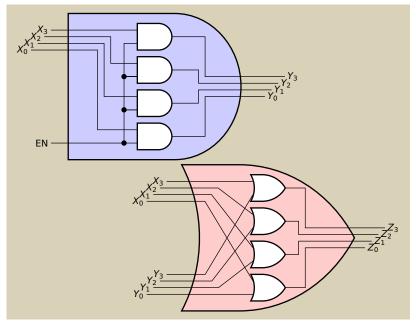

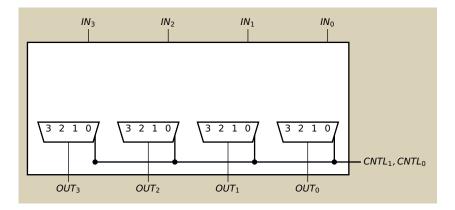

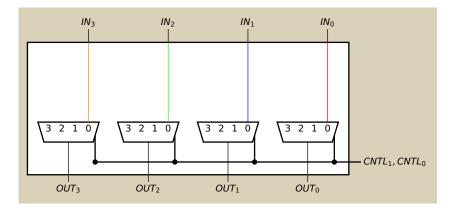

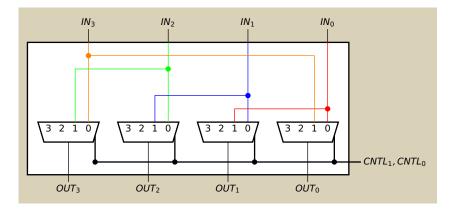

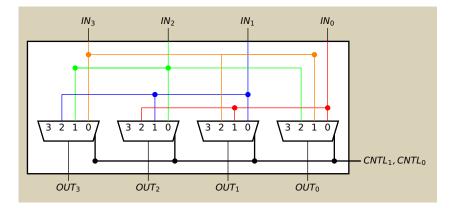

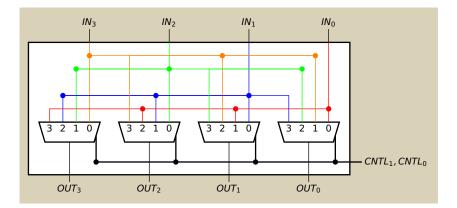

#### Muxing Wider Values (Overview)

#### Muxing Wider Values (Components)

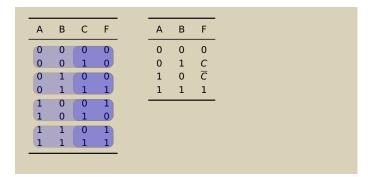

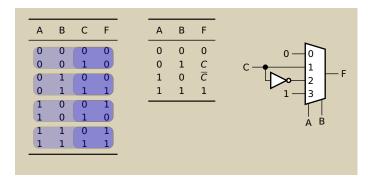

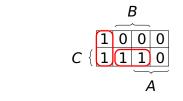

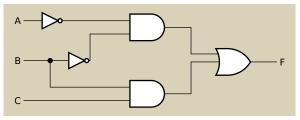

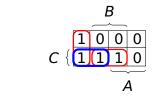

Think of a function as using k input bits to choose from  $2^k$  outputs.

E.g.,  $F = BC + A\overline{C}$

Think of a function as using k input bits to choose from  $2^k$  outputs.

E.g.,  $F = BC + A\overline{C}$

Can we use a smaller MUX?

Instead of feeding just 0 or 1 into the mux, as in Version 1, one can remove a bit from the select, and feed it into the data ports along with the constant.

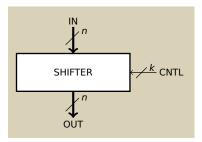

#### **Overview: Shifters**

A shifter shifts the inputs bits to the left or to the right.

There are various types of shifters.

- Barrel: Selector bits indicate (in binary) how far to the left to shift the input.

- L/R with enable: Two control bits (upper enables, lower indicates direction).

In either case, bits may "roll out" or "wraparound"

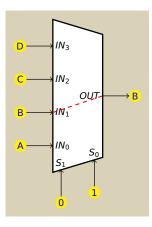

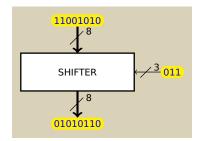

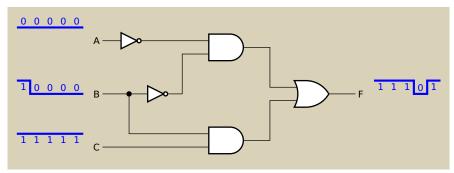

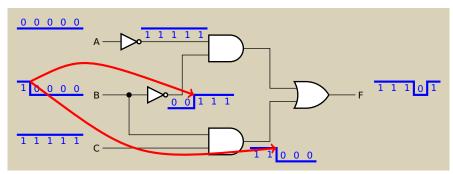

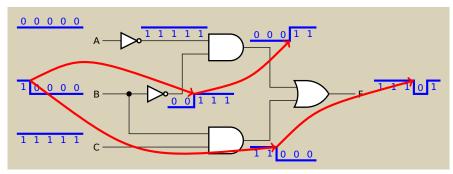

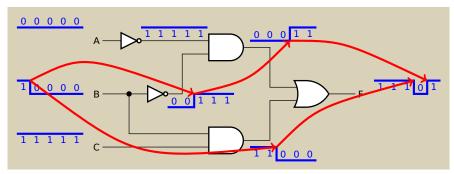

#### Example: Barrel Shifter with Wraparound

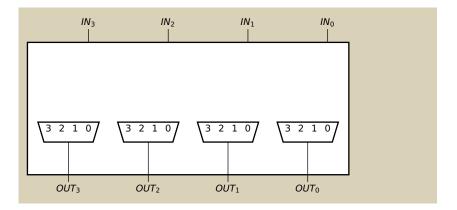

## Implementation of Barrel Shifter with Wraparound (Part 2)

#### Implementation of Barrel Shifter with Wraparound (Part 2)

#### Implementation of Barrel Shifter with Wraparound (Part 2)

#### Implementation of Barrel Shifter with Wraparound (Part 2)

## Implementation of Barrel Shifter with Wraparound (Part 2)

Main idea: wire up all possible shift amounts and use muxes to select correct one.

## Implementation of Barrel Shifter with Wraparound (Part 2)

Main idea: wire up all possible shift amounts and use muxes to select correct one.

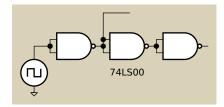

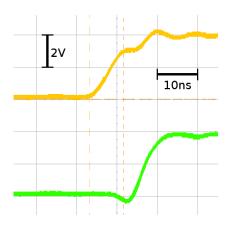

## **Computation Always Takes Time**

There is a delay between inputs and outputs, due to:

- Limited currents charging capacitance

- $\cdot$  The speed of light

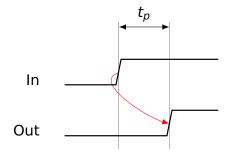

# The Simplest Timing Model

- Each gate has its own propagation delay t<sub>p</sub>.

- When an input changes, any changing outputs do so after t<sub>p</sub>.

- Wire delay is zero.

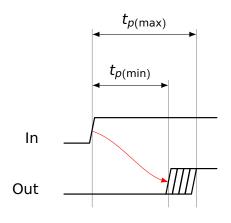

## A More Realistic Timing Model

It is difficult to manufacture two gates with the same delay; better to treat delay as a range.

- Each gate has a minimum and maximum propagation delay t<sub>p(min)</sub> and t<sub>p(max)</sub>.

- Outputs may start changing after t<sub>p(min)</sub> and stablize no later than t<sub>p(min)</sub>.

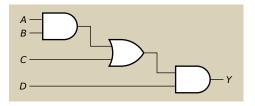

### **Critical Paths and Short Paths**

How slow can this be?

### Critical Paths and Short Paths

How slow can this be?

The critical path has the longest possible delay.

$$t_{

m

ho(max)} = t_{

m

ho(max, AND)} + t_{

m

ho(max, OR)} + t_{

m

ho(max, AND)}$$

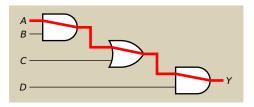

### Critical Paths and Short Paths

How fast can this be?

The shortest path has the least possible delay.

$t_{p(\min)} = t_{p(\min, AND)}$

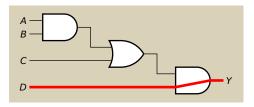

A glitch is when a single change in input values can cause multiple output changes.

A glitch is when a single change in input values can cause multiple output changes.

A glitch is when a single change in input values can cause multiple output changes.

A glitch is when a single change in input values can cause multiple output changes.

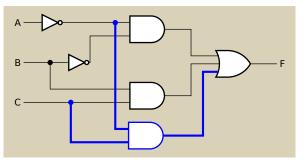

## **Preventing Single Input Glitches**

Additional terms can prevent single input glitches (at a cost of a few extra gates).

### **Preventing Single Input Glitches**

Additional terms can prevent single input glitches (at a cost of a few extra gates).

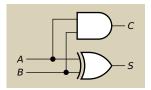

## Arithmetic: Addition

Adding two one-bit numbers: *A* and *B* Produces a two-bit result: *C* and *S* (carry and sum)

| Α | В | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Half Adder

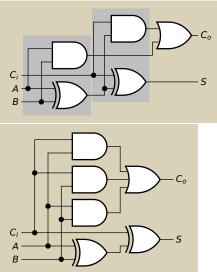

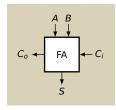

### **Full Adder**

In general, due to a possible carry in, you need to add *three bits*:

| C <sub>i</sub> AB | C <sub>o</sub> S |

|-------------------|------------------|

| 000               | 0 0              |

| 001               | 01               |

| 010               | 01               |

| 011               | 10               |

| 100               | 01               |

| 101               | 10               |

| 110               | 10               |

| 111               | 11               |

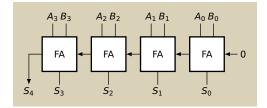

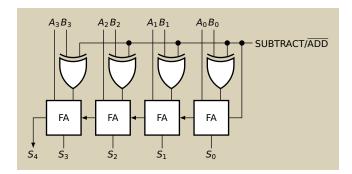

### A Four-Bit Ripple-Carry Adder

#### A Two's Complement Adder/Subtractor

To subtract *B* from *A*, add *A* and -B. Neat trick: carry in takes care of the +1 operation.

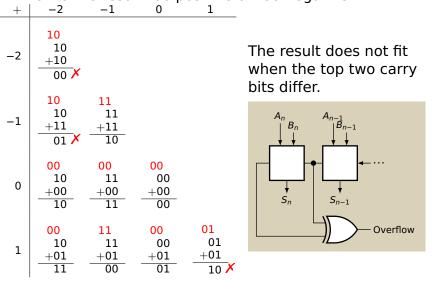

## Overflow in Two's-Complement Representation

When is the result too positive or too negative?

| +  | -2                    | -1                       | 0                     | 1               |

|----|-----------------------|--------------------------|-----------------------|-----------------|

| -2 | 10<br>10<br>+10<br>00 |                          |                       |                 |

| -1 | 10<br>10<br>+11<br>01 | 11     11     +11     10 |                       |                 |

| 0  | 00<br>10<br>+00<br>10 | 00<br>11<br>+00<br>11    | 00<br>00<br>+00<br>00 |                 |

| 1  | 00<br>10<br>+01<br>11 | 11<br>11<br>+01<br>00    | 00<br>00<br>+01<br>01 | 01<br>+01<br>10 |

## Overflow in Two's-Complement Representation

When is the result too positive or too negative?

## Ripple-Carry Adders are Slow

The *depth* of a circuit is the number of gates on a critical path.

This four-bit adder has a depth of 8.

*n*-bit ripple-carry adders have a depth of 2*n*.

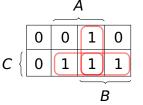

### Carry Generate and Propagate

The carry chain is the slow part of an adder; carry-lookahead adders reduce its depth using the following trick:

$$C_{i+1} = A_i B_i + A_i C_i + B_i C_i$$

=  $A_i B_i + C_i (A_i + B_i)$

=  $G_i + C_i P_i$

K-map for the carry-out function of a full adder

Generate  $G_i = A_i B_i$  sets carry-out regardless of carry-in.

Propagate  $P_i = A_i + B_i$  copies carry-in to carry-out.

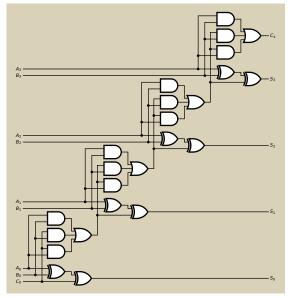

#### Carry Lookahead Adder

Expand the carry functions into sum-of-products form:

$$C_{i+1} = G_i + C_i P_i$$

$$C_{1} = G_{0} + C_{0}P_{0}$$

$$C_{2} = G_{1} + C_{1}P_{1}$$

$$= G_{1} + (G_{0} + C_{0}P_{0})P_{1}$$

$$= G_{1} + G_{0}P_{1} + C_{0}P_{0}P_{1}$$

$$C_{3} = G_{2} + C_{2}P_{2}$$

$$= G_{2} + (G_{1} + G_{0}P_{1} + C_{0}P_{0}P_{1})P_{2}$$

$$= G_{2} + G_{1}P_{2} + G_{0}P_{1}P_{2} + C_{0}P_{0}P_{1}P_{2}$$

$$C_{4} = G_{3} + C_{3}P_{3}$$

$$= G_{3} + (G_{2} + G_{1}P_{2} + G_{0}P_{1}P_{2} + C_{0}P_{0}P_{1}P_{2})P_{3}$$

$= G_3 + G_2 P_3 + G_1 P_2 P_3 + G_0 P_1 P_2 P_3 + C_0 P_0 P_1 P_2 P_3$

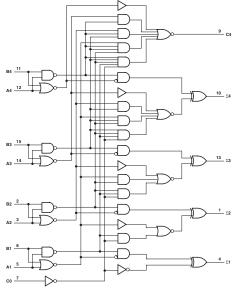

### The 74283 Binary Carry-Lookahead Adder (From National Semiconductor)

Carry out *i* has i + 1product terms, largest of which has i + 1literals.

If wide gates don't slow down, delay is independent of number of bits.

More realistic: if limited to two-input gates, depth is  $O(\log_2 n)$ .