## Scalable Multi-module Packet Switches with Quality of Service

Santosh Krishnan

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

## **COLUMBIA UNIVERSITY**

2006

© 2006

Santosh Krishnan

All Rights Reserved

### ABSTRACT

# Scalable Multi-module Packet Switches with Quality of Service

Santosh Krishnan

The rapid growth in packet-based network traffic has resulted in a growing demand for network switches that can scale in capacity with increasing interface transmission rates and higher port counts. Furthermore, the continuing migration of legacy circuit-switched services to a shared IP/MPLS packet-based network requires such network switches to provide an adequate Quality of Service (QoS) in terms of traffic prioritization, as well as bandwidth and delay guarantees. While technology advances, such as the usage of faster silicon and optical switching components, provide one dimension to address this demand, architectural improvements provide the other. This dissertation addresses the latter topic. Specifically, we address the subject of constructing and analyzing high-capacity QoS-capable packet switches using multiple lower-capacity modules.

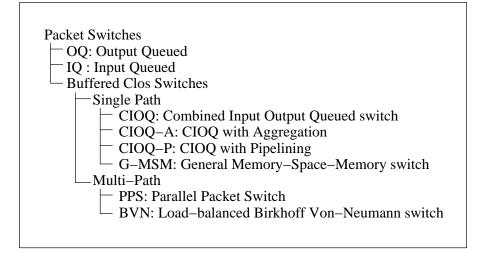

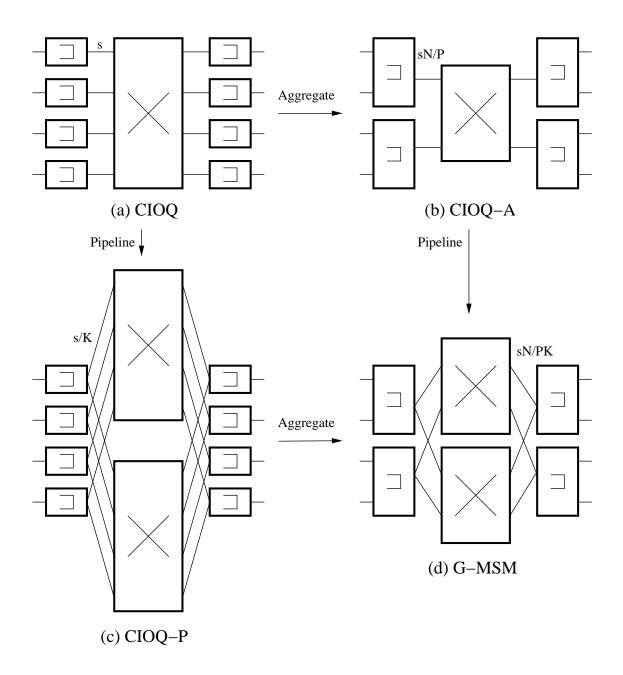

Switches with the output-queueing (OQ) discipline, in theory, provide the best performance in terms of throughput as well as QoS, but do not scale in capacity with increasing rates and port counts. Input-queued (IQ) switches, on the other hand, scale better but require complex arbitration procedures, sometimes impractical, to achieve the same level of performance. We leverage the state-of-the-art in OQ and IQ switching systems and establish a new taxonomy for a class of three-stage packet switches, which we call *Buffered Clos Switches*. The taxonomy is created by augmenting existing switching elements with *aggregation, pipelining and parallelization* techniques. This offers a switch designer several alternatives, each driven by specific design and re-use constraints, to build a high-capacity switch composed of lower-capacity basic elements.

We also present a formal framework for optimal packet-switching performance, in order to uniformly characterize the capabilities of the switches in the class. The optimality is based on establishing *functional equivalence* of a given switch and its associated arbitration algorithms with a well-understood ideal switch. For the items in the above taxonomy, we demonstrate how some existing algorithms perform with respect to the optimality criteria, and then augment the state-of-the-art by presenting algorithms and analytical results for stricter equivalence with an ideal switch.

# Contents

| List of I | ligures                           | V  |

|-----------|-----------------------------------|----|

| List of 7 | fables                            | ix |

| Preface   |                                   | xi |

| Chapter   | r 1 Introduction                  | 1  |

| 1.1       | Motivation                        | 3  |

| 1.2       | Contributions                     | 6  |

|           | 1.2.1 Applicability and Scope     | 7  |

| 1.3       | Organization                      | 9  |

| Chapter   | r 2 Switching Model               | 11 |

| 2.1       | Switching Basics: Overview        | 11 |

|           | 2.1.1 Circuits: Blocking          | 11 |

|           | 2.1.2 Packets: QoS and Throughput | 13 |

| 2.2       | Notions of Optimal Performance    | 14 |

| 2.3       | Forwarding Models                 | 18 |

| 2.4       | Building Blocks                   | 21 |

| 2.5       | Common Existing Switches          | 26 |

| Chapter   | r 3 Formal Methods in Switching   | 30 |

| 3.1       | Clos Network                      | 30 |

| 3.2     | Matchi  | ing Algorithms for Input-Queued Switches | 34  |

|---------|---------|------------------------------------------|-----|

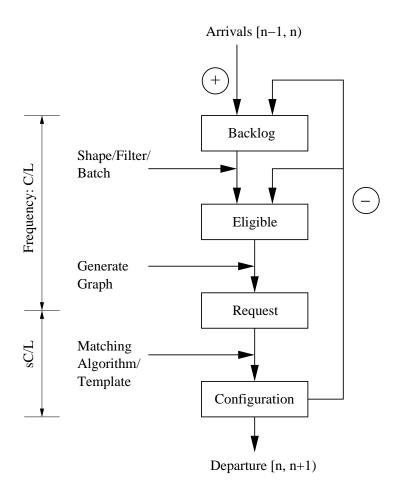

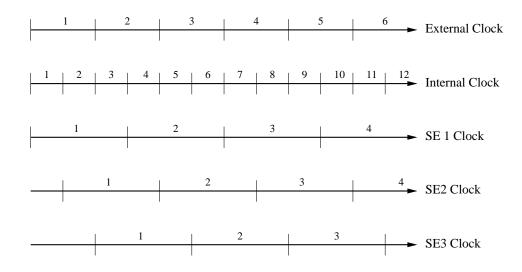

|         | 3.2.1   | Switch Control Loop                      | 35  |

|         | 3.2.2   | General Matching Techniques              | 37  |

|         | 3.2.3   | Deterministic Properties                 | 42  |

|         | 3.2.4   | Stochastic Stability                     | 48  |

|         | 3.2.5   | Work Conservation and Exact Emulation    | 55  |

|         | 3.2.6   | Low-complexity Matchings                 | 58  |

| 3.3     | Throug  | ghput and QoS in Packet Switching        | 63  |

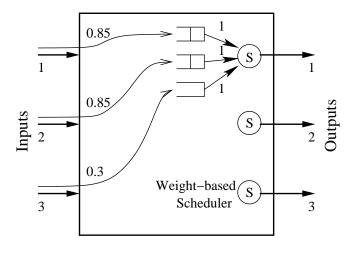

|         | 3.3.1   | Integrated Matchings                     | 63  |

|         | 3.3.2   | Hierarchical Switch Scheduling           | 65  |

|         | 3.3.3   | Memory Element QoS                       | 68  |

| 3.4     | Summa   | ary                                      | 73  |

| Chapter | r4 Bu   | ffered Clos Switches: A Framework        | 75  |

| 4.1     | BCS T   | axonomy                                  | 75  |

|         | 4.1.1   | Multi-module Architecture                | 78  |

|         | 4.1.2   | Feasible Implementations                 | 81  |

| 4.2     | Functio | onal Equivalence                         | 88  |

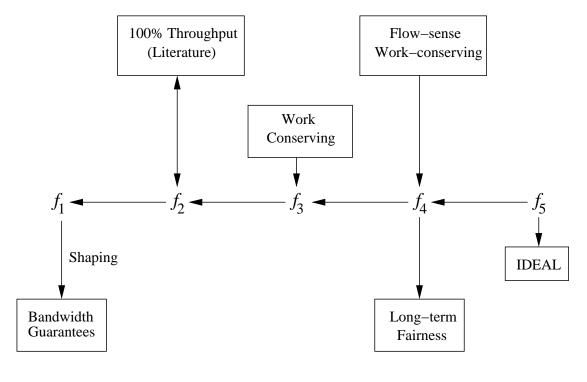

|         | 4.2.1   | Levels of Emulation                      | 89  |

|         | 4.2.2   | Meaning of Equivalence                   | 91  |

|         | 4.2.3   | Existing Results                         | 96  |

| 4.3     | Summa   | ary                                      | 97  |

| Chapter | r5 Co   | mbined Input-Output Queueing             | 98  |

| 5.1     | Maxim   | al Matching: Application to QoS          | 99  |

|         | 5.1.1   | Clos Networks: Space-Time Duality        | 101 |

|         | 5.1.2   | Packet-switching Equivalent              | 104 |

|         | 5.1.3   | Bandwidth and Delay Guarantees           | 105 |

| 5.2     | Critica | l Matching Algorithms                    | 109 |

|         | 5.2.1   | Deterministic Properties                 | 110 |

|         |         |                                          |     |

|         | 5.2.2    | Stability without Speedup                     | 115 |

|---------|----------|-----------------------------------------------|-----|

| 5.3     | Unifor   | m Traffic: Sub-maximal Perfect Sequence       | 121 |

|         | 5.3.1    | SPS Matching                                  | 122 |

|         | 5.3.2    | Online Variants                               | 124 |

| 5.4     | Maxim    | nal Matching for Inadmissible Traffic         | 126 |

|         | 5.4.1    | Bounded Arrivals and Statistical Multiplexing | 127 |

|         | 5.4.2    | Matching on Pruned Requests                   | 130 |

|         | 5.4.3    | Stochastic Stability                          | 132 |

| 5.5     | Strict I | Relative Stability                            | 135 |

|         | 5.5.1    | Shortest Output-Queue First                   | 139 |

|         | 5.5.2    | Alternative Approaches                        | 145 |

| 5.6     | Putting  | g it Together: Switched Fair-Airport Policies | 147 |

|         | 5.6.1    | Multi-phase Combination                       | 148 |

|         | 5.6.2    | Exclusive Combination                         | 150 |

| 5.7     | Extens   | ions to Multicast Traffic                     | 152 |

| 5.8     | Summ     | ary                                           | 155 |

| Chapter | :6 CI    | OQ: Aggregation and Pipelining                | 157 |

| 6.1     |          | gation                                        | 158 |

|         | 6.1.1    | Queueing Strategies                           |     |

|         | 6.1.2    | Shadowing a CIOQ                              |     |

|         | 6.1.3    | Low-complexity Matchings                      | 170 |

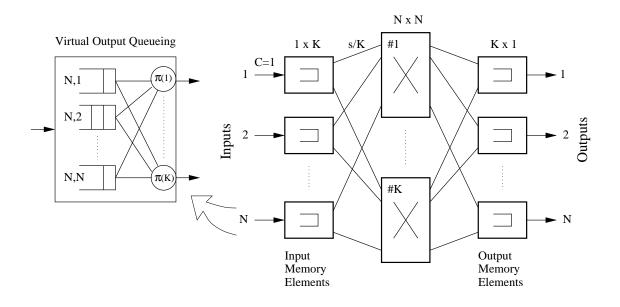

| 6.2     | Spatial  | Pipelining                                    | 183 |

|         | 6.2.1    | Shadowing a CIOQ                              | 185 |

|         | 6.2.2    | Concurrent Dispatch                           | 188 |

|         | 6.2.3    | Balanced Matchings                            | 196 |

| 6.3     | Genera   | al MSM Switches                               | 206 |

|         | 6.3.1    | Shadowing Approaches                          | 211 |

|         | 6.3.2    | Matching on Virtual Element Queues            | 215 |

|         | 6.3.3    | Recursive G-MSM                               | 218 |

| 6.4      | Summa   | ary and Discussion                   | 221 |

|----------|---------|--------------------------------------|-----|

|          | 6.4.1   | Related Work                         | 224 |

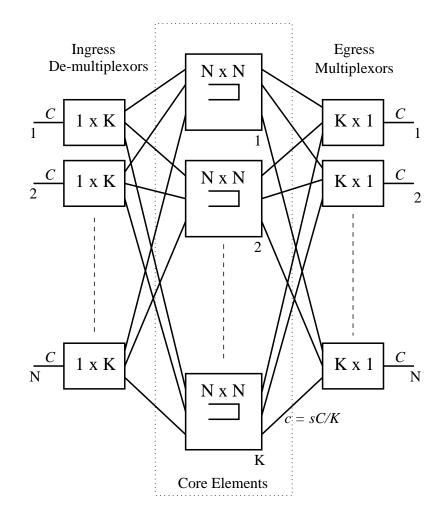

| Chapter  | 7 Pai   | rallel Packet Switches               | 226 |

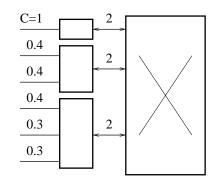

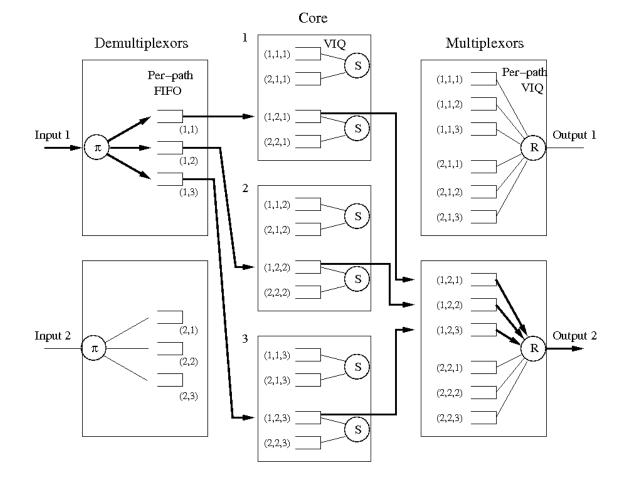

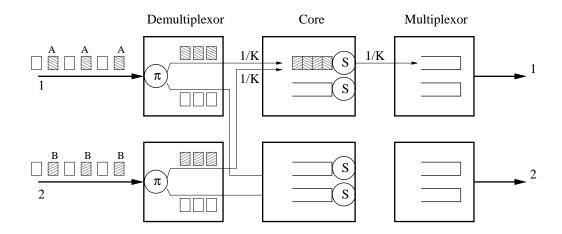

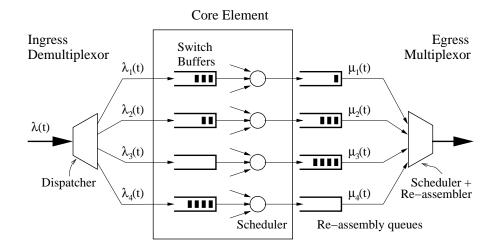

| 7.1      | Switch  | Architecture                         | 227 |

|          | 7.1.1   | Benefits                             | 230 |

|          | 7.1.2   | Queueing Strategies                  | 232 |

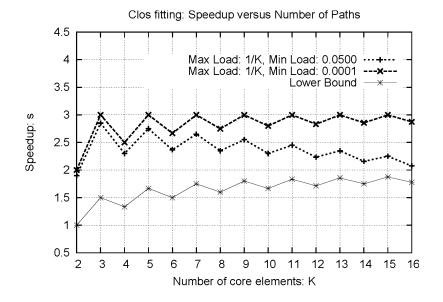

| 7.2      | Flow-b  | ased PPS                             | 238 |

| 7.3      | Cell-ba | used PPS                             | 246 |

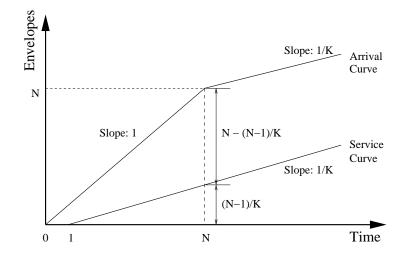

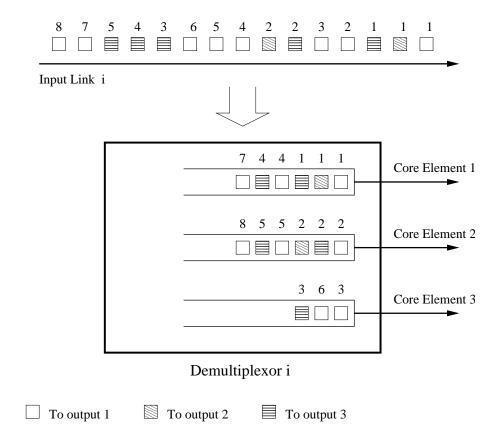

|          | 7.3.1   | Envelope Striping                    | 248 |

|          | 7.3.2   | Equal Dispatch                       | 253 |

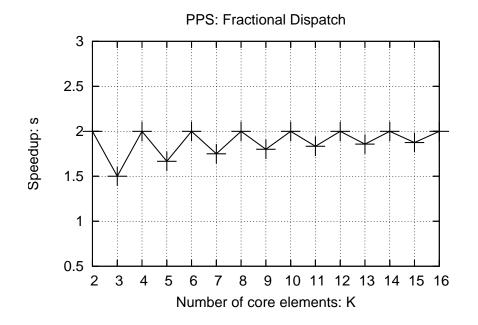

|          | 7.3.3   | Fractional Dispatch                  | 261 |

|          | 7.3.4   | Related Work                         | 263 |

| 7.4      | Sequen  | ce Control                           | 265 |

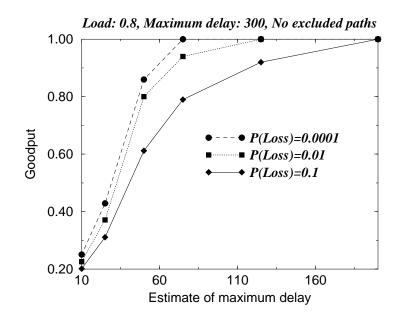

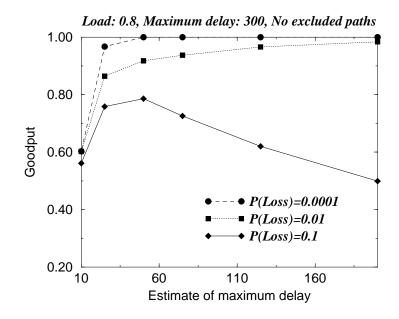

|          | 7.4.1   | Simulation Results                   | 269 |

| 7.5      | Summa   | ary and Discussion                   | 271 |

|          | 7.5.1   | Alternative Multi-path Architectures | 273 |

| Chapter  | · 8 Co  | nclusions                            | 276 |

| 8.1      | Summa   | ary of Contributions                 | 277 |

| 8.2      | Topics  | for Further Research                 | 280 |

| Bibliogr | aphy    |                                      | 284 |

# **List of Figures**

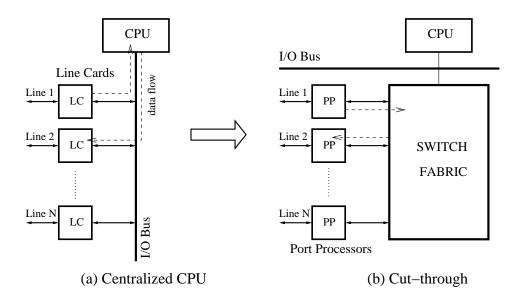

| 2.1  | Forwarding models: (a) Centralized CPU, (b) Cut-through                                                                                                             | 18 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

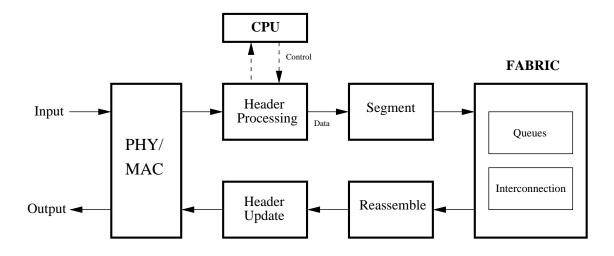

| 2.2  | Pipeline of a cut-through forwarding path                                                                                                                           | 20 |

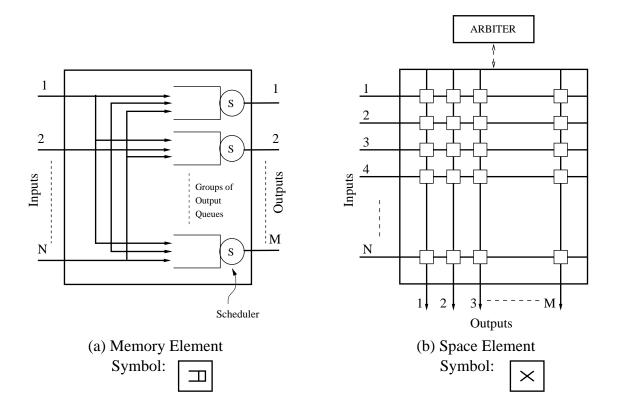

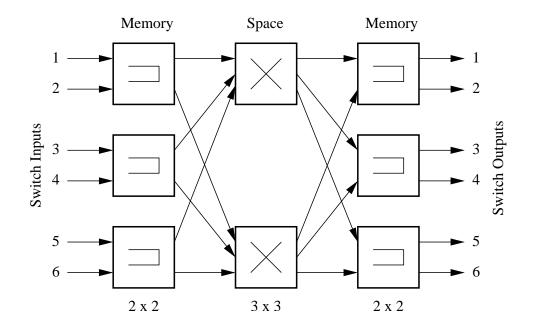

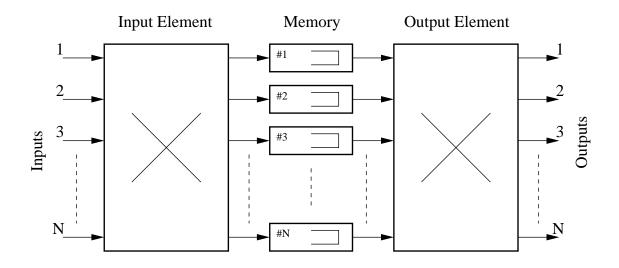

| 2.3  | Forwarding elements: (a) memory element, (b) space element                                                                                                          | 22 |

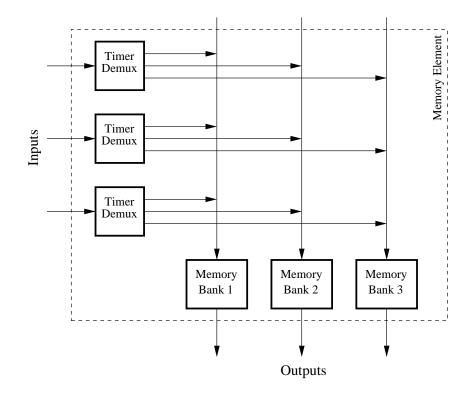

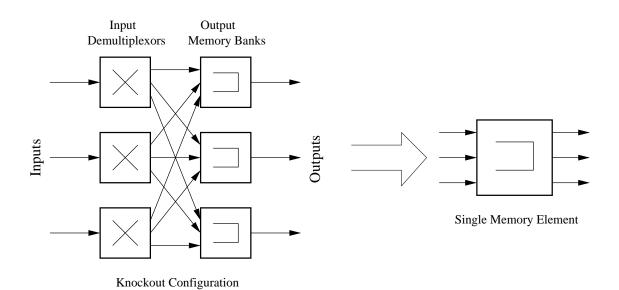

| 2.4  | Memory element implementation example: Knockout configuration                                                                                                       | 25 |

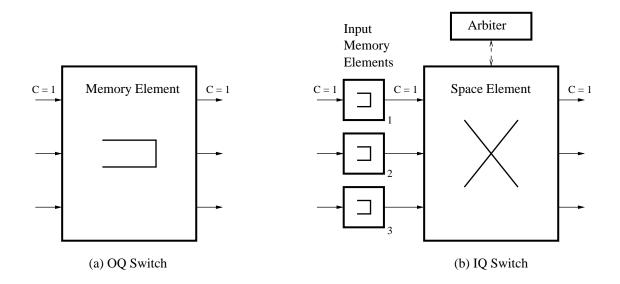

| 2.5  | Common existing switching models: (a) Output-queued, (b) Input-queued                                                                                               | 27 |

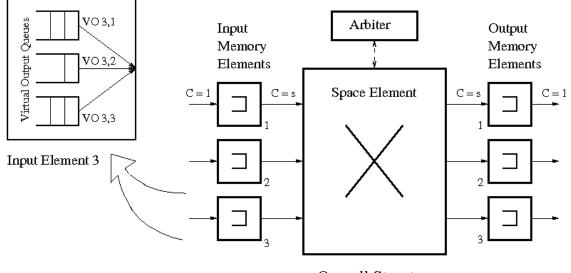

| 2.6  | A combined input-output queueing switch (CIOQ)                                                                                                                      | 28 |

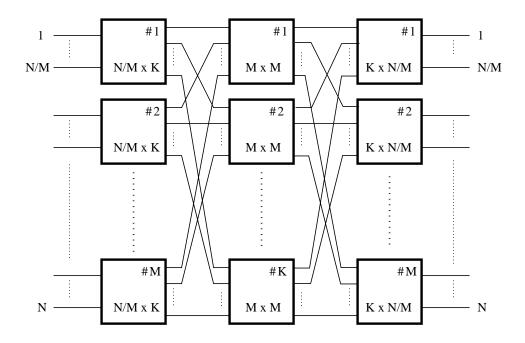

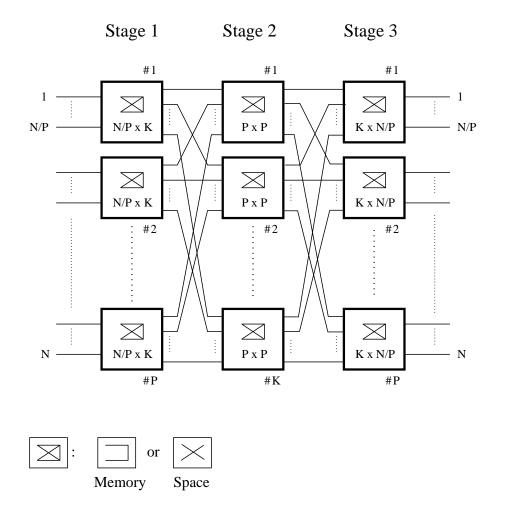

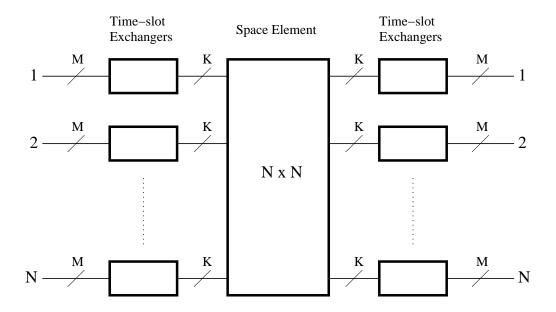

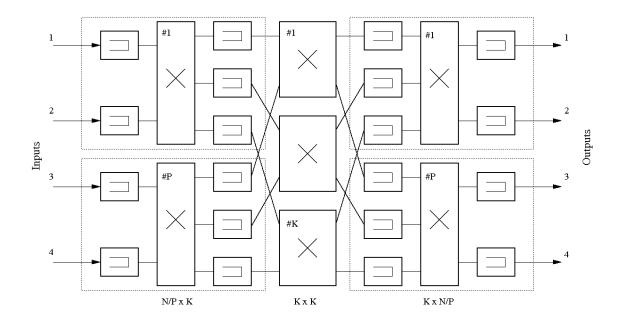

| 3.1  | An $N \times N$ Clos network $\ldots \ldots \ldots$ | 31 |

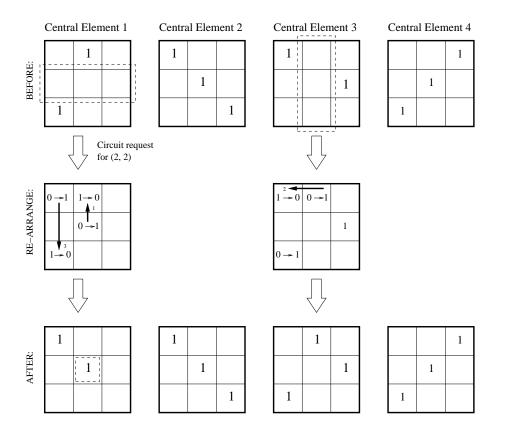

| 3.2  | Example of Slepian-Duguid-based circuit re-arrangement                                                                                                              | 34 |

| 3.3  | Control loop for an input-queued switch                                                                                                                             | 36 |

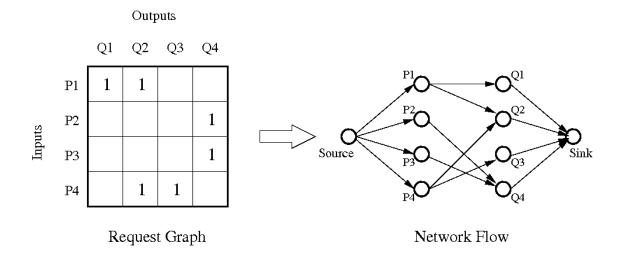

| 3.4  | Maximum Size Matching using an equivalent flow network                                                                                                              | 39 |

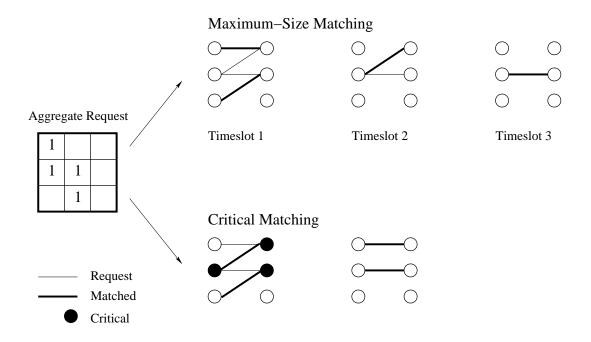

| 3.5  | Maximum Size Matching versus Critical Matching                                                                                                                      | 40 |

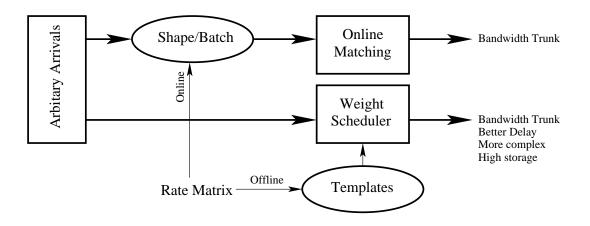

| 3.6  | Bandwidth and delay guarantees: Exact 100% throughput versus templates $\ldots$ .                                                                                   | 44 |

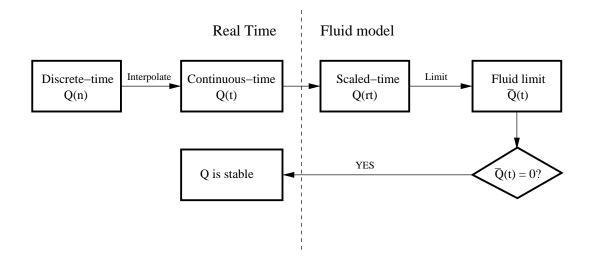

| 3.7  | Fluid limits: Steps in analyzing queue stability                                                                                                                    | 50 |

| 3.8  | Lowest Output Occupancy First: A maximal matching                                                                                                                   | 55 |

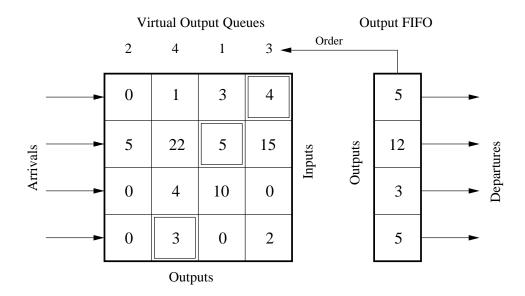

| 3.9  | EREW Maximal Matching: A distributed implementation                                                                                                                 | 59 |

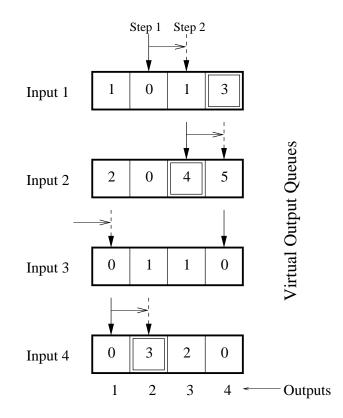

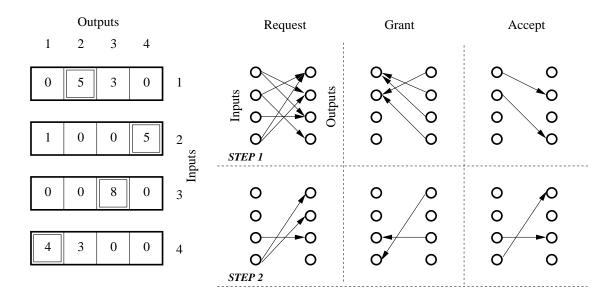

| 3.10 | Parallel Iterative Matching: Example of an RGA algorithm                                                                                                            | 60 |

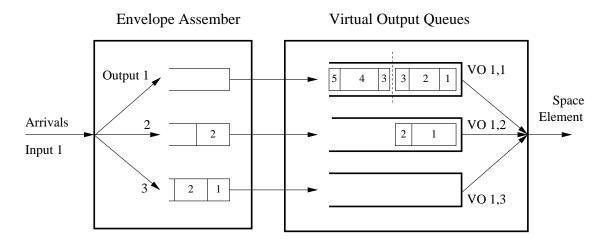

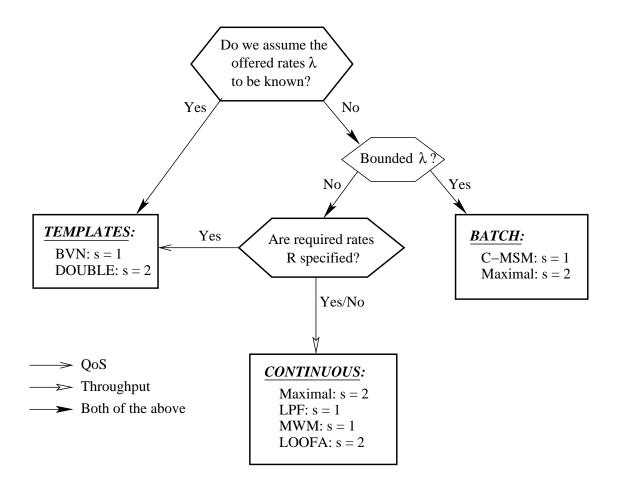

| 3.11 | Assembling large envelopes for low-frequency matchings                                                                                                              | 62 |

| 3.12 | A decision chart to select matchings based on requirements                                                                                                          | 64 |

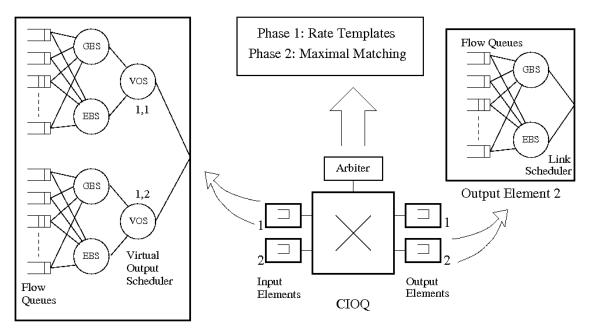

| 3.13 | Throughput and QoS for input-queued switches using distributed scheduling                                                                                           | 66 |

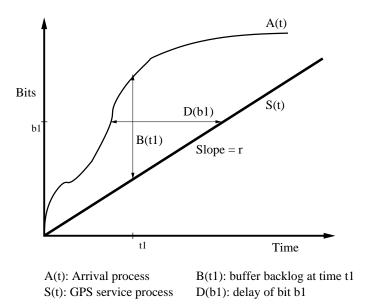

| 3.14 | GPS: Delays and backlog for a single flow                                                                                                                           | 70 |

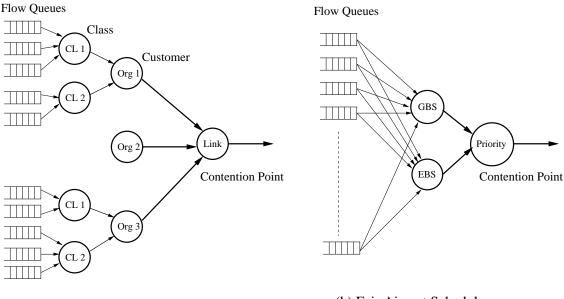

| 3.15 | Scheduler arrangements: (a) Hierarchical (b) Fair Airport                                                                                                           | 71 |

| 4.1  | A Knockout configuration as a network of logical elements                       | 6  |

|------|---------------------------------------------------------------------------------|----|

| 4.2  | General model of a buffered Clos switch                                         | 8  |

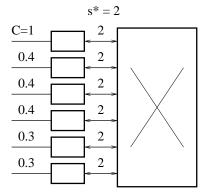

| 4.3  | BCS example: $(6, [MSM], 3, 2, 2)$                                              | 9  |

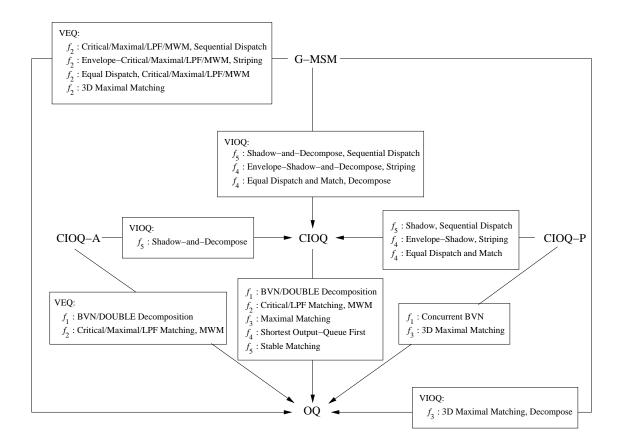

| 4.4  | The taxonomy of buffered Clos switches                                          | 32 |

| 4.5  | Single-path buffered Clos switches                                              | 34 |

| 4.6  | A parallel packet switch (PPS)                                                  | 37 |

| 4.7  | Example: Work-conservation does not lead to strict relative stability 9         | 3  |

| 4.8  | Relationship between various performance measures                               | 94 |

| 5.1  | A circuit Clos network: Time version                                            | 0  |

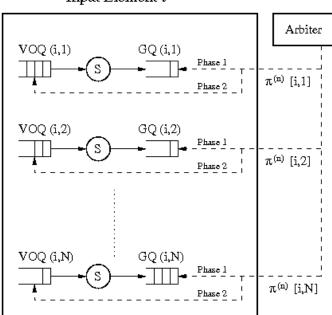

| 5.2  | CIOQ: Virtual output queues and guaranteed queues                               | 15 |

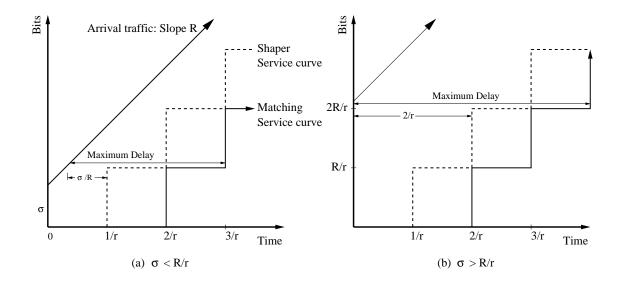

| 5.3  | Maximum delay for leaky-bucket constrained traffic under maximal matching 10    | 17 |

| 5.4  | Maximal matching for QoS: Emulating a GQ using counters                         | 18 |

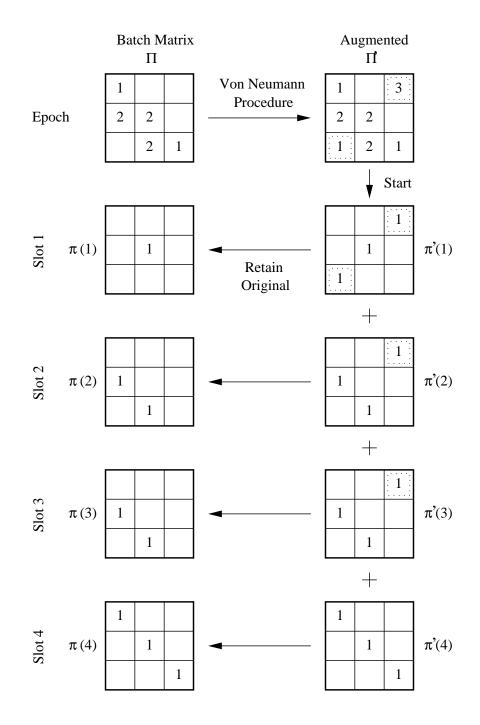

| 5.5  | Algorithm for generating a batch-mode critical matching                         | 1  |

| 5.6  | Example of a sequence of non-maximum critical matchings                         | 3  |

| 5.7  | Critical matching for QoS: Emulating a shaper using counters                    | 4  |

| 5.8  | Algorithm for generating a continuous-mode critical matching                    | 7  |

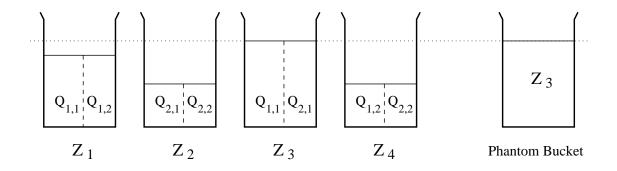

| 5.9  | Critical matching: Buckets of line sums                                         | 8  |

| 5.10 | Uniform traffic: A repeating sequence of perfect templates                      | 2  |

| 5.11 | EREW sub-maximal matching: Online generation of a perfect sequence 12           | 5  |

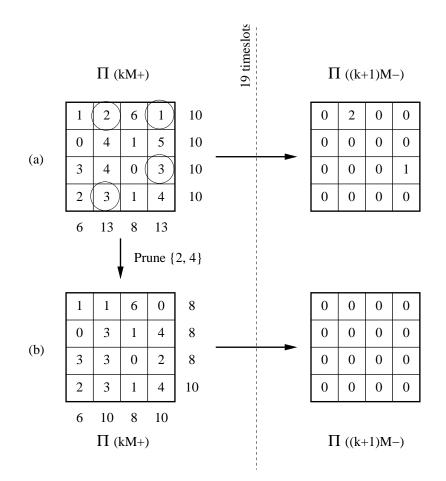

| 5.12 | Example: Batch-mode matching for inadmissible traffic                           | 8  |

| 5.13 | Batch-mode maximal matching with residue management for inadmissible traffic 12 | 9  |

| 5.14 | Batch-mode critical matching with pruning for inadmissible traffic 13           | 1  |

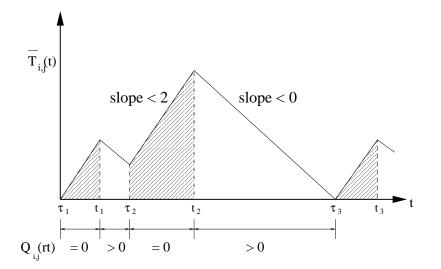

| 5.15 | How $\overline{T}_{i,j}(t)$ varies with t based on $Q_{i,j}(rt)$                | 4  |

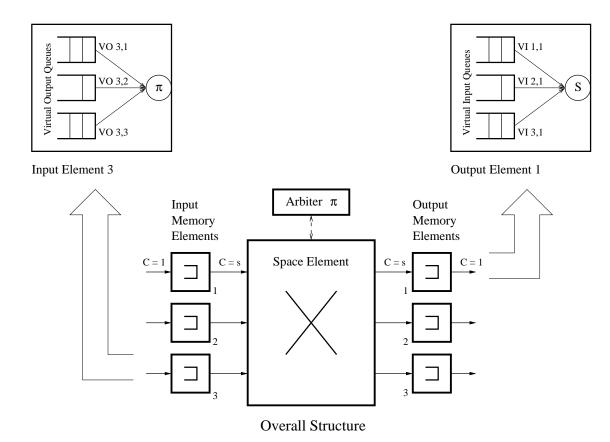

| 5.16 | A CIOQ switch with virtual input queueing in the output elements                | 6  |

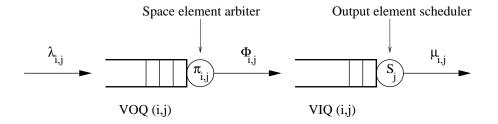

| 5.17 | A CIOQ switch as a set of tandem queues                                         | 7  |

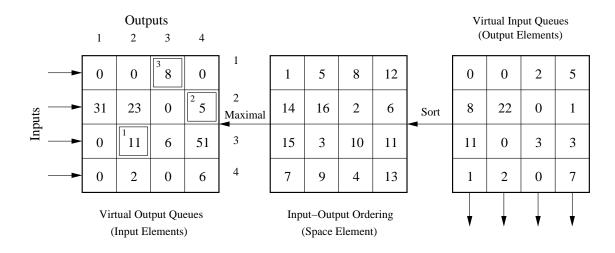

| 5.18 | Shortest output-queue first (SOQF) maximal matching                             | 8  |

| 5.19 | Example: SOQF maximal matching algorithm                                        | 0  |

| 5.20 | Imaginary queue system for non-conforming flows with stable output queues 14    | .2 |

| 5.21 | A backpressure-based approximation of SOQF                                      | 7  |

| 5.22 | SFA policy using a multi-phase combination of matchings                                                                                                            |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.23 | SFA policy using an exclusive combination of matchings                                                                                                             | 150 |

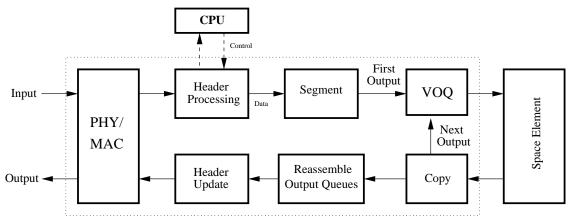

| 5.24 | Forwarding-path pipeline for multicast recycling support                                                                                                           | 153 |

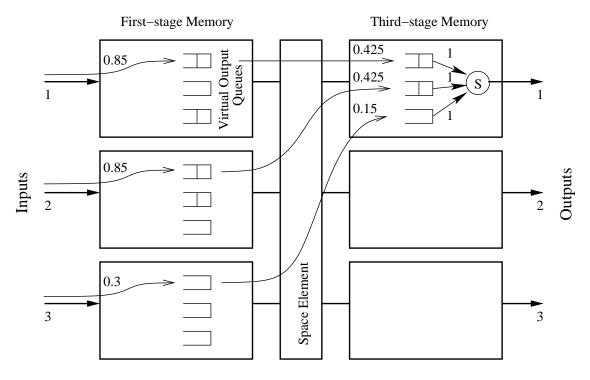

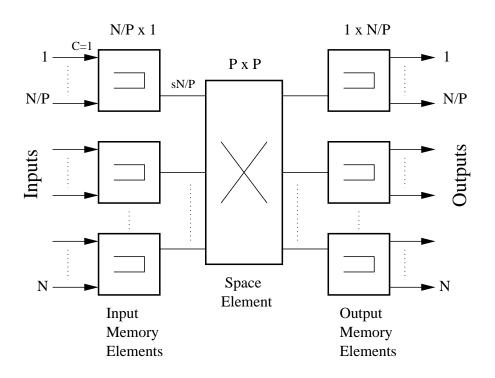

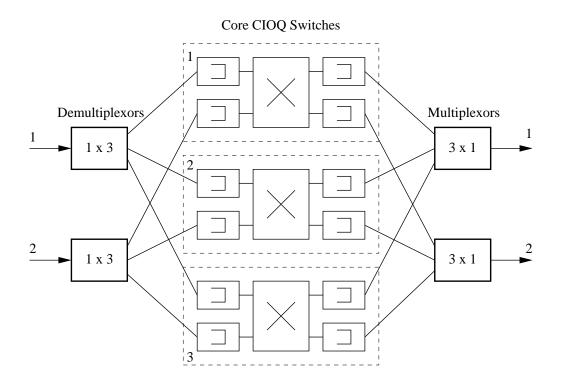

| 6.1  | CIOQ-A: CIOQ switch with aggregation                                                                                                                               | 158 |

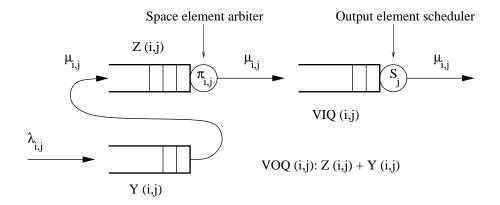

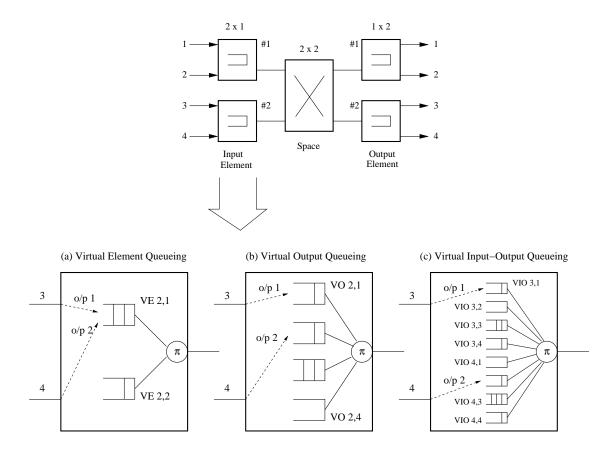

| 6.2  | Different queueing strategies for CIOQ-A switches                                                                                                                  | 160 |

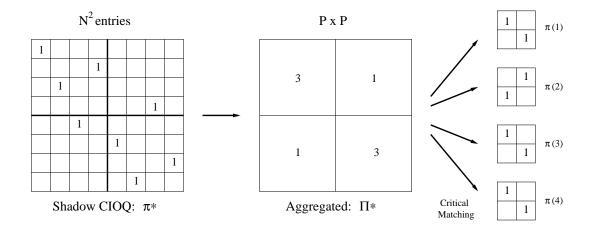

| 6.3  | CIOQ-A: Emulating a CIOQ using shadowing and decomposition 1                                                                                                       | 163 |

| 6.4  | CIOQ-A: Emulating a CIOQ using shadowing and decomposition 1                                                                                                       | 164 |

| 6.5  | CIOQ-A: Batch-mode shadowing and decomposition to emulate a CIOQ with lag                                                                                          | 168 |

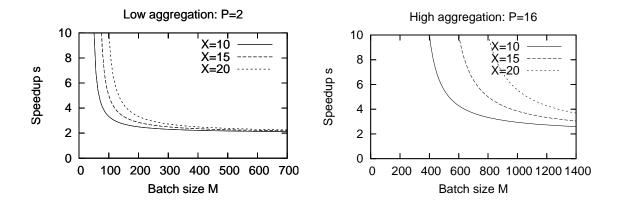

| 6.6  | CIOQ-A shadowing: Relationship between speedup and batch-size                                                                                                      | 171 |

| 6.7  | CIOQ-A: Direct matching on virtual element queues                                                                                                                  | 173 |

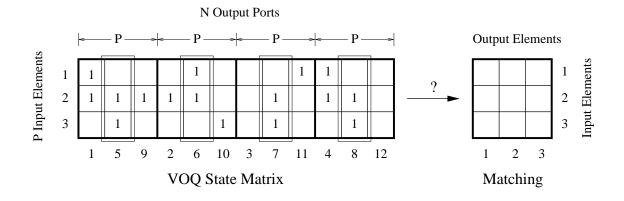

| 6.8  | CIOQ-A: How do we generate a $P \times P$ matching from a $P \times N$ queue state? 1                                                                              | 175 |

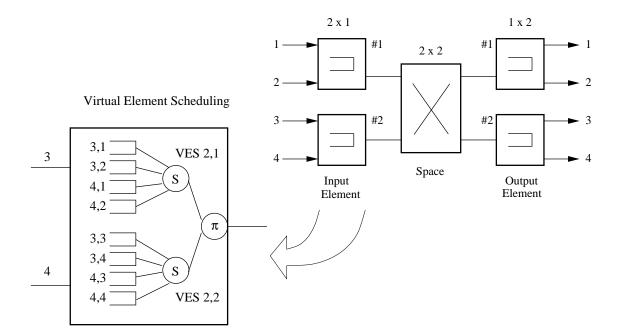

| 6.9  | CIOQ-A: Replacing a VEQ with a virtual element scheduler                                                                                                           | 177 |

| 6.10 | Example of a two-dimensional ${\cal O}(1)$ matching in CIOQ-A for uniform traffic $~$ .                                                                            | 179 |

| 6.11 | The CIOQ-A architecture applied to a switch with heterogeneous links 1                                                                                             | 182 |

| 6.12 | CIOQ-P: CIOQ switch with spatial pipelining                                                                                                                        | 184 |

| 6.13 | Staggered timeslots in a CIOQ-P switch: $s = 2, K = 3 \dots \dots$ | 185 |

| 6.14 | CIOQ-P: Emulating a CIOQ using shadowing and sequential dispatch 1                                                                                                 | 187 |

| 6.15 | CIOQ-P: Emulating a CIOQ using a concurrent matching                                                                                                               | 189 |

| 6.16 | Best-fit assignment of BVN templates to $K$ space elements $\ldots$ $\ldots$ $\ldots$ 1                                                                            | 191 |

| 6.17 | Concurrent SPS matching: EREW sub-maximal implementation                                                                                                           | 193 |

| 6.18 | A three-dimensional EREW concurrent matching for CIOQ-P                                                                                                            | 194 |

| 6.19 | 3D maximal matching: A cube of desynchronized pointers                                                                                                             | 195 |

| 6.20 | CIOQ-P: Emulating an envelope-based CIOQ matching using striping 1                                                                                                 | 197 |

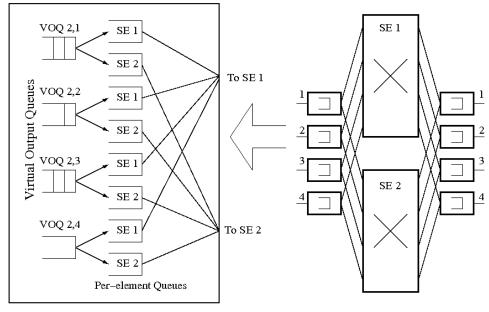

| 6.21 | CIOQ-P: Per-element virtual output queues                                                                                                                          | 200 |

| 6.22 | CIOQ-P: Emulating a CIOQ using equal dispatch                                                                                                                      | 202 |

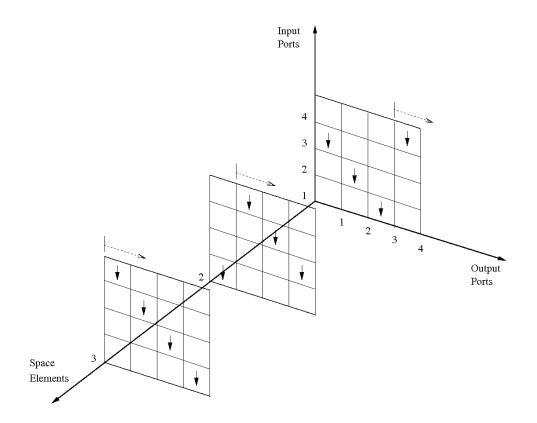

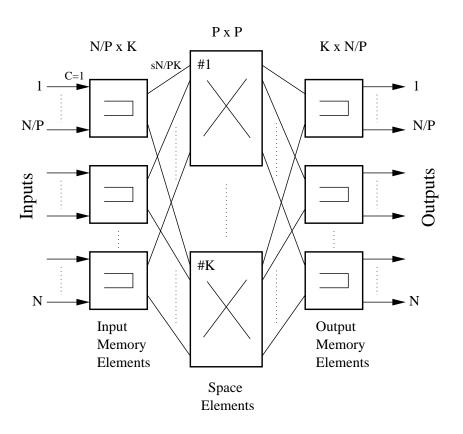

| 6.23 | G-MSM: CIOQ switch with aggregation and pipelining                                                                                                                 | 207 |

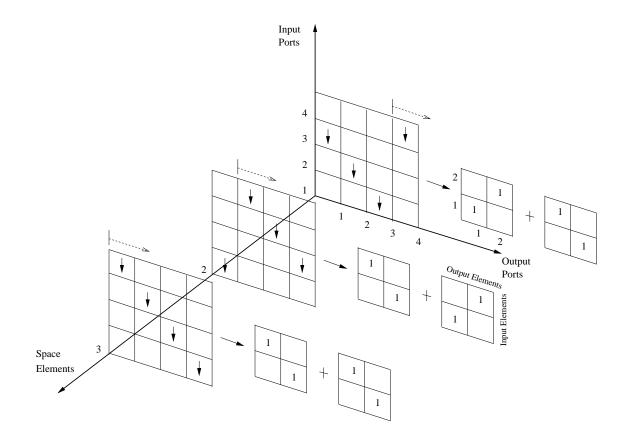

| 6.24 | G-MSM: Combination methods based on shadowing and decomposition 2                                                                                                  | 212 |

| 6.25 | G-MSM: 3D maximal matching with critical decomposition, $P = 2, K = 3$ 2                                                                                           | 214 |

| 6.26 | G-MSM: Combination methods for matching on virtual element queues 2                                                                                                | 216 |

| 6.27 | Recursive G-MSM switch: $N = 4, P = 2, K = 3 \dots 218$                   |

|------|---------------------------------------------------------------------------|

| 6.28 | Functional equivalences for single-path buffered Clos switches            |

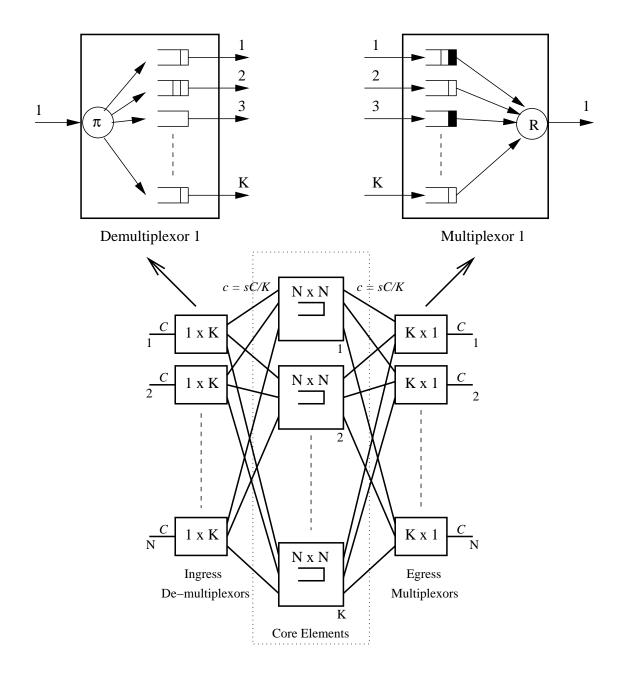

| 7.1  | A parallel packet switch (PPS) with load balancers and re-assemblers      |

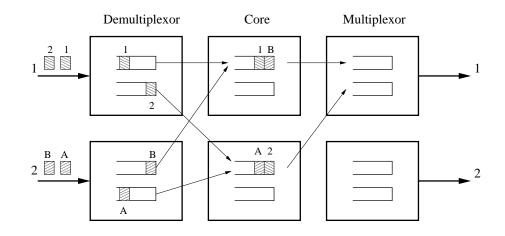

| 7.2  | A $2\times2$ PPS with CIOQ switches for central memory elements           |

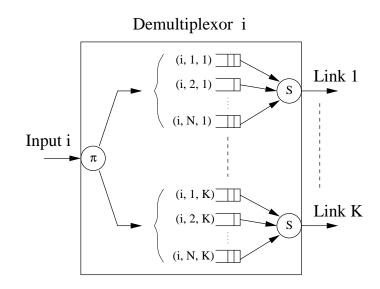

| 7.3  | Ingress demultiplexor with per-path virtual output queueing               |

| 7.4  | PPS: FIFO in the core may be incompatible with a buffered first stage 234 |

| 7.5  | A PPS with virtual input queues in the core elements and multiplexors 236 |

| 7.6  | Flow-based PPS: Static dispatch method                                    |

| 7.7  | Clos fitting in PPS: Effect of unbalanced load on speedup                 |

| 7.8  | Cell-based PPS: Round-robin on arrivals leads to instability              |

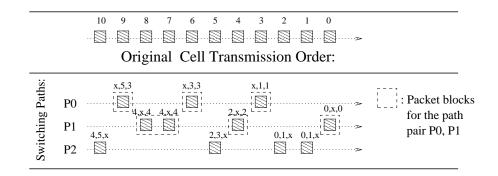

| 7.9  | Cell-based PPS: Striping envelopes across the core elements               |

| 7.10 | Arrival and service curves for envelopes in a PPS with striping 250       |

| 7.11 | Cell-based PPS: Per-flow equal dispatch across core elements              |

| 7.12 | Example of per-flow equal dispatch in a PPS with $N = 3, K = 3 \dots 256$ |

| 7.13 | Cell-based PPS: Per-flow fractional dispatch across core elements         |

| 7.14 | PPS: Speedup required for fractional dispatch                             |

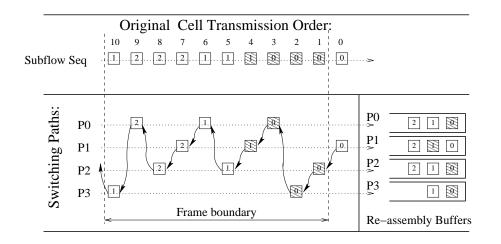

| 7.15 | Sequence control using SCIMA                                              |

| 7.16 | Sequence control using the rank-based protocol                            |

| 7.17 | The split flow model for sequence-control analysis                        |

| 7.18 | Performance of the rank-based protocol                                    |

| 7.19 | Performance of SCIMA                                                      |

| 7.20 | A load-balanced Birkhoff-Von Neumann switch                               |

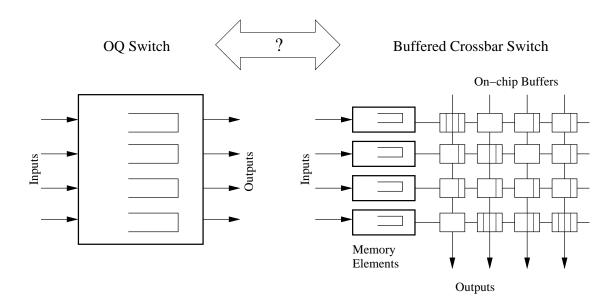

| 8.1  | Is a buffered crossbar functionally equivalent to an OQ switch?           |

# **List of Tables**

| 1.1 | Common measures for packet switching performance                             | 5   |

|-----|------------------------------------------------------------------------------|-----|

| 2.1 | Forwarding elements: Properties and constraints                              | 24  |

| 3.1 | General matching techniques and their complexity                             | 42  |

| 3.2 | Deterministic properties of popular matching algorithms                      | 47  |

| 3.3 | VOQ stability for admissible arrivals using popular matching algorithms      | 53  |

| 3.4 | Algorithms for emulation of a reference OQ switch                            | 58  |

|     |                                                                              |     |

| 4.1 | Feasibility of BCS implementations                                           | 81  |

| 4.2 | Properties of single-path BCS designs                                        | 86  |

| 5.1 | SFA: Speedup required to simultaneously provide QoS and optimal throughput . | 151 |

| 6.1 | Shadowing in CIOQ-A: Speedup required for throughput optimization            | 166 |

| 6.2 | CIOQ-A: Arbitration complexity of the shadow-and-decompose method            | 167 |

| 6.3 | CIOQ-A: Arbitration complexity for VEQ matching                              | 176 |

| 6.4 | G-MSM: Equivalence with CIOQ, and complexity for various combinations 2      | 210 |

| 6.5 | Combination method for a 7-stage recursive G-MSM switch                      | 220 |

| 7.1 | Sequence Control: Dependence on loss bounds and delay estimates              | 269 |

# Preface

The design and analysis of scalable packet switches is now a mature field, thanks to several pioneering contributions by the switching research community in the late 1990's. This was fueled partly by a quest for the biggest and most powerful switching system during the telecommunications boom visited upon us in that period. The time is now ripe to further the maturation process by lending the field a semblance of formality and rigor common in classical circuit switching. Motivated by this goal, I present here a compendium of techniques and analyses that may be used by switch designers to methodically construct and study high-capacity switches in a formal and unambiguous framework.

My choice to pursue this subject matter was not entirely coincidental. I was very fortunate to be part of the architecture team of three generations of the best-selling Atlanta<sup>TM</sup> switching chip-set at Bell Labs. Most of the original work presented here was indeed inspired by the research conducted and lessons learned in the 1998–2002 time-frame while working on that and related projects. The delayed publication of the material, on my part, may largely be attributed to some entrepreneurial adventures in the interim.

## Acknowledgments

Several people deserve my sincere gratitude for supporting this non-linear effort. First of all, I would like to thank my advisor Prof. Henning Schulzrinne for his invaluable help and encouragement, and my co-advisor, Dr. Fabio Chiussi, who mentored me rather admirably during my years at Bell Labs. Thanks are also due to Prof. Ed Coffman, Prof. Vishal Misra and Prof. Dan Rubenstein for being part of my dissertation committee. This work was partially supported by the Lucent doctoral scholarship, for which I am thankful to the erstwhile Lucent management.

Many of the ideas here were influenced by numerous engaging discussions with my excolleagues and fellow researchers at Bell Labs, while working with the Atlanta/ $\pi$  and Packetstar teams, in the good old days. Specifically, I would like to thank Alberto Brizio, Abhijit Choudhury, Andrea Francini, Lampros Kalampoukas, Denis Khotimsky, Jonathan Rosenberg, Sheng Shen, Dimitrios Stiliadis and Bernhard Suter for always sharing their expertise, whenever I needed it. I am grateful to the Invento Networks team, who kept life interesting and came along for a ride the last two years. Special thanks are due to Dave Bartolini, Bob MacDonald and Bob Power for spending time with me and helping me learn newer tricks.

Finally, I am thankful to my dear wife Vaishali for her continued support, motivation and, in general, an upbeat attitude towards everything, not to mention her invaluable help in the grammatical editing of this dissertation.

> Santosh Krishnan May 2006

To Vaishali

# Chapter 1

# Introduction

The telecommunications industry has witnessed a dramatic increase in packet-based network deployments over the past decade. Such deployments have spanned fiber-based wide and metropolitan area networks, as well as various flavors of wireline and wireless access networks. The enterprise and data-center industries have seen a similar proliferation in the form of packet-based local area, storage and cluster computing networks. Increasing traffic carried over such networks has propelled the demand for high-capacity packet-switching systems.

The networking protocols supported by these systems vary widely from connectionoriented to connectionless ones depending upon deployment. Legacy Asynchronous Transfer Mode (ATM) and the emerging Multi-Protocol Label Switching (MPLS) [94] typically provide transport services within network domains, the former still prevalent in DSL and cellular access networks and the latter finding favor in service-provider metropolitan and core networks. The ubiquitous Internet Protocol (IP) and Ethernet continue to support end-user connectivity, often overlayed on the above transport networks. Elsewhere, purpose-built technologies such as Infiniband and Myrinet provide interconnectivity for storage networks and cluster computing.

Independent of the specific protocol supported, and the diversity of names given to the respective systems, e.g., multi-service switch, router and packet multiplexor, the core of such systems consists of a *forwarding path* that transfers traffic units from the input to the output interfaces. In the interest of protocol agnosticity, we refer to all such traffic units as *packets* in the generic sense, and the systems as *packet switches*. The capacity of a packet switch depends

upon the number of supported interfaces, also known as port count, and the transmission rates of those interfaces. Two commonly used metrics for switching capacity include *forwarding* and *processing* capacity. The former is measured as the amount of cumulative traffic that may be instantaneously dispatched by the switch, e.g., a switch with 16 full-duplex interfaces each operating at 10 Gb/s has a nominal capacity of 160 Gb/s. Processing capacity is measured as the number of packets that may be processed in unit time, e.g., if the above switch can tolerate a minimum packet size of 125 bytes, the processing capacity on each interface would be 10 million packets per second (pps).

The need for higher switching capacity stems from both higher port counts due to dense deployments, and higher transmission rates enabled by improvements in the physical layer. A typical high-end IP router in production today (e.g., Cisco 12000 series, Juniper T-series) supports 10-20 ports, each operating at 10-40 Gb/s, thus requiring a forwarding capacity of several hundred Gb/s. Since IP packet sizes have not changed materially with the increasing rates, assuming a minimum packet size of 64 bytes, the router would require a processing capacity of about 20-80 million pps per interface. These represent more than a tenfold increase in capacities since a decade ago. This trend is expected to continue, albeit at a slower pace compared to the past decade, driven by a greater number of high-speed fiber/DSL ports at the edges of the network, the anticipated adoption of 10-G Ethernet in the metropolitan area, and increasing OC-192 (10 Gb/s) and OC-768 (40 Gb/s) links in the core. A higher forwarding capacity imposes severe constraints on the construction of the switch, e.g., on the design of packet memories, interconnection network and arbitration logic, while a higher processing capacity constrains the complexity of the algorithms such as route determination and scheduling that must operate on a per-packet basis.

As an orthogonal trend, multimedia and other traditionally circuit-switched network services are being migrated to a converged packet-based network. Such services are characterized by traffic *flows* that require Quality of Service (QoS) in the form of bandwidth and delay guarantees. Examples of such flows include Voice-over-IP (VoIP) sessions, Video-on-Demand streams, and MPLS Virtual Private Network (VPN) tunnels providing multi-site office connectivity. While end-to-end QoS in an IP network remains a pipe-dream and is typically addressed by throwing additional capacity into the network, QoS capability is being slowly engineered into selected por-

#### Introduction

tions of the network. For example, the TR-58 specification of the DSL forum and the PacketCable specification of CableLabs allow for QoS provisioning of end-user flows in the access network. Elsewhere, QoS for aggregates of end-user flows are becoming common in MPLS-based transport networks. Consequently, the forwarding path of a modern packet switch needs to provide preferential treatment to specified flows so that their negotiated QoS requirements may be met.

While the increase in packet-based network traffic has been facilitated by enhancements in physical layer technologies and QoS capability has been addressed by advances in link scheduling, the forwarding path itself remains a bottleneck primarily because memory bandwidths have not experienced comparable improvements. Consequently, there is a continuing interest in building packet switches using multiple modules of lower capacities. This dissertation addresses the design and analysis of such multi-module switches. We present architectures that may be used to construct the forwarding path of a large-scale packet switch, and the associated algorithms to optimize throughput and provide QoS to the served traffic flows. Towards this goal, we propose a new taxonomy for a class of scalable switches, together with an analytical framework to characterize optimal performance for the algorithms employed within such switches.

### **1.1** Motivation

The design and analysis of classical multi-module circuit switches (see [45] for an overview) provide a historical precedence and inspiration for this work. Scalable switches, using an interconnection network of smaller components, were proposed to decrease the number of expensive electronic crosspoints within a large switch. Notable examples of such architectures include the Banyan, Benes, Clos and Cantor networks. This work benefited immensely from a wellestablished performance framework, namely, the property of *blocking*, which characterized the performance of a given architecture in isolation from the properties of specific circuit arrival processes. Levels of blocking behavior, namely, strict-sense, wide-sense and rearrangeable, allowed to accurately deduce the functional equivalence of a given design with an ideal single-stage switch, in terms of circuit admission capability. Such rigor and precision are lacking in prior packet-switching work.

Admittedly, significant progress has already been made towards the design of multi-

module packet switches in the form of combined input-output queueing (CIOQ) switches (e.g., see [24, 70]), memory-space-memory switches [19, 22], and more recently, parallel switches [50, 62] and load balanced Birkhoff-Von Neumann (BVN) [9] architectures. Such works have yielded several arbitration and load-balancing algorithms for the respective designs, yet, in the absence of a uniform performance framework, several diverse, often inadequate, measures and/or simulation results have been used to claim optimality, making it difficult to make fair comparisons between switches. This has likely restricted the practical implementations of sophisticated high-performance designs in the industry. For example, a recent survey [102] as well as a look at systems based on the standard Advanced Telecom Computing Architecture (ATCA) platform confirm that a majority of packet switches continue to adopt simple variations of the shared-memory output-queued (OQ) or a crossbar-based input-queued (IQ) design, often with unknown performance characterizations.

Among patently imperfect measures is a practice still prevalent in the industry to rig together an interconnection between the input and output interfaces and claim the nominal capacity, i.e., the sum of the interface rates, as the *throughput* of the system. For example, a number of so-called terabit routers are but multiple switching blades interconnected by a separate cluster controller switch. The mere fact that a path exists between any two interfaces of a system does not directly imply that the nominal rates can be sustained on each interface. Consequently, the advertised capacity of the system is rendered meaningless in engineering the network. Another approach, common in earlier ATM literature, is to quantify switching performance by deriving packet loss ratios in the finite buffers within the switch for specific arrival patterns. It can be argued that such ratios are primarily indicative of the arrival processes themselves, and not entirely meaningful in choosing a switch design. Fortunately, these approaches are falling out of favor in the modern literature, replaced by concepts such as non-blocking and 100% throughput. While the latter constitute a step in the right direction, they are not entirely satisfactory.

The concept of non-blocking, which is in reality a circuit-switching property, has been variously and often ambiguously applied to characterize a packet switch. One of its more reasonable interpretations is a switch that is non-blocking in structure, i.e., a design in which a path can always be found between an idle input-output interface pair. While this might be a necessary

#### Introduction

| Measure                               | Limitation                                               |

|---------------------------------------|----------------------------------------------------------|

| Full interconnection                  | Interface throughput not necessarily sustainable         |

| Loss ratios for finite switch buffers | Property of arrivals, not of the switch                  |

| Non-blocking structure                | Does not address throughput                              |

| 100% throughput                       | Does not address arbitrary, e.g., inadmissible, arrivals |

Table 1.1: Common measures for packet switching performance

condition to optimize throughput, it is not sufficient as evidenced by a simple crossbar switch, which is trivially non-blocking yet not necessarily optimal in throughput. A better measure is that of 100% throughput (example applications can be seen in [29, 70]), which refers to the ability of a switch to ensure stable queues for admissible traffic in the long term. Well-behaved traffic is taken for granted either via auxiliary admission control means or as a result of end-to-end flow control. While this approach comes closest in the literature to providing a meaningful performance framework, it does not address equivalence with an ideal switch for arbitrary, including inadmissible, traffic, leading sometimes to necessitate additional considerations such as starvation prevention. Table 1.1 summarizes these common measures and their limitations.

The above problems are compounded by a lack of clear demarcation between the logical architectures of packet switches, and their chosen implementations. For example, a classical  $N \times N$  OQ switch is logically similar in operation to several space-division multiplexed designs [110] such as the bus-matrix switch and the full-mesh switch each of which employs  $N^2$  disjoint paths, with respective queues, between the input-output pairs. A similar case can be made for a buffered crossbar switch, in which there has been some recent interest, which places those  $N^2$  queues at the crosspoints of a  $N \times N$  crossbar, with the main implementation concern being minimizing the on-chip queue sizes via backpressure to larger off-chip queues at the inputs. The logical similarity is due to the fact that in each of these designs, arriving packets can immediately be presented to the destination queues that are organized on a per-output basis, and each of those queues are random-accessible in the departure decisions. Our contention is that any analysis of such designs constitutes an analysis of the implementation and its associated trade-offs and not that of the logical switch architecture.

These considerations lead us to two important questions: what qualifies as the logical architecture of a multi-module packet switch, and what models can be used to characterize optimal performance of a packet switch design? Once these questions are answered, the remaining task would be to identify the algorithms that may be implemented to achieve such optimal performance. Prior taxonomical work [88] have covered these questions for ATM switch topologies, though most of the focus was on the structural blocking property of the interconnection network. Further studies (e.g., [12]) have dealt with the design and analysis of a specific class of Banyanbased topologies. Though such works, and others previously mentioned in this section, have enabled to implement practical multi-module switches, providing functional equivalence with an ideal switch remains an open topic of research for many of the simple non-blocking networks augmented with buffers at arbitrary points within them. This dissertation takes a small step in addressing that topic.

## **1.2** Contributions

The primary contribution of this work is a constructive approach to building a high-capacity packet switch, using stages of lower capacity memory and space elements. We restrict ourselves to designs that resemble the three-stage Clos network, augmented with buffers. For switches with this structure, which we call *Buffered Clos switches*, we establish a taxonomy of packet switch designs. Each item in the taxonomy is accompanied by the design and re-use constraints that it resolves, so that switch implementors may identify the most appropriate item to use. To accurately characterize the capabilities of the switches in the taxonomy, we introduce a new performance framework for packet switches based on the ability of their resident algorithms to achieve *functional equivalence* with an ideal switch. While some items in the classification are already addressed to a large extent in the literature, the taxonomy itself and the performance framework are novel. In addition to providing a road-map to construct scalable switches, this work allows to ascertain the properties of existing vendor equipment by inspecting the structure and the associated algorithms for functional equivalence.

To place this work in the context of existing results in the literature, we present it in a new perspective, namely, as an exercise in how formal methods from graph theory, combinatorics and

#### Introduction

stochastics may be beneficially used to design and analyze switching algorithms. This exposition is concentrated on IQ and CIOQ switches, which form the starting point of our taxonomy and the inspiration for our performance framework. For the heavily researched CIOQ switch, we augment the state of the art by presenting algorithms that may be used to achieve stricter equivalence with an ideal switch. We propose a new intuitive proof that shows how a CIOQ switch may be considered as an analog of the circuit Clos switch. This result is used to exhibit how simple matching algorithms may be used to achieve bandwidth and delay guarantees. We then present three new fundamental results on the throughput capability of such switches. Specifically, we prove that a class of critical matching algorithms ensures equivalence with an ideal switch without requiring internal speedup, and that well-chosen maximal matchings are sufficient for asymptotic emulation of an ideal switch even under inadmissible traffic.

Proceeding further in the above taxonomy, we present the design and analysis of CIOQ switches with *aggregation* and *pipelining*, two crucial ingredients to scaling. These fall into the category of what we call single-path buffered Clos switches. We show the application of these two transformations to convert a CIOQ switch, without losing performance, into general memory-space-memory switches. We present methods that shadow a CIOQ switch, combined with matrix decomposition to account for aggregation, and with sequential, balanced or concurrent dispatch methods to account for pipelining, in order to inherit the performance of the reference CIOQ switch. Some existing switches appear similar to these, nevertheless, the presented algorithms and analytical results are novel. Lastly, we propose and analyze a new *parallel* packet switch architecture, which belongs to what we call multi-path buffered Clos switches. We cover the topics of stable load balancing and sequence control for such switches. It should be noted that while all the contributions mentioned in this section are original, some of the accompanying results have already been published elsewhere by the author.

#### **1.2.1** Applicability and Scope

This work is restricted in several aspects to keep it tractable. We deal mainly with unicast traffic. While the ability to handle multicast traffic is certainly relevant to packet switching, it is not addressed with the same level of detail except, in some cases, to point out easily adaptable extensions. We also do not include specialized switching algorithms that may be used to optimize the performance for adaptive traffic such as TCP. Our assumption is that the presented performance framework by itself will be beneficial to adaptive traffic as well, and other mechanisms, such as active queue management, to enforce fairness among adaptive flows, can be added on to this work without much difficulty. In addition, we do not address the end-to-end network behavior and network engineering. Instead, we concentrate on individual node mechanisms whose suitability for end-to-end optimal behavior may be studied independently. This work is also agnostic of the protocol processing specifics and control-plane handling, e.g., signaling the flows for QoS, and route control.

This dissertation covers only the switching node architectures and algorithms. There are several simplifying assumptions that will restrict the direct application of this work to practical implementations. For example, the effect of finite-sized buffers is not explored in detail. For the most part, the buffers in the logical switching elements are considered to be infinite, with the assumption that the tails of the queue-length distributions may be used to yield packet loss ratios in actual designs. Similarly, the full effect of variable-sized packets, and the overhead of the associated segmentation and reassembly component, is not adequately addressed. We also admit that several of the presented algorithms are centralized in nature. The complexity of the logic as well as a requirement to build multi-board systems might necessitate non-trivial extensions to achieve a comparable distributed implementation. Consequently, this work should be treated as a theoretical advancement, which may be used as a guide to devise suitable heuristics to enable practical designs.

The author himself was responsible for several key components of the architecture of the commercial Lucent/Agere Atlanta(tm) chipset [19] and the protocol-independent ( $\pi$ ) chipsets [21, 22], all of which were based on memory-space-memory and buffered crossbar designs before those terms became fashionable in the literature. The author was also responsible for a prototype architecture of a parallel packet switch named  $\pi$ -group. While this dissertation does not cover any of those implementations in detail, those products provided proofs of concept for the ideas contained here.

### **1.3 Organization**

The remainder of this dissertation is organized as follows. Chapter 2 contains our view of the packet switching model. We introduce the basic logical building blocks that are meaningful for packet switching, namely, memory and space elements, and make a case for meaningful notions of optimal performance. The latter includes three basic propositions that encompass the QoS and throughput properties of a switch. These are presented before the chapter on literature in order to place the latter in proper perspective.

Chapter 3 covers the related work in switch design, including a short exposition of circuitbased Clos networks, and a main focus on the results in IQ and CIOQ packet switching. These are presented in a new context, namely, as a usage of formal methods from diverse mathematical areas to arrive at high-performance switching algorithms. We cover the question of how matching algorithms are devised for input-queued switches, and how those matchings have been applied to QoS and throughput performance in the prior art.

Chapter 4 presents our taxonomy of buffered Clos switches, and the new performance framework of functional equivalence. This is accompanied by a presentation of how existing results fit into the new framework. The taxonomy allows switch designers to assemble basic building blocks into sophisticated multi-module switch designs, while the framework of equivalence allows to accurately characterize and compare the performance of the algorithms implemented within such switches.

Chapter 5 augments the state-of-the-art of CIOQ switches, the first item in our taxonomy. We provide a proof of how a circuit Clos switch is analogous to a packet CIOQ switch, using which we exhibit how bandwidth and delay guarantees may be provided. On the throughput of such switches, we show that a class of critical matching algorithms ensure equivalence with an ideal switch for admissible traffic. Furthermore, we show that an existing class of simple algorithms, namely maximal matching, may be used for stricter equivalence with an ideal switch under partially admissible traffic, and present a specific maximal matching that ensures asymptotic emulation of the ideal for abritrary traffic, which solidifies this equivalence. Finally, the throughput and QoS results are combined to yield a unified matching framework.

Chapter 6 covers single-path buffered Clos switches, namely, switches with aggregation

and pipelining. We present and analyze matching algorithms for such switches, based on shadowing a high-performance CIOQ switch. The transitivity property of functional equivalence is applied to translate the optimal throughput and QoS results of CIOQ switches to such single-path designs. For switches with aggregation, we propose a shadow-and-decompose method, as well as a lower-complexity matching method, using a more efficient queueing strategy, in order to obtain performance comparable to CIOQ. Towards the same goal, for switches with pipelining, we propose and analyze sequential, concurrent and equal dispatch methods. To conclude, the possibility of recursively constructing switches with smaller components, using a larger number of stages, is briefly presented.

Chapter 7 contains the architecture and analysis of parallel packet switches, which are multi-path manifestations of buffered Clos switches. We propose load balancing algorithms for such switches and analyze their switching performance. We also cover issues unique to multi-path designs, primarily that of sequence control. For completeness, we include a short exposition on the other common multi-path design in the literature, namely, the BVN switch.

Chapter 8 presents the conclusions of this work, including problems that remained unaddressed and avenues for future research.

# Chapter 2

# **Switching Model**

We first overview the switching framework relevant to this work, including definitions of basic concepts such as contention, blocking and throughput, followed by a case for some meaningful notions of optimal performance. We then present models for the forwarding path of a packet switch, and their atomic logical building blocks. We briefly introduce the output-queued (OQ) and input-queued (IQ) switching models, the former representing the ideal reference switch for our performance framework.

## 2.1 Switching Basics: Overview

### 2.1.1 Circuits: Blocking

Circuit-based networks divide the physical communication media into units called *channels*. Depending upon the multiplexing technique, channels may correspond to timeslots, frequency bands, codes or wavelengths. A *circuit* is an end-to-end traffic pipe established by pre-determining the path to be traversed through the network, and assigning channels, if they are available, on the links that comprise the path. Traffic is segmented into *frames*, and each circuit switching node in the path transfers the frames that arrive on a given channel of an input link to the respective pre-established channel of an output link. Examples of such nodes include SONET switches based on electronic crossbars and WDM waveguide routers based on optical components such as tunable lasers and MEMS mirrors.

A *contention* is a condition in which more than one frame compete for a given link at the same instant. If this link belongs to the set of outputs of a switch, we refer to the condition as *external* contention. If it belongs inside the interconnection network of the switch, we refer to the condition as *internal* contention. Since channels are pre-established on every network link traversed by a circuit, there is no external contention and no inherent necessity to provide buffers for pending frames, other than for synchronization purposes. Consequently, the performance measures of interest in circuit switching include only the admissibility of circuits, or call-level behavior, and the capability to realize internal paths within the switch to accommodate admitted circuits. The former is studied using *loss models* [95], which characterize circuit acceptance probabilities based on the statistics of call arrivals and holding times, a celebrated example of which is the Erlang loss system used to engineer telephony networks. The latter is determined by the architecture of the switching node itself.

A circuit switch achieves maximum throughput as long as an internal path can be established for every circuit that is admitted solely on the basis of the available resources of the external links. Such a property, effectively, allows us to remove the specifics of the internal switch architecture from network engineering considerations, which then depend only on the available link resources in the network. A switch that satisfies this property is referred to as *non-blocking*. It is said to be non-blocking in the strict sense if an internal path can be established without disturbing any existing ones. If a re-arrangement of the existing paths is necessary and sufficient to support a newly admitted circuit, the switch is called re-arrangeably non-blocking. All non-blocking switches may be considered *functionally equivalent* in terms of the circuits they can support.

A trivial example of a strictly non-blocking  $N \times N$  circuit switch, with each external link supporting a single circuit, is a crossbar that employs  $N^2$  electronic crosspoints to fully interconnect the N inputs to the N outputs. Much of the work in circuit switching [45, 88] addresses the construction of a multi-module bufferless fabric using an interconnection network of smaller components. This was motivated primarily by the fact that electronic crosspoints were expensive and their number in a crossbar increases quadratically with the size of the switch. Such networks may have internal contention due to commonality in the internal paths between inputoutput pairs, and hence can potentially be blocking. An internal *speedup*, defined as the ratio of the total link capacity between two internal stages to the total external capacity, is usually used to counter blocking. Examples of notable interconnection networks are the Banyan network and the Batcher sorting network, which require  $O(N \log N)$  and  $O(N \log^2 N)$  crosspoints, respectively. Both these networks are self-routing with a unique path between every input-output pair, however, the resulting structure is blocking. A popular example of a non-blocking network, which we shall revisit on several occasions, is the three-stage Clos network, which uses  $O(N^{1.5})$  crosspoints. A more complex example is the Cantor network, which uses  $O(N \log^2 N)$  crosspoints and remains non-blocking by employing several planes of a blocking sorting network. Indeed, the literature in the design of bufferless interconnection networks is fairly rich, yet rigorous due to the well-defined cost parameter and performance framework, namely, the number of crosspoints and blocking behavior, respectively.

### 2.1.2 Packets: QoS and Throughput

Packet-based networks do not rely on holding dedicated link resources and on switching between pre-established physical layer channels. Instead, the physical and link layers have the flexibility to employ either synchronous means such as SONET, or asynchronous ones such as Ethernet, on a link-by-link basis. Forwarding decisions at each switching node are made separately for each individual packet, based on the packet header information and the state maintained within the switch.

A traffic *flow*, in the most generic sense, refers to a stream of related packets. A flow may be fine-grained, corresponding to an end-to-end application session, or coarse-grained such as a permanent MPLS path providing connectivity between two IP subnets. In fact, each switch may view the aggregate traffic between each of its input-output pairs as a flow of the coarsest granularity. Flows are identified by a switch either using a label in the header, as in ATM and MPLS, or through a header-filter based on ranges of source and destination addresses, protocol types and/or transport-layer port numbers. Resources may be negotiated and configured for a subset of flows traversing a switch through a signaling phase prior to packet transmission or via long-term service level agreements (SLA). The traffic presented to a typical packet switch consists of a combination of such *guaranteed QoS* flows, for which the traffic profiles (e.g., a

token bucket specification [28]) and service requirements, including the desired average rate and tolerable maximum delay, are known in advance, and *best-effort* flows without any pre-specified profiles or requirements. Even the former are allowed to violate their negotiated profiles, in which case the excess component of their offered traffic is treated on a best-effort basis.

The foremost distinguishing feature of a packet switch is the inherent presence of external contention, i.e., several packets destined to the same output may compete for that link simultaneously. This phenomenon can be sustained over an arbitrary period of time, resulting in a backlog of unserved packets, which need to be buffered. An arriving packet may be dropped in response to congestion in the finite amount of available buffers, resulting in a packet loss ratio for the corresponding flow. The admitted backlog is then *scheduled* in a chosen fashion, which determines the packet delays, the observed flow service rates and the total throughput of the switch. Consequently, the performance measures of interest in packet switching include not only the admissibility of flows but also the abilities to meet the negotiated QoS requirements and to maximize throughput, both in the presence of external contention. Multi-rate loss models [95], similar to the ones in circuit switching, may be used to address the former for guaranteed QoS flows, while empirical ones (e.g., [5, 89]) are used to characterize the expected traffic for besteffort flows. These models, based only on the external link resources, may be meaningfully used to engineer the network, provided a packet switch possesses the above abilities, thereby removing specifics of the internal switch architecture from such engineering considerations.

In summary, the primary goals in designing a packet switching node include provisions to ensure that the observed packet throughput on the external links approaches the advertised link capacities, and provisions to provide preferential treatment, in the form of scheduling and buffer management, to specified flows so that their negotiated QoS requirements are met. When design constraints necessitate building a multi-module switch, the challenge is to meet these goals in the presence of both external and internal contention.

## 2.2 Notions of Optimal Performance

We now crystallize some of the concepts seen in the overview, and arrive at a few propositions that serve as guiding principles for switching analysis. A circuit request between an input-output link

pair of a circuit switch is considered *admissible* if there are available channels on the specified external links. Let V denote a set of simultaneously admissible circuits. A non-blocking switch ensures that a path within the switch is realizable for every  $v \in V$ . Since this holds for any given V, including *any* given definition of an optimal set, and since circuit switches drop inadmissible requests, we assert the following:

#### **Proposition 1.** The non-blocking property ensures optimal throughput of a circuit switch.

Packet switching calls for similar properties that ensure optimal QoS and throughput, limited solely by external link resources, for the most general models of offered traffic. Let the traffic arriving at input *i* and destined to output *j* of a packet switch be referred to as the inputoutput flow (i, j). Let the amount of arriving traffic, e.g., in bits, for each flow be maintained by the arrival matrix *A*, where  $A_{i,j}[t_1, t_2)$  refers to the arrivals in the interval  $[t_1, t_2)$  for flow (i, j). The short-form A(n) may be used for A[0, n). In general, this is governed by a stochastic arrival process. The long-term average rates of arrival yield the *offered rate* matrix  $\lambda$ , i.e.,

$$\lambda_{i,j} = \lim_{n \to \infty} \frac{A_{i,j}(n)}{n}.$$

(2.1)

The arrivals are considered admissible if the following conditions are satisfied:

$$\forall i \sum_{j} \lambda_{i,j} \leq C \quad \text{and} \quad \forall j \sum_{i} \lambda_{i,j} \leq C,$$

(2.2)

where C refers to the link capacity of the inputs and outputs. The above is typically used to restrict the modeled arrivals due to the following reasons. The first inequality is a physical constraint imposed by the input link. A violation of the second would imply that at least some of the output links cannot sustain the offered rates. As a special case, the arrivals are considered *bounded admissible* with timescale T, if the average rates  $\lambda$  hold for every interval of length T, and  $\lambda$  is admissible, i.e.,

$$\forall i, j, t \; \frac{A_{i,j}[t, t+T)}{T} \le \lambda_{i,j} \tag{2.3}$$

and (2.2) is satisfied. In other words, (2.3) imposes a timescale on the averaging of arrival rates. The arrivals are considered *partially admissible* if the second inequality in (2.2) holds for a proper subset of the outputs. Unlike circuit switching, neither admissibility nor a knowledge of  $\lambda$  may be presumed due to the presence of best-effort traffic.

The *required rate* matrix R contains the effective-rate requirements of the guaranteed QoS component. In general, this can be independent of  $\lambda$ . If rates are specified for finer-grain flows, these may be aggregated per input-output pair to yield R. As opposed to  $\lambda$ , the required rate matrix may be presumed to be known and admissible, i.e.,

$$\forall i \sum_{j} R_{i,j} \le C \quad \text{and} \quad \forall j \sum_{i} R_{i,j} \le C.$$

(2.4)

The above is ensured by the admission control procedure that negotiates QoS on the basis of the external link resources. Consequently, a switch that is able to allocate any given combination of admissible rates throughout the internal paths between respective input-output pairs may be considered optimal in QoS capability. We refer to the act of allocating rates as *flow fitting* or providing virtual bandwidth trunks through the switch. Notice that these trunks may be viewed as multi-rate circuits, e.g., a request for 5 Mb/s on a link of 20 Mb/s capacity may be viewed as a simultaneous request for 5 circuits on a link with a capacity to admit 20 circuits. Therefore, it is straight-forward to see that a multi-stage packet switch that has the same logical structure, i.e., an identical interconnection network with identical capacities on each internal link but augmented with contention buffers in certain stages, as a non-blocking circuit switch is guaranteed to find the requisite internal paths to fit any set of admissible flows.

#### **Proposition 2.** A packet switch with a non-blocking structure is optimal in QoS capability.

Due to the variability in the packet arrivals, mere path realization is not sufficient. Additional mechanisms, specifically, scheduling policies in each stage of the switch, are required to ensure QoS satisfaction. Nevertheless, in terms of switch architecture, a non-blocking design is a good first step. Since much of the early packet switching work was based on ATM switches, wherein the entire traffic undergoes admission control, the ability to fit flows was considered the primary objective, also leading to several claims of optimal throughput based solely on the non-blocking property.

Notice that if all  $\lambda_{i,j}$  are known beforehand, and  $\lambda$  is admissible, we may use it instead of R in order to create virtual bandwidth trunks within the switch. In this special case, the ability to provide optimal QoS is sufficient to realize maximum long-term throughput as well. However, the knowledge of offered rates is an invalid assumption in packet switching, necessitating additional measures for optimality in throughput. Since the amount of traffic that may be successfully dispatched on an output link is limited by the capacity of that link, maximum throughput is ensured as long as an output link of the switch never idles when a packet destined to it is backlogged anywhere within the switch. Switches with this property are referred to as system-wide *work conserving*. Therefore, a packet switch may be considered *ideal* if it is work conserving under any offered traffic, and is able to allocate any given combination of required rates at the same time.

If  $\lambda$  is admissible, every queue in an ideal switch remains stable. If  $\lambda$  is partially admissible, only those queues that contain traffic destined to oversubscribed outputs, i.e., outputs j for which  $\sum_i \lambda_{i,j} \geq C$ , become unstable. Within an oversubscribed output j, an ideal switch has the ability to serve each individual flow (i, j) with a specified proportion of the output capacity. This results in a subset of the queues that contain traffic to output j to remain stable, specifically, the queues corresponding to (i, j) for which  $\lambda_{i,j}$  is less than the respective proportion. Notice that any switch that can maintain the stability of the same set of queues as an ideal switch ends up providing the same asymptotic throughput to each corresponding flow, and hence the same throughput for the switch as a whole. We refer to such a switch as *functionally equivalent* to an ideal switch. In other words, we may use the stability of a given set of circuits in circuit switching. If it is difficult or impossible to prove that a switch design under consideration is ideal, one may then claim optimal throughput by establishing functional equivalence with an ideal switch, for the most general model of offered traffic.

**Proposition 3.** A packet switch that is functionally equivalent, in terms of queue stability, with a well-known ideal switch is optimal in throughput.

We can now relate the techniques used in the existing literature to the above notion of optimal throughput. One approach is to rely on directly establishing a switch to be work conserving (e.g., [65]), while another is to ensure that the packets depart from the outputs of a given switch in an *exact emulation* of the departure from a well-known ideal switch, for identical arrival patterns (e.g., [24]). One widely used approach that relies on establishing queue stability, and hence implicitly on functional equivalence with an ideal switch, is the notion of 100% throughput

Figure 2.1: Forwarding models: (a) Centralized CPU, (b) Cut-through

(e.g., [29, 70]). The technique is to prove the stability of all the queues for admissible offered rates. This is a reasonable approach except, maybe, for the presumption of admissibility.

To summarize, we may use the following steps to design a multi-module packet switch that remains optimal in QoS and throughput performance. We start with a non-blocking structure, possibly borrowed from circuit switching, augment it with internal buffers wherever necessary to account for contention, and provide for scheduling policies that can guarantee virtual bandwidth trunks to satisfy any admissible required-rate matrix. We then ensure that the devised scheduling policies, which govern the dispatch decisions from module to module and finally to the external links, are able to maintain stability in the same set of queues as an ideal switch for the same offered traffic, not necessarily admissible. The performance capability becomes weaker whenever restrictions are placed on the offered traffic.

## 2.3 Forwarding Models

With a framework in place for optimal packet switching performance, independent of the internal switch architecture, as desired, we are now ready to address the latter, namely, the topic of switch

design itself. We identify two basic forwarding models for a packet switch, the centralized CPUbased model and the cut-through fabric model.

The first generation of routers, and many of the current lower capacity ones, perform software-based forwarding using a centralized processor. A general purpose CPU is connected to multiple line cards through an I/O bus, as shown in Fig. 2.1(a). The lines shown are full-duplex, i.e., they contain both input and output interface components. In practice, the line cards may be located off of the same board as the CPU, with an on-board bus such as PCI providing connectivity to the CPU, or on separate boards on a chassis, with a star or bus connectivity between them. The cards perform the physical and link layer protocol processing and forward the incoming packets to the CPU. Access to the I/O bus may be controlled by the CPU, e.g., by polling the line cards, or arbitrated via a separate medium-access technique. The headers of the incoming packets are analyzed by the CPU to determine the outgoing interface and any special handling, if applicable, following which they are dispatched to the respect output in a chosen order.

In general, a packet may experience contention at several points within the system, namely, at the I/O bus waiting to gain access and get transferred to the CPU, at the CPU waiting to be processed, and finally, as is the case with any packet switch, at the output interface. Accordingly, queueing buffers are provided in the line cards next to the input and the output interfaces, and in the CPU memory. An evident disadvantage of this model is that the limited communication bandwidth of the I/O bus and the processing power of the CPU present significant bottlenecks to packet throughput, and thereby limit the port counts and the interface rates that can be supported. Providing QoS is practically ruled out if packets need to be queued *before* they can even be identified by the CPU.

Consider an example of a  $16 \times 16$  switch with 1 Gb/s ports. In order to make such a switch *wire-speed*, i.e., to ensure that any queueing happens only after a packet has been identified, and to remove the I/O bus and the CPU as internal contention points, the components need to be dimensioned as follows. Assuming a minimum packet size of 64 bytes, the CPU needs a processing capacity of 32 million pps (16 Gb/s of total offered traffic divided by 512 bits), which translates to an upper bound of about 32 cycles on a 1 GHz CPU to account for memory access and

Figure 2.2: Pipeline of a cut-through forwarding path

instructions. To sustain the full-duplex traffic, the I/O bandwidth required is 32 Gb/s, compared, e.g., to the 8 Gb/s available using a 64-bit 133 MHz PCI bus. The bandwidth required of the CPU memory is also 32 Gb/s, allowing merely 16 ns for a memory transfer assuming a wide 64-byte memory bus. Clearly, these are tall orders even for the modestly sized switch in the example. Consequently, the path traversed by the packet through a central CPU is often referred to as the *slow path*.

Modern designs use the *cut-through* model illustrated in Fig. 2.1(b). Special-purpose port processors, attached to each full-duplex line, operate on packets at the ingress and egress of the switch. In addition to physical and link-layer processing, packet header processing is also performed within these units using local state information. Such processing includes network address lookup for output determination, flow identification via filters, flow policing if applicable, statistics collection, and other protocol-specific tasks. The results of these operations that are relevant to packet dispatch are encoded and inserted into a special local header. The packets are then routed directly to the respective output interfaces through a dedicated switch fabric, also known as the *fast path*. If the fabric expects fixed-size data units, the port processor is also responsible for the associated segmentation and reassembly (SAR) of variable-sized packets. A central CPU is connected to the port processors either via a special port of the switch fabric, as

shown in the figure, or through a dedicated I/O bus. In this model, only the network and system control traffic is routed to the CPU, which implements the relevant routing and management protocols, maintains the overall state of the system and programs the local states into the port processors and switch fabric. In other words, the slow path continues to handle the control plane, while the dedicated fast path handles the data plane. Fig. 2.2 shows an example pipeline of a cut-through forwarding path.

In practice, there are several variations of this logical model. Each port processor unit may be implemented on a separate board, attached to a chassis, with a star topology on the backplane interconnecting them to a switch fabric board. Alternatively, the interconnection may be on the backplane itself as a full-mesh between port processor cards, which may also house the queues of the switch. In any case, all internal contention in this model is concentrated within the fabric, provided the port processors operate at wire speed. For the same  $16 \times 16$  switch example as above, this requires a processing capability of 2 million pps in each unit. Communication IC vendors already offer so-called network processors that implement the necessary components in silicon at interface rates of 10 Gb/s and processing capacities of 20-30 million pps. More importantly, as opposed to the previous model, these capacities do not need to increase linearly with the port count. The switch fabric needs to sustain a forwarding capacity of 16 Gb/s, with a memory bandwidth that depends on the architecture, though it clearly does not exceed 32 Gb/s. Vendors today use several different types of designs to offer fabrics that operate at a nominal capacity of several hundred Gb/s.

While there are quite a few interesting problems in scaling the port processors, such as the best sorting structures to use for address lookup, for example, we concentrate on the design of the fabric itself.

# 2.4 Building Blocks

We introduce two types of basic forwarding elements to construct a fabric, namely *memory elements* and *space elements*. These are logical entities that address the two primary functionalities of a packet switch, namely, queueing to absorb contention, and providing interconnection. From the perspective of multi-module switch design, we consider these entities to be the atomic build-

Figure 2.3: Forwarding elements: (a) memory element, (b) space element

ing blocks.