### **GPU-Acceleration of In-Memory Data Analytics**

Evangelia Sitaridi

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

### COLUMBIA UNIVERSITY

2016

©2016 Evangelia Sitaridi All Rights Reserved

### ABSTRACT

# GPU-Acceleration of In-Memory Data Analytics Evangelia Sitaridi

Hardware advances strongly influence the database system design. The flattening speed of CPU cores makes many-core accelerators, such as GPUs, a vital alternative to explore for processing the ever-increasing amounts of data. GPUs have a significantly higher degree of parallelism than multi-core CPUs but their cores are simpler. As a result, they do not face the power constraints limiting the parallelism of CPUs. Their trade-off, however, is the increased implementation complexity. This thesis adapts and redesigns data analytics operators to better exploit the GPU special memory and threading model. Due to the increasing memory capacity and also the user's need for fast interaction with the data, we focus on in-memory analytics.

Our techniques span different steps of the data processing pipeline: (1) Data preprocessing, (2) Query compilation, and (3) Algorithmic optimization of the operators. Our data preprocessing techniques adapt the data layout for numeric and string columns to maximize the achieved GPU memory bandwidth. Our query compilation techniques compute the optimal execution plan for conjunctive filters. We formulate *memory divergence* for string matching algorithms and suggest how to eliminate it. Finally, we parallelize decompression algorithms in our compression framework *Gompresso* to fit more data into the limited GPU memory. Gompresso achieves high speed-ups on GPUs over multi-core CPU state-of-the-art libraries and is suitable for any massively parallel processor.

## **Table of Contents**

| Li       | List of Figures v |         |                                             |    |  |

|----------|-------------------|---------|---------------------------------------------|----|--|

| Li       | st of             | Tables  | 5                                           | ix |  |

| 1        | Intr              | oducti  | on                                          | 1  |  |

|          | 1.1               | Motiva  | ation                                       | 3  |  |

|          | 1.2               | GPU A   | Architecture                                | 4  |  |

|          |                   | 1.2.1   | GPU Historical Overview                     | 4  |  |

|          |                   | 1.2.2   | GPU Architectural challenges                | 6  |  |

|          | 1.3               | Proble  | em Setting and Context                      | 10 |  |

|          | 1.4               | Thesis  | Contribution                                | 14 |  |

|          |                   | 1.4.1   | Shared Memory Joins & Aggregations          | 15 |  |

|          |                   | 1.4.2   | Multi-Predicate Selection Execution         | 16 |  |

|          |                   | 1.4.3   | String Matching Optimization                | 17 |  |

|          |                   | 1.4.4   | SIMD-Accelerated Regular Expressions        | 18 |  |

|          |                   | 1.4.5   | Compression Acceleration                    | 19 |  |

|          | 1.5               | Thesis  | Outline                                     | 21 |  |

| <b>2</b> | Rela              | ated W  | Vork                                        | 22 |  |

|          | 2.1               | Relatio | onal Operator Accelerator                   | 22 |  |

|          | 2.2               | State-o | of-the-art GPU-Accelerated Database Systems | 23 |  |

| 3        | Sha               | red M   | emory Joins & Aggregations                  | 27 |  |

|          | 3.1               | Introd  | uction                                      | 27 |  |

|   | 3.2   | Related Work                | 8             |

|---|-------|-----------------------------|---------------|

|   | 3.3   | Problem Description         | 9             |

|   | 3.4   | Data Placement Algorithms   | 2             |

|   |       | 3.4.1 Write Conflicts       | 2             |

|   |       | 3.4.2 Read Conflicts        | 4             |

|   | 3.5   | Experimental Evaluation     | 5             |

|   |       | 3.5.1 Experimental Setup    | 5             |

|   |       | 3.5.2 Memory Footprint      | 6             |

|   |       | 3.5.3 Query Performance     | 8             |

|   |       | 3.5.4 Optimization Speed    | 2             |

|   | 3.6   | Summary & Conclusions       | 2             |

| 4 | N/I-1 | ti-Predicate Selections 4   | 2             |

| 4 | 4.1   |                             | <b>э</b><br>З |

|   |       |                             | 3<br>4        |

|   | 4.2   |                             |               |

|   | 4.3   | 0                           | 6             |

|   | 4.4   |                             | 6             |

|   |       | 0                           | 6             |

|   |       | -                           | 8             |

|   | 4.5   | Query Cost-Model            |               |

|   |       | 4.5.1 Single-Kernel Plans 5 |               |

|   |       | 4.5.2 Multiple-Kernel Plans | 1             |

|   |       | 4.5.3 Model Calibration     | 2             |

|   | 4.6   | Optimization Algorithm      | 2             |

|   | 4.7   | Experimental Evaluation     | 4             |

|   |       | 4.7.1 Experimental Setup 5  | 4             |

|   |       | 4.7.2 Cost Model Validation | 5             |

|   |       | 4.7.3 Query Plan Space      | 7             |

|   |       | 4.7.4 Optimization Speed    | 8             |

|   | 4.8   | Summary & Conclusions       | 8             |

| Sub | -string                                                                                                                         | g Matching Acceleration                                                                                                               | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 | Introd                                                                                                                          | luction                                                                                                                               | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.1.1                                                                                                                           | String Matching Acceleration                                                                                                          | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.1.2                                                                                                                           | String Matching on GPUs                                                                                                               | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.1.3                                                                                                                           | String matching on GPU Databases                                                                                                      | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.1.4                                                                                                                           | Thread-Divergence on GPUs                                                                                                             | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.2 | Cache                                                                                                                           | Pressure                                                                                                                              | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.3 | String                                                                                                                          | matching Framework                                                                                                                    | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.3.1                                                                                                                           | Addressing Thread Divergence                                                                                                          | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.3.2                                                                                                                           | Addressing Cache Pressure                                                                                                             | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.3.3                                                                                                                           | Addressing Memory Divergence                                                                                                          | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.3.4                                                                                                                           | Combining Different Optimizations                                                                                                     | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.3.5                                                                                                                           | Algorithm Analysis                                                                                                                    | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.4 | Exper                                                                                                                           | imental Evaluation                                                                                                                    | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.4.1                                                                                                                           | Experimental Setup                                                                                                                    | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.4.2                                                                                                                           | Comparing Algorithm Efficiency                                                                                                        | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.4.3                                                                                                                           | Effect of Thread Divergence                                                                                                           | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.4.4                                                                                                                           | Effect of Alphabet Size                                                                                                               | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 5.4.5                                                                                                                           | Segmentation                                                                                                                          | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

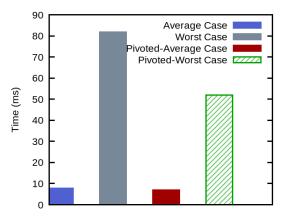

|     | 5.4.6                                                                                                                           | Worse-Case Performance                                                                                                                | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

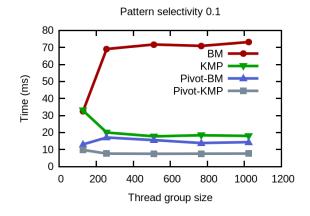

|     | 5.4.7                                                                                                                           | Thread Group Size Tuning                                                                                                              | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

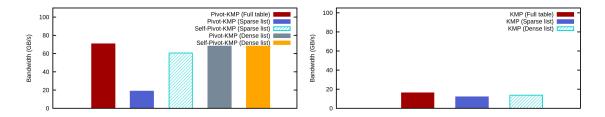

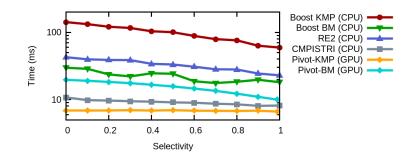

|     | 5.4.8                                                                                                                           | Comparison with CPUs                                                                                                                  | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.5 | Conclu                                                                                                                          | usions and Future Work                                                                                                                | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SIM | ID-Ace                                                                                                                          | celerated Regular Expressions                                                                                                         | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.1 | Introd                                                                                                                          | luction                                                                                                                               | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

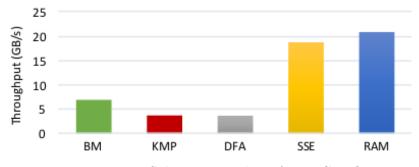

|     | 6.1.1                                                                                                                           | Substring Matching                                                                                                                    | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

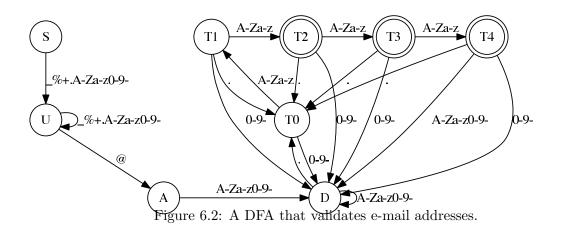

|     | 6.1.2                                                                                                                           | Regular Expression Matching                                                                                                           | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.2 | Relate                                                                                                                          |                                                                                                                                       | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.3 |                                                                                                                                 |                                                                                                                                       | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.4 | _                                                                                                                               |                                                                                                                                       | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>SIN</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul> | 5.1 Introd<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 Cache<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3 | 5.1.1       String Matching Acceleration         5.1.2       String Matching on GPUs         5.1.3       String matching on GPU Databases         5.1.4       Thread-Divergence on GPUs         5.2       Cache Pressure         5.3       String matching Framework         5.3.1       Addressing Thread Divergence         5.3.2       Addressing Cache Pressure         5.3.3       Addressing Cache Pressure         5.3.4       Combining Different Optimizations         5.3.5       Algorithm Analysis         5.4       Experimental Evaluation         5.4.1       Experimental Setup         5.4.2       Comparing Algorithm Efficiency         5.4.3       Effect of Thread Divergence         5.4.4       Effect of Thread Divergence         5.4.5       Segmentation         5.4.6       Worse-Case Performance         5.4.7       Thread Group Size Tuning         5.4.8       Comparison with CPUs         5.5       Conclusions and Future Work         6.1       Introduction         6.1.1       Substring Matching         6.1.2       Regular Expression Matching         6.1.2       Regular Expression Matching         6.1.2       Replated Work< |

|                           | 6.5    | Conclu  | usions $\ldots$ | 113 |

|---------------------------|--------|---------|--------------------------------------------------------------------------------------------------|-----|

| 7                         | Dec    | compre  | ession Acceleration                                                                              | 115 |

|                           | 7.1    | Introd  | luction                                                                                          | 115 |

|                           | 7.2    | Relate  | ed Work                                                                                          | 117 |

|                           | 7.3    | Gomj    | presso Overview                                                                                  | 119 |

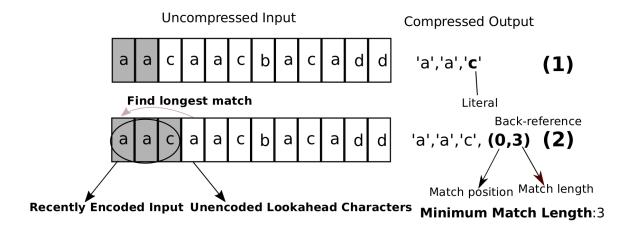

|                           |        | 7.3.1   | Parallel Compression                                                                             | 120 |

|                           |        | 7.3.2   | Parallel Decompression                                                                           | 121 |

|                           | 7.4    | Data 1  | Dependencies in Nested Back-references                                                           | 124 |

|                           |        | 7.4.1   | MRR Strategy                                                                                     | 125 |

|                           |        | 7.4.2   | DE Strategy                                                                                      | 127 |

|                           | 7.5    | Exper   | imental Evaluation                                                                               | 130 |

|                           |        | 7.5.1   | Experimental Setup                                                                               | 130 |

|                           |        | 7.5.2   | Data Dependency Resolution                                                                       | 131 |

|                           |        | 7.5.3   | Performance Impact of Nested back-references                                                     | 131 |

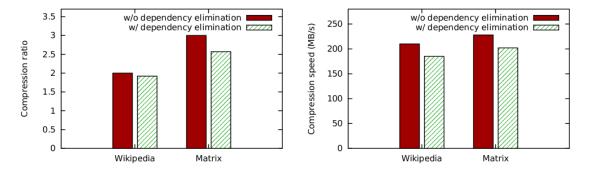

|                           |        | 7.5.4   | Impact of DE on Compression Ratio and Speed                                                      | 134 |

|                           |        | 7.5.5   | Compression Framework Tuning                                                                     | 134 |

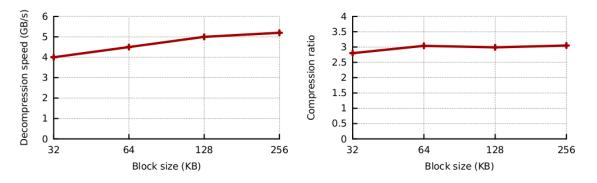

|                           |        | 7.5.6   | Dependency on Data Block Size                                                                    | 134 |

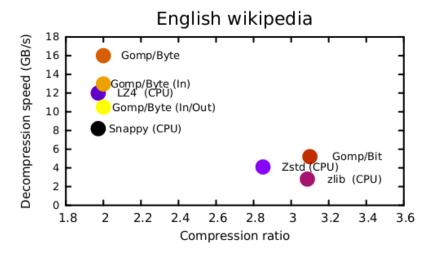

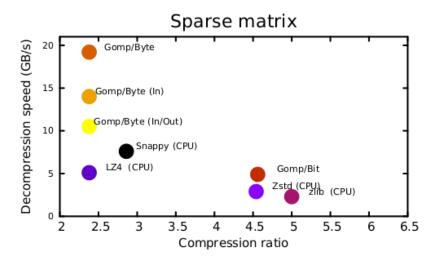

|                           |        | 7.5.7   | GPU vs. Multi-core CPU Performance                                                               | 135 |

|                           | 7.6    | Summ    | nary & Conclusions                                                                               | 138 |

| 8                         | Cor    | ncludin | ng Remarks and Future Work                                                                       | 140 |

|                           | 8.1    | GPU     | Query Execution Optimization                                                                     | 140 |

|                           | 8.2    | String  | Matching Acceleration                                                                            | 141 |

|                           | 8.3    | Massiv  | vely Parallel Lossless Compression                                                               | 142 |

|                           | 8.4    | Hetero  | ogeneous Computing Data Analytics                                                                | 142 |

| Bi                        | ibliog | graphy  |                                                                                                  | 144 |

| $\mathbf{A}_{\mathbf{j}}$ | ppen   | dix     |                                                                                                  | 161 |

# List of Figures

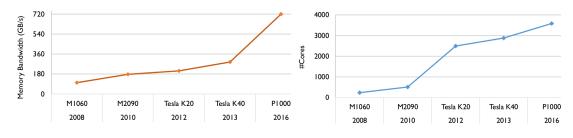

| 1.1  | GPU Trends in memory bandwidth and number of cores                               | 6  |

|------|----------------------------------------------------------------------------------|----|

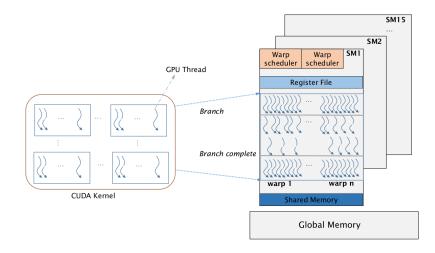

| 1.2  | NVIDIA GPU Architecture overview.                                                | 6  |

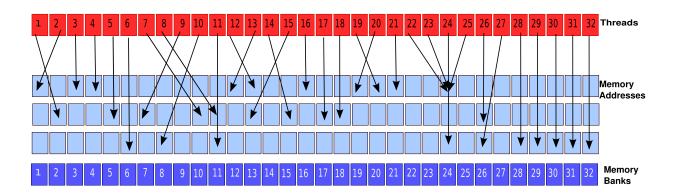

| 1.3  | An example of bank/value access pattern for 32 threads in a warp                 | 7  |

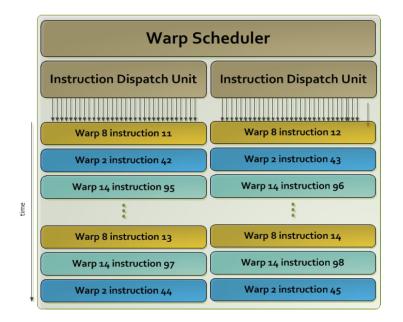

| 1.4  | Thread scheduling in NVIDIA GPUs                                                 | 8  |

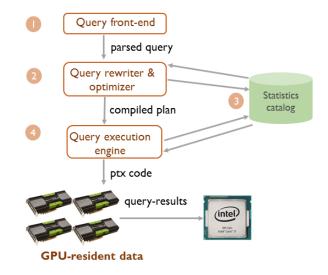

| 1.5  | GPU Database system architecture.                                                | 10 |

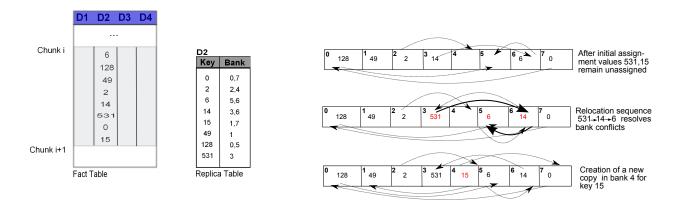

| 3.1  | Bank optimization for 8-element chunks.                                          | 34 |

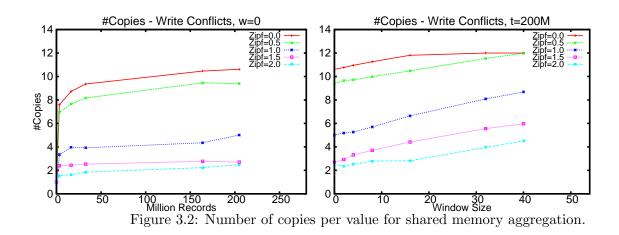

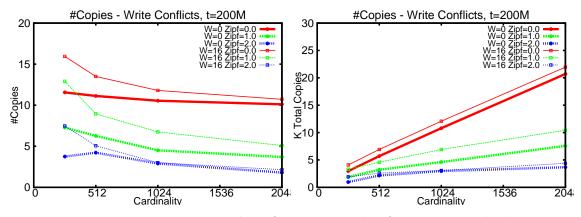

| 3.2  | Number of copies per value for shared memory aggregation                         | 35 |

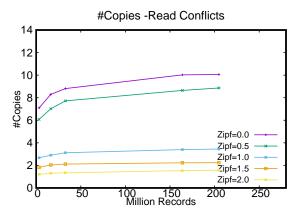

| 3.3  | Number of copies per value for shared-memory joins                               | 36 |

| 3.4  | Number of copies per value for varying cardinality                               | 37 |

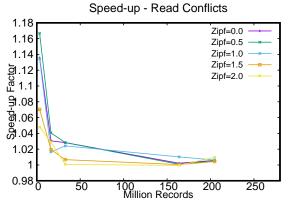

| 3.5  | Throughput for different budgets                                                 | 37 |

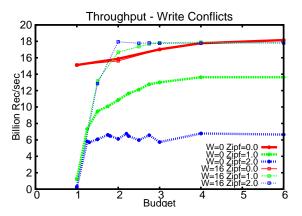

| 3.6  | Speed-up for Write Conflicts.                                                    | 38 |

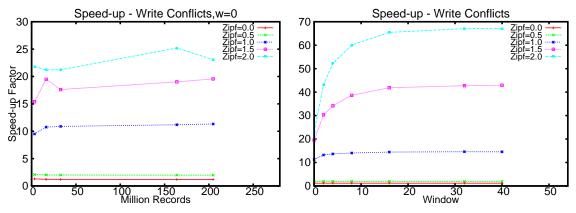

| 3.7  | Speed-up for Read Conflicts.                                                     | 38 |

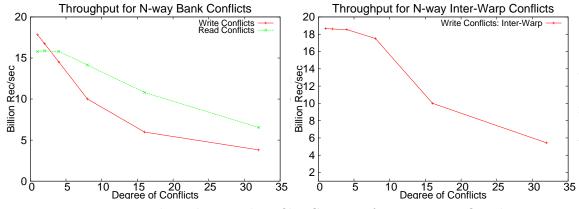

| 3.8  | Throughput and profiler Counters for varying conflict degree, t=30<br>M. $\ .$ . | 39 |

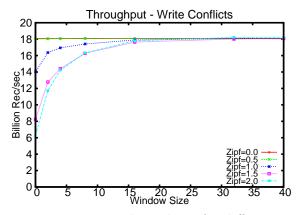

| 3.9  | Throughput for different windows.                                                | 40 |

| 3.10 | Optimizing for value conflicts only                                              | 41 |

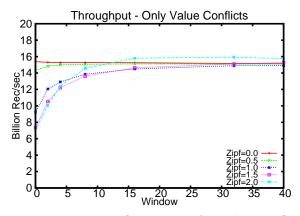

| 3.11 | Optimization time                                                                | 41 |

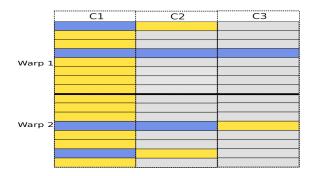

| 4.1  | Execution of the S111 plan for two warps.                                        | 47 |

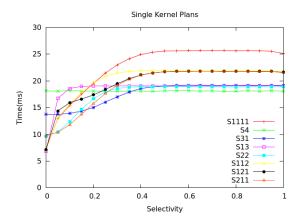

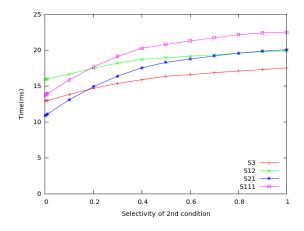

| 4.2  | Time performance in ms of different plans for a query with four conditions.      | 48 |

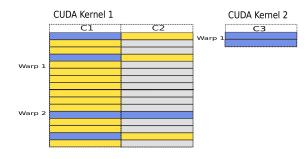

| 4.3  | Execution of the K21 plan for two warps.                                         | 49 |

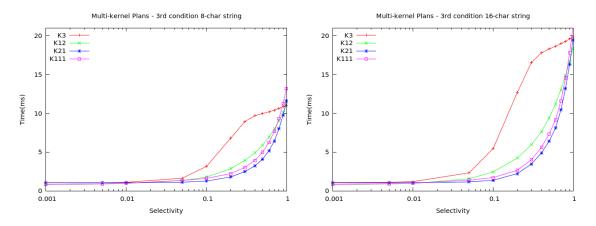

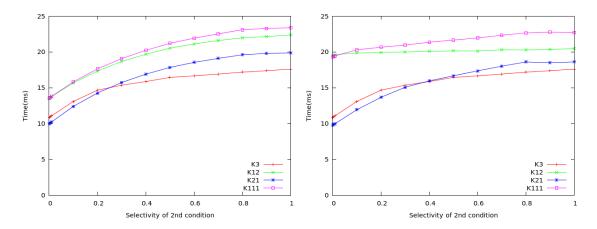

| 4.4  | Performance of multi-kernel plans when varying the selectivity of the first      |    |

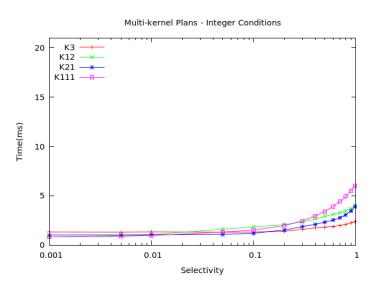

|      | condition.                                                                       | 49 |

| 4.5  | Performance of multi-kernel plans when varying the selectivity of the first       |    |

|------|-----------------------------------------------------------------------------------|----|

|      | condition                                                                         | 50 |

| 4.6  | Single-Kernel Optimization Algorithm                                              |    |

| 4.7  | Actual and estimated performance for different single-kernel plans of Q2. $$ .    | 55 |

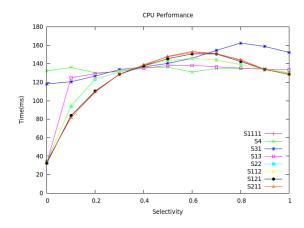

| 4.8  | Time performance of different plans on the CPU for Q2                             | 56 |

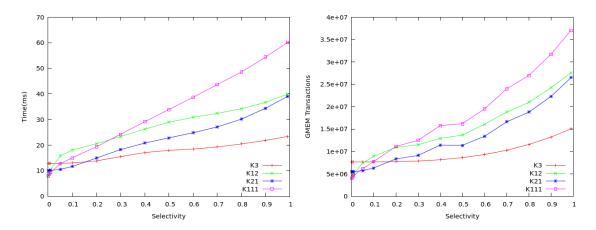

| 4.9  | Actual and estimated performance of multi-kernel plans for Q1 varying the         |    |

|      | selectivity of all conditions.                                                    | 56 |

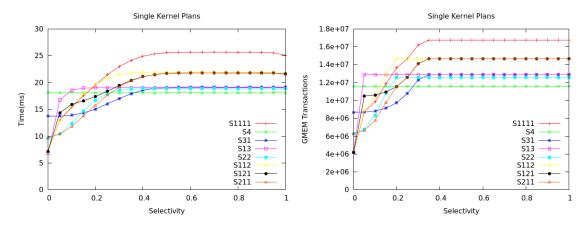

| 4.10 | Time performance of single-kernel plans for Q1 for varying predicate selectivity. | 57 |

| 4.11 | Time performance of multi-kernel plans for Q1 or varying predicate selectivity.   | 57 |

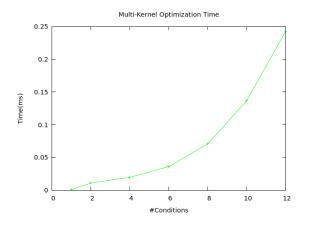

| 4.12 | Execution time of the multi-kernel optimizer as a function of the number of       |    |

|      | conditions.                                                                       | 58 |

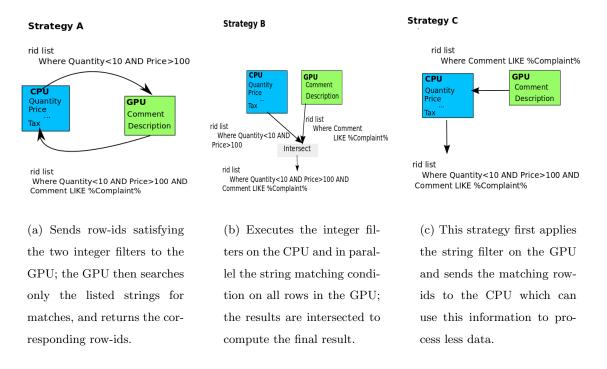

| 5.1  | Strategies for CPU-GPU interaction.                                               | 66 |

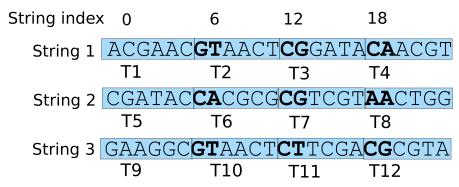

| 5.2  | Execution of the baseline method and Split-2 method for search pattern 'CAA'. 67  |    |

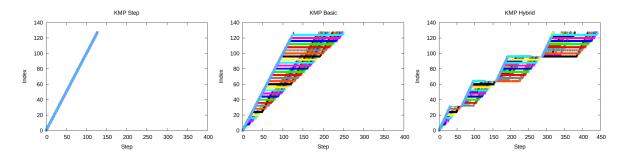

| 5.3  | Execution of Seg 6-4 parallelism method for a pattern of three characters. 68     |    |

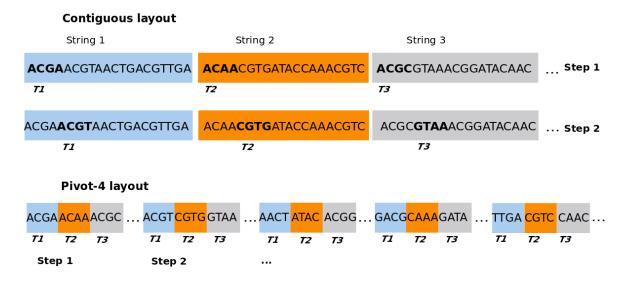

| 5.4  | Contiguous and pivoted layout for 20-character strings and pivoted-piece of       |    |

|      | 4-characters.                                                                     | 69 |

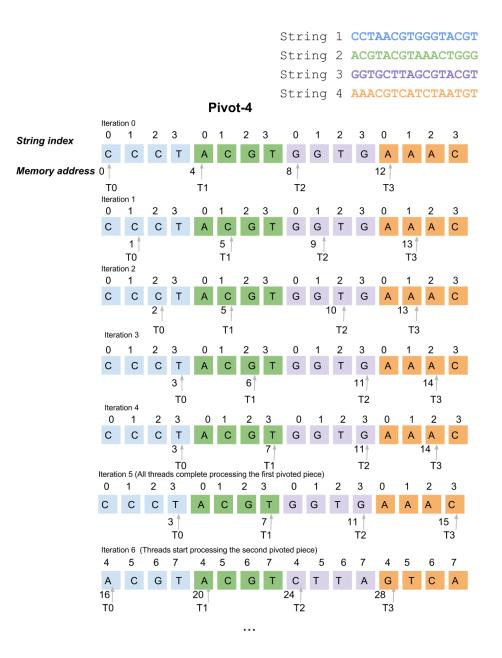

| 5.5  | Execution of Pivot-4 method for 'ATG' pattern using the KMP-Hybrid string $$      |    |

|      | matching method and 4 GPU threads                                                 | 75 |

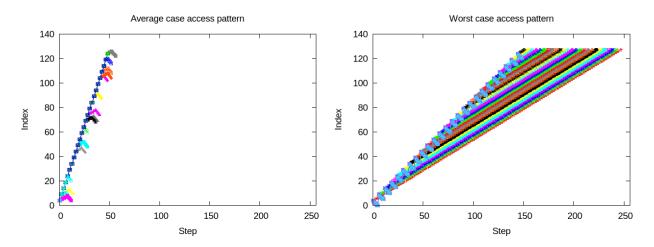

| 5.6  | Memory access pattern for BM on an average case dataset and an adversar-          |    |

|      | ially generated input maximizing memory divergence.                               | 76 |

| 5.7  | Memory access pattern for a worst case input of KMP                               | 76 |

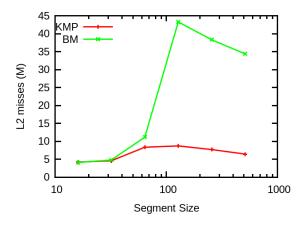

| 5.8  | KMP and BM Seg- $k$ - $t$ L2 misses for varying segment size on a dataset of      |    |

|      | 512K strings with $t=4$                                                           | 79 |

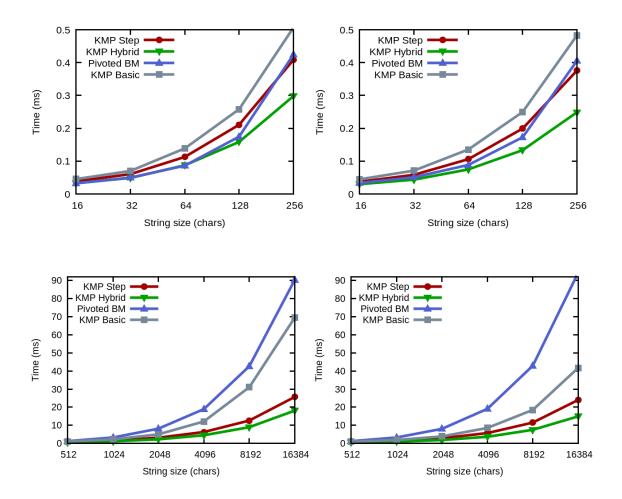

| 5.9  | Performance as a function of string length for Pivot-4 (left) and Pivot-8         |    |

|      | (right) layouts. The top row shows the results for shorter strings and the        |    |

|      | bottom row for longer strings                                                     | 82 |

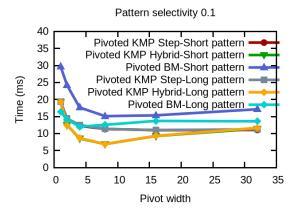

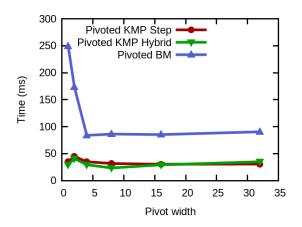

| 5.10 | Time performance on A1 for varying pivoted width.                                 | 83 |

| 5.11 | Time performance on R1 for varying pivoted width                                  |    |

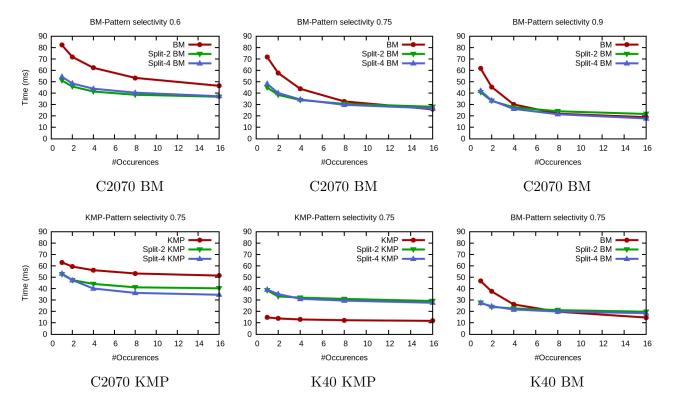

| 5.12 | Performance of Split-k Optimization on BM for varying number of string           |     |

|------|----------------------------------------------------------------------------------|-----|

|      | occurrences in the input. The first subfigure is for selectivity 0.6, the second |     |

|      | for 0.75, and the last for selectivity 0.9.                                      | 85  |

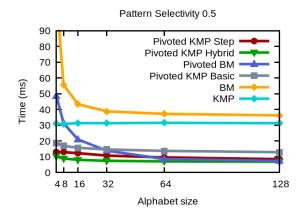

| 5.13 | Time performance of pivoted and unpivoted methods for varying alphabet           |     |

|      | size and an 8-character pattern.                                                 | 87  |

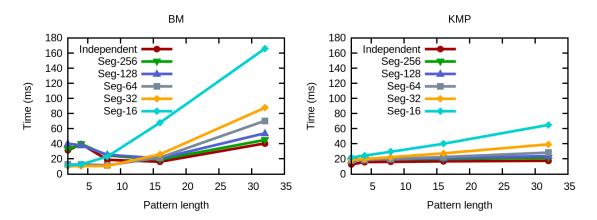

| 5.14 | Performance for increasing pattern length for Independent and Seg- $k-t$ (8)     |     |

|      | implementations                                                                  | 87  |

| 5.15 | Performance of BM for average and adversarial input.                             | 88  |

| 5.16 | Performance of KMP and BM for varying group size                                 | 89  |

| 5.17 | Bandwidth of string matching for sparse and dense record lists for pivoted       |     |

|      | (left) and unpivoted (right) KMP methods.                                        | 89  |

| 5.18 | Time performance of CPU and GPU string matching for A1 and a 8-character         |     |

|      | pattern                                                                          | 93  |

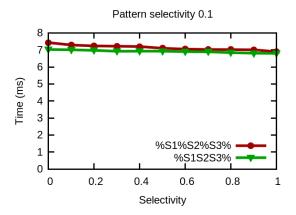

| 5.19 | Time performance of KMP for two different predicates: '%S1%S2%S3%' vs.           |     |

|      | '%S1S2S3%'                                                                       | 93  |

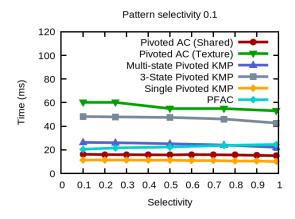

| 5.20 | Performance of pivoted AC, pivoted KMP against PFAC for varying selectivity.     | 94  |

| C 1  | Cabataina matakina far TDC II O12                                                | 00  |

| 6.1  | Substring matching for TPC-H Q13.                                                | 99  |

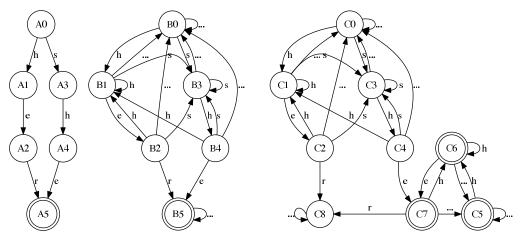

| 6.2  | A DFA that validates e-mail addresses.                                           | 100 |

| 6.3  | DFAs for combinations of: she, her                                               | 101 |

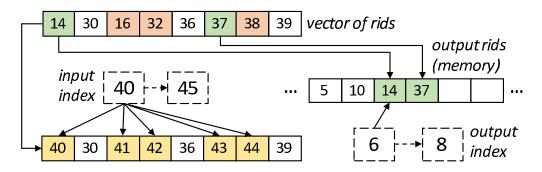

| 6.4  | Selective loads & stores of rids                                                 | 106 |

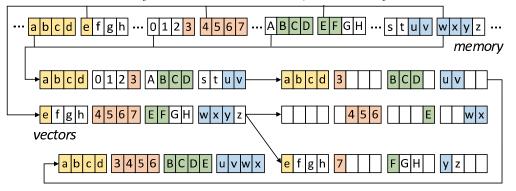

| 6.5  | Unaligned vector gathers in Xeon Phi                                             | 107 |

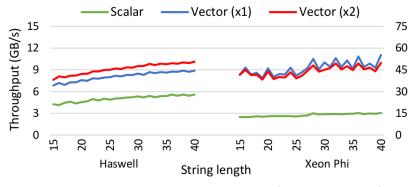

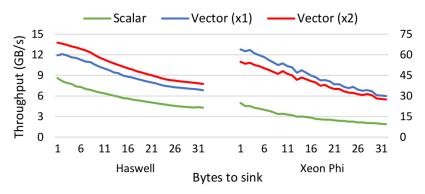

| 6.6  | Varying string lengths (URL validation)                                          | 110 |

| 6.7  | Varying the failure point (URL validation)                                       | 111 |

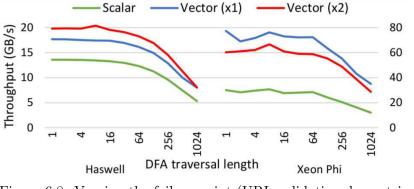

| 6.8  | Varying the failure point (URL validation, long strings)                         | 111 |

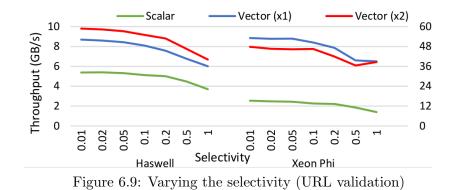

| 6.9  | Varying the selectivity (URL validation)                                         | 112 |

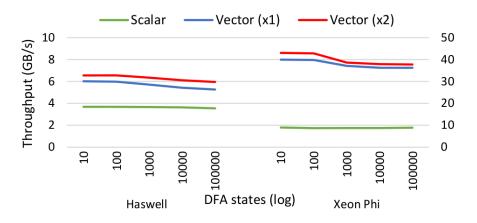

| 6.10 | Varying the DFA size (DFA for multi-pattern matching using English dictio-       |     |

|      | nary words)                                                                      | 113 |

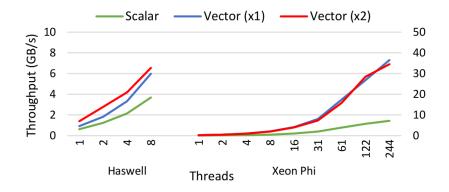

| 6.11 | Scalability (multi-pattern matching both positive and negative using English     |     |

|      | dictionary words)                                                                | 114 |

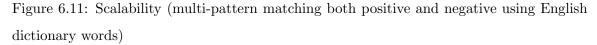

| 7.1  | Illustration of LZ77 compressio                                                                                   | 117 |

|------|-------------------------------------------------------------------------------------------------------------------|-----|

| 7.2  | Gompresso compression and decompression overview                                                                  | 120 |

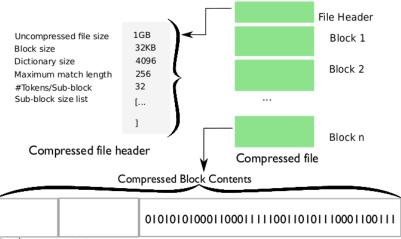

| 7.3  | The <b>Gompresso</b> file format.                                                                                 | 121 |

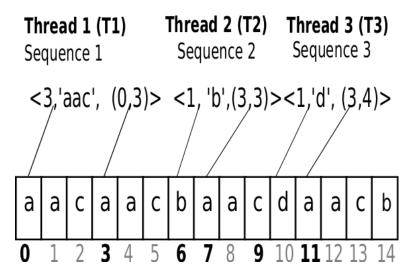

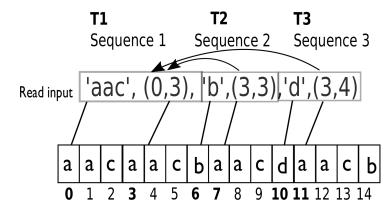

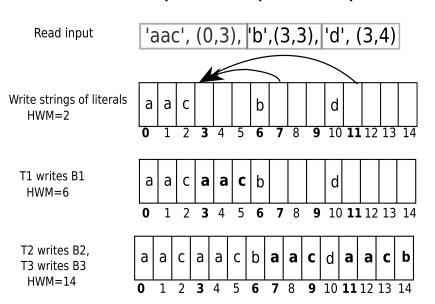

| 7.4  | Decompression of 3 sequences by 3 threads. Numbers at the bottom show the                                         |     |

|      | positions in the uncompressed output, and those in <b>bold</b> indicate the start                                 |     |

|      | write positions of each token. For simplicity, we indicate each match position                                    |     |

|      | as a global offset, though ${\bf Gompresso}$ uses thread-relative distances                                       | 123 |

| 7.5  | Nested back-references: back-references in Sequence 2 and 3 depend on Se-                                         |     |

|      | quence 1, and cannot be resolved before the output of Sequence 1 is available.                                    | 124 |

| 7.6  | Multi-Round Resolution (MRR) Algorithm                                                                            | 125 |

| 7.7  | Multi-Round Resolution (MRR) execution.                                                                           | 126 |

| 7.8  | Modified LZ77 compression algorithm with Dependency Elimination (DE).                                             | 128 |

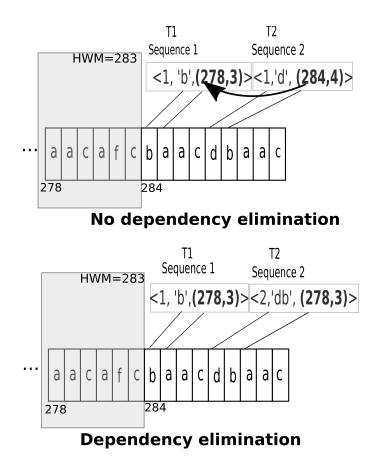

| 7.9  | Resulting token stream without and with dependency elimination (DE)                                               | 129 |

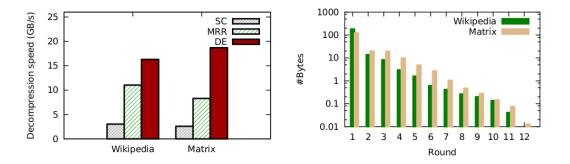

| 7.10 | (a) Decompression speed of $\mathbf{Gompresso}/\mathbf{Byte}$ (data transfer cost not in-                         |     |

|      | cluded), using different dependency resolution strategies for the two datasets.                                   |     |

|      | (b) Number of bytes processed on each round of MRR                                                                | 131 |

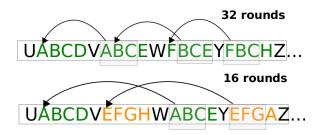

| 7.11 | Series of sequences inducing 32 and 16 rounds of resolution. $\ldots$ $\ldots$ $\ldots$                           | 132 |

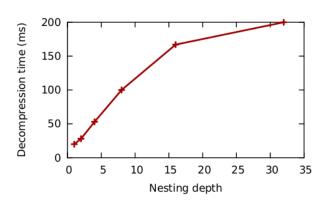

| 7.12 | Decompression speed of MRR as a function of the number of resolution                                              |     |

|      | rounds, for an artificially generated dataset                                                                     | 132 |

| 7.13 | Degradation in compression efficiency and speed for DE method. $\ldots$ .                                         | 134 |

| 7.14 | $Decompression \ speed \ (data \ transfer \ cost \ included) \ and \ ratio \ of \ \mathbf{Gompresso}/\mathbf{Bi}$ | t   |

|      | for different block sizes.                                                                                        | 135 |

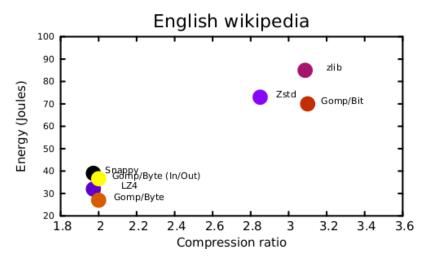

| 7.15 | GPU vs multicore CPU performance for the Wikipedia dataset                                                        | 136 |

| 7.16 | GPU vs multicore CPU performance for the sparse matrix dataset                                                    | 136 |

| 7.17 | GPU vs. multicore CPU energy consumption                                                                          | 137 |

## List of Tables

| 1.1  | CPU-GPU analogies.                                                            | 9  |

|------|-------------------------------------------------------------------------------|----|

| 3.1  | Average number of distinct banks, read serialization rounds and write seri-   |    |

|      | alization rounds in a chunk.                                                  | 31 |

| 5.1  | Advantages and drawbacks of each string matching optimization                 | 70 |

| 5.2  | Set of techniques used in our string matching methods                         | 71 |

| 5.3  | L2 cache footprint of different matching methods                              | 78 |

| 5.4  | GPUs used in our experiments.                                                 | 80 |

| 5.5  | Workload parameters.                                                          | 81 |

| 5.6  | Time performance of the three alternative CPU-GPU interaction strategies.     | 90 |

| 5.7  | CPU versus GPU comparison for Q16_1 and string size 1024 bytes                | 92 |

| 5.8  | CPU versus GPU comparison for Q16_1 and original string size (63 bytes).      | 92 |

| 5.9  | Performance (GB/s) of our matching methods versus the published perfor-       |    |

|      | mance of other GPU libraries (bottom three lines)                             | 95 |

| 5.10 | Best average case performance for workload A1 for different query parameters. | 95 |

## Acknowledgments

I would like to express my gratitude to my advisor Ken Ross for his guidance during my years at Columbia University. Ken always gave great insights during our research discussions because of his broad and deep knowledge of Database Systems and his sharp intellect. He inspired my interest in Hardware Accelerated Databases and I consider myself fortunate to have an advisor that always had time for discussion. I am also thankful for his understanding during the rewarding but also the harder times of my academic journey.

My sincere thanks go to Dr. Tim Kaldewey who was a very encouraging and hands-on mentor and collaborator sharing his valuable advice on all research, technical and personal levels. During my internships at the IBM Almaden Research Center, I had the chance to work with him, Dr. Rene Mueller and Dr. Guy Lohman. I consider myself lucky to collaborate on a project with them, an experience that I found genuinely exciting and I feel I gained valuable insights on real-world problems and on communicating my work more effectively. During my time in IBM Almaden, I also had the chance to interact with Dr. Ippokratis Pandis, who shared valuable advice on presenting my work in conferences.

I would like to thank Professor Luis Gravano for his resourceful comments and thoughtprovoking questions during the Database Group meetings and additionally for serving on my committee.

I am also grateful to Professors Mihalis Yannakakis and Eugene Wu for serving on my thesis committee. I appreciate the time they took out of their busy schedules to read through my thesis and share their knowledge and insights.

Many thanks deserve all the members of the Database Research Group of Columbia with whom I had the opportunity to overlap. I thank Bingyi, Fotis, Ioannis, Orestis, Pablo, Tom, and Wangda, for attending and giving valuable comments during my conference dry-run presentations. I especially thank Orestis Polychroniou, who was an excellent and inspiring collaborator.

Professors Yannis Ioannidis and Alex Delis introduced me to the Database and the System research field during my B.Sc. and M.Sc. years. Their lectures sparked my interest in these two fields and I am grateful for their advice during my Ph.D. applications and studies.

The members of Computing Research Facilities of Columbia were extremely helpful when hardware failures came up. I am thankful to Daisy, Hitae, Jorge and Sean for their support.

I am grateful to the National Science Foundation (grants IIS-0915956 and IIS-1218222) for the continuous financial support during my studies. I would like to thank IBM for the Fellowship it awarded me during the fourth year of my Ph.D. I am also grateful for the hardware donations from NVIDIA, that provided the GPU hardware I used for my Experimental Evaluations. Finally, I would like to thank Onassis Foundation for the scholarship it awarded me for my Ph.D. research.

On a personal note, I would like to express my gratitude to my family and friends in Greece and USA for their continuous encouragement. The friends I met during my graduate years at Columbia: Anthie, Bingyi, Christian, Emilio, Georgia, John, Marios, Melanie, Moschoula, Orestis, and Theofilos were a great support system and I thank them for the fun moments we shared. My long-time friends Maria, Marialena, Marina, and Nisa kept me going during the hardest times and celebrated with me my aha! moments. My family members Eleni, Kostis, and Voula made my life more meaningful. I am, especially, forever indebted to my parents Despoina and Tasos for their generosity of spirit. They taught me while growing up the value of creative work and compassion. My thesis would not have been completed or even start without their unconditional love and support. One of my life purposes is repaying their love and dedication and living up to their moral standards.

To my parents, Despoina and Tasos

### Chapter 1

## Introduction

In the last two decades database systems faced new bottlenecks. The increase in memory sizes allowed small and moderately sized databases to fit in the RAM [Manegold *et al.*, 2000]. As a result, the main performance bottleneck shifted from disk access to memory access.

The increase of memory capacity creates new opportunities for businesses to take advantage of in-memory data analytics. In-memory data analytics speed up the performance of a wide range of applications, from data warehousing to real-time analytics.

In data warehousing, data is reviewed, aggregated and then processed. *Real-time an-alytics* involves up-to-the-minute fresh data [Cohen-Crompton, 2012]. Social media is a significant source for real-time analytics. Interactive data visualization is a powerful tool for a lot of industries [Tableau, 2016]. Twitter data can be used by journalists to generate visualizations related to important events, such as the elections. Visualizations of the most tweeted candidate capture election trends and enrich the content of an article. In-memory analytics for businesses provide more detailed reports by boosting database performance. Faster processing means that managers can understand customer behavior and eventually make high-value, fast and informed decisions. Regardless of the time sensitivity of the data, in-memory processing requires optimized implementations of key functions. In this thesis, we explore two key functions: Filtering and string matching predicates to explore interesting areas of the data.

Another shift in hardware performance was the flattening speed of single-core processors

that paved the way for the multi-core era. Parallelism is our main hope to meet the need for increasing performance on database workloads [Sutter, 2005]. To reach the maximum memory bandwidth of processors for in-memory workloads, fully parallel programs must be designed. There are different types of available parallelism that database systems exploit. *Thread-parallelism* involves the development of multi-threaded software partitioning a task into subtasks and concurrent threads executing the different subtasks in parallel. The main challenges in thread parallelism are load balancing to make sure all threads execute approximately the same amount of work and contention handling to avoid performance degradation because of resource sharing between threads. Database performance can be boosted by independent instructions in the code-path. Independent instructions can be evaluated in parallel because of the instruction pipelining in the CPUs. This potential overlap is called instruction level parallelism (ILP). For example, consider this pseudo-code snippet, applying a conjunctive filter on tuples of table R:

if(R.a < min\_age)

if(R.b < min\_salary)

add the tuple to results</pre>

The second if-statement instruction depends on the outcome of the first condition, limiting the ILP. Checking both conditions for every tuple, regardless of the outcome of the first condition, increases the ILP but also increases the memory traffic. The optimal execution depends on factors such as the memory latency and the condition selectivity. *Simultaneous multithreading* (SMT) on superscalar CPUs combines both thread-level and instructionlevel parallelism by allowing instructions from multiple threads to be issued at a given cycle. *Data parallelism*, on the other hand, involves applying the same operation on different data elements. Challenges for data parallelism include transforming the control flow of the operators by removing branches so that the same code can be applied to different data elements. This optimization also results in increased ILP. Mainstream processors with SIMD instructions are the most common platforms for vectorized programs.

We are in the midst of a transition from the multi-core to the many-core era. While the number of transistors increases at the rate of Moore's law, the energy efficiency per transistor has been decreasing. Power constraints will eventually prevent all cores being concurrently active [Esmaeilzadeh *et al.*, 2013]. Also, adding cores to a processor results in linear scaling only up to a certain number of cores. Many-cores have an especially high number of cores, which are typically simpler than the cores of traditional CPUs. Simpler cores do not have the same power constraints as more complex CPU cores. Many-cores trade-off ease of development for increased parallelism. GPUs and the Intel Xeon Phi are typical examples of many-core processors.

In this thesis, we focus on data processing powered by GPUs. GPUs are many-core processors with very fast memory suitable for memory bound database queries. In Section 1.1 we discuss our research motivation for GPU database processing to accommodate the increasing needs for lightning-fast processing. Section 1.2 describes the challenges posed by the special GPU processor architecture. In Section 1.3 we formulate the database setting and the problems we are tackling in the present thesis and Section 1.4 is our contribution statement.

#### 1.1 Motivation

Hardware advances make hardware-aware software critical to avoid leaving database performance on the table [Breß *et al.*, 2014]. The exponential growth of data further pushes hardware acceleration for more efficient systems. GPUs have massive parallelism available and high memory bandwidth, matching the speeds of memory bound database workloads [Manegold *et al.*, 2000].

Integrating multiple CPUs can match the raw performance of a GPU processor but not the Performance per Watt. Energy efficiency of large scale data processing systems is becoming critical important with the increased availability of GPUs on the cloud. GPU instances on the cloud support the computing requirements of an increasing number of businesses without the upfront costs of dedicated server solutions[Amazon Web Services, 2016; Microsoft, 2016; MapD, 2016]. For the problems studied in this thesis, GPUs are always the most energy efficient option. Straightforward GPU implementations would not achieve performance speed-ups or energy savings against multi-core solutions but we leverage the GPU performance by adapting the input data layout in the GPU memory and the operator algorithms.

As their memory capacity increases, GPUs are fit for in-memory processing of larger datasets. The NVIDIA K80 GPU has 24GB of available memory [NVIDIA, 2015e]. Our focus on GPUs is also supported by their increased commercial availability. Also, GPU programming interfaces are becoming more programmer-friendly so the learning curve for GPU parallel programming is now less steep [NVIDIA, 2016a].

#### **1.2 GPU Architecture**