# SHIM: A Deterministic Model for Heterogeneous Embedded Systems

Stephen A. Edwards and Olivier Tardieu

Department of Computer Science,

Columbia University

www.cs.columbia.edu/~sedwards

{sedwards,tardieu}@cs.columbia.edu

#### **Definition**

#### **shim** \'shim\ n

- 1: a thin often tapered piece of material (as wood, metal, or stone) used to fill in space between things (as for support, leveling, or adjustment of fit).

- 2 : Software/Hardware Integration Medium, a model for describing hardware/software systems

#### Conclusions

SHIM is an effective model of computation for embedded hardware/software systems

Formal semantics guarantee determinism & boundedness

Easy to synthesize into hardware and software

Applicable to large, important class of systems, but not all

Embedded systems should be designed on the SHIM model of computation

# Robby Roto (Bally/Midway, 1981)

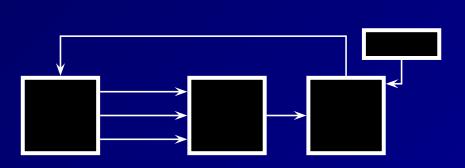

#### Robby Roto Block Diagram

## **HW/SW Interaction**

#### **SHIM Wishlist**

- Mixes synchronous and asynchronous styles

Need multi-rate for hardware/software systems

- Delay-insensitive (Deterministic)

Want simulated behavior to reflect reality

Verify functionality and performance separately

- Only requires bounded resources

Hardware resources fundamentally bounded

- Formal semantics

Do not want arguments about what something means

#### The SHIM Model

Sequential processes

Unbuffered point-to-point communication channels exchange data tokens

Fixed topology

Asynchronous

Synchronous communication events

Delay-insensitive: sequence of data through any channel independent of scheduling policy (the Kahn principle)

"Kahn networks with rendezvous communication"

#### **SHIM vs. Other Models**

#### SHIM CSP Kahn SDF Haste Sync Petri

| Deterministic             | $\sqrt{}$ |           | $\sqrt{}$ | $\sqrt{}$ |           | $\sqrt{}$ |           |

|---------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Blocking<br>Communication | $\sqrt{}$ | $\sqrt{}$ |           |           | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ |

| Bounded Buffers           | $\sqrt{}$ | $\sqrt{}$ |           | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ |           |

| Multi-Rate                | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ |           | $\sqrt{}$ |

| Data-Dependent<br>Rates   | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ |           | $\sqrt{}$ |           | $\sqrt{}$ |

| Easy-To-Schedule          | $\sqrt{}$ | $\sqrt{}$ |           | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ |

| Static Scheduling         |           |           |           |           |           |           |           |

## **Modeling in SHIM**

To model introduce

Buffers Buffer processes

Interrupts Polling and periodic

communication

Synchrony Clock signals

Synchronous dataflow Buffers

Sensors Source processes

Arbiters A deterministic algorithm

## **Modeling Time in SHIM**

SHIM is timing-independent

Philosophy: separate functional requirements from performance requirements

Like synchronous digital logic: establish correct function independent of timing, then check and correct performance errors

Vision: clock processes impose execution rates, checked through static timing analysis

## The Syntax of Tiny-SHIM

```

e ::= L \qquad \text{(literal)} \qquad s ::= V = e \qquad \text{(assignment)}

\mid V \qquad \text{(variable)} \qquad \mid \text{ if ($e$ ) $s$ else $s$ (conditional)}

\mid op \ e \qquad \text{(unary op)} \qquad \mid \text{ while ($e$ ) $s$} \qquad \text{(loop)}

\mid e \ op \ e \ \text{(binary op)} \qquad \mid s \ ; \ s \qquad \text{(sequencing)}

\mid (e \ ) \ \text{(paren)} \qquad \mid \text{read($C, V$)} \qquad \text{(blocking read)}

\mid \text{write($C, e$)} \qquad \text{(blocking write)}

\mid \{s\} \qquad \text{(grouping)}

```

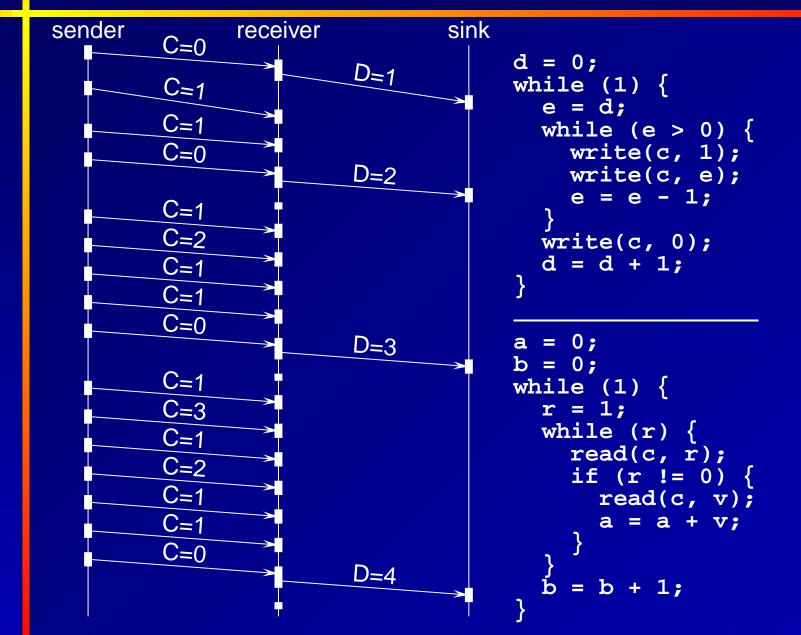

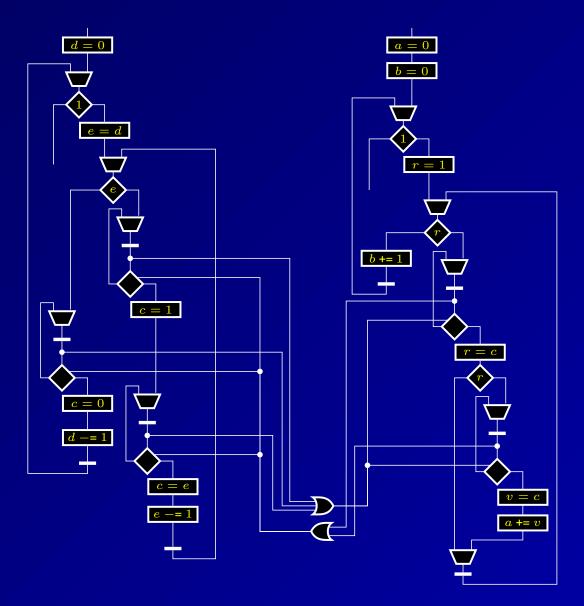

## **Example Processes**

Local variables: d, e

```

d = 0;

while (1) {

e = d;

while (e > 0) {

write(c, 1);

write(c, e);

e = e - 1;

write(c, 0);

d = d + 1;

```

Local variables: a, b, r, v

```

a = 0;

b = 0;

while (1) {

r = 1;

while (r) {

read(c, r);

if (r != 0) {

read(c, v);

a = a + v;

b = b + 1;

```

C

#### **Behavior of the Processes**

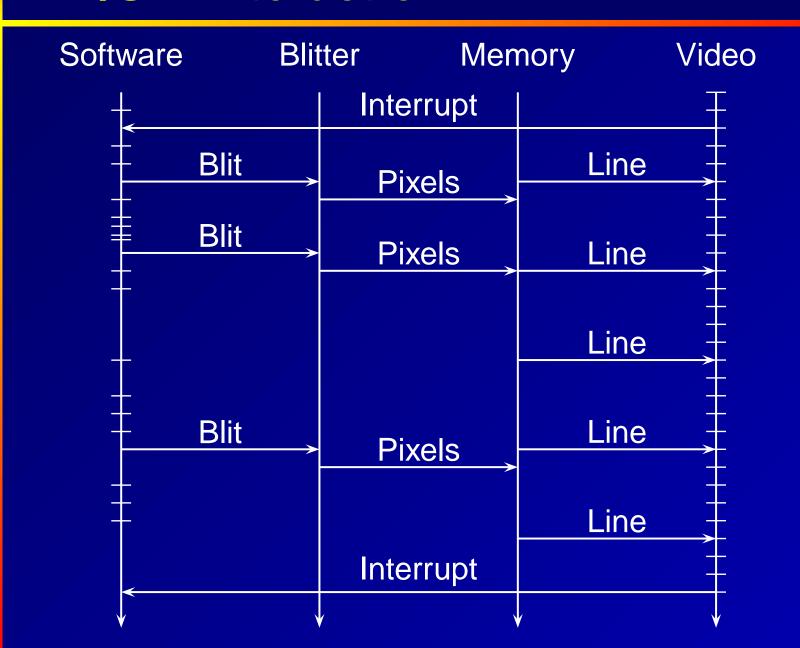

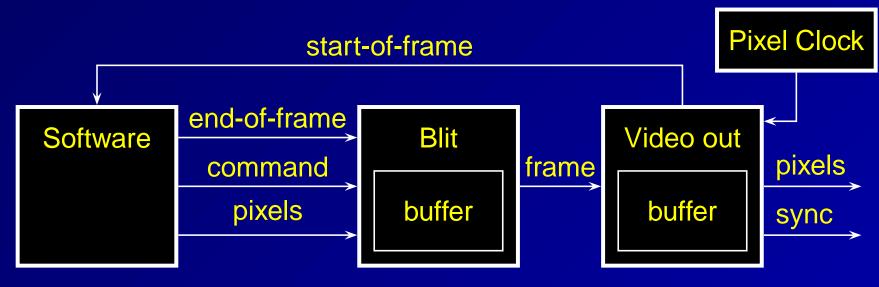

## Robby Roto in SHIM: Block Diagram

while the player is alive do

Wait for start-of-frame

...game logic...

Write "false" to end-of-frame

Write to the blitter

...game logic...

Write "true" to end-of-frame

while 1 do

while not end-of-frame do

Read blit command

Write pixels to memory

Write frame

#### while 1 do

Write start-of-frame

for each line do

Emit line timing signals

for each pixel do

Wait for pixel clock

Read pixel from memo

Send pixel to display

Read next frame

## **Translating Tiny-SHIM to Software**

Each process becomes a C function with static variable that can resume itself

Main scheduler takes runnable process from head of list and calls its function.

Processes mark themselves blocked, can scheduler their communication partner.

#### **C** Translation Example

```

process p1 {

output C;

write(C, 42);

}

```

```

process p2 {

input C;

int v;

read(C, v);

}

```

#### **C** Declarations

```

Linked list of runnable processes

typedef struct process_struct {

void (*process)(void);

Function of process

Next runnable process

struct process_struct *next;

} process_t;

Channel datatype

typedef struct {

Value being transferred

int value:

process_t *waiting;

Blocked process, if any

} channel t;

channel_t C = { 0, 0 };

Definition of channel C

State of each process

int p1_state = 0;

int p2_state = 0;

void p1_function(void);

Process functions

(forward declarations)

void p2_function(void);

Linked List

process_t p1 = { p1_function, 0 };

process_t p2 = { p2_function, &p1 };

of runnable

process_t *head_process = &p2;

processes

```

#### The (Trivial) Scheduler

```

int main()

{

process_t *running_process;

while (head_process) {

running_process = head_process;

Remove head

head_process = running_process->next;

(*(running_process->process))();

Run it

}

return 0;

Everything terminated or deadlocked

}

```

## **The Writing Process**

```

void p1_function() {

switch (p1_state) {

Resume at current state

case 1: goto L1;

case 0: goto L0;

L0:

write(C, 42)

C.value = 42;

if (C.waiting) {

Schedule

(C.waiting)->next = head process;

reading process

head_process = C.waiting;

C.waiting = &p1;

p1_state = 1;

Suspend

return;

process p1 {

L1:

output C;

write(C, 42);

```

## **The Reading Process**

```

void p2_function() {

static int v;

switch (p2_state) {

resume at current state

case 0: goto L0;

case 1: goto L1;

L0:

process p2 {

read(C, v)

if (!C.waiting) {

input C;

C.waiting = &p2;

int v;

p2 state = 1;

Suspend

return;

read(C, v);

L1:

v = C.value;

(C.waiting)->next = head_process;

Schedule

writing process

head process = C.waiting;

C.waiting = 0;

```

#### Write before Read

```

/* write(C, 42) */

/* read(C, v) */

C.value = 42;

if (!C.waiting) {

if (C.waiting) {

C.waiting = &p2;

(C.waiting)->next =

p2_state = 1;

head process;

return;

head process =

C.waiting;

L1:

v = C.value;

(C.waiting)->next =

C.waiting = &p1;

p1_state = 1;

head_process;

head_process =

return;

C.waiting;

L1:

C.waiting = 0;

```

#### **Read before Write**

```

/* write(C, 42) */

/* read(C, v) */

C.value = 42;

if (!C.waiting) {

if (C.waiting) {

C.waiting = &p2;

(C.waiting)->next =

p2_state = 1;

head_process;

return;

head_process =

C.waiting;

L1:

v = C.value;

(C.waiting)->next =

C.waiting = &p1;

p1_state = 1;

head_process;

head_process =

return;

C.waiting;

L1:

C.waiting = 0;

```

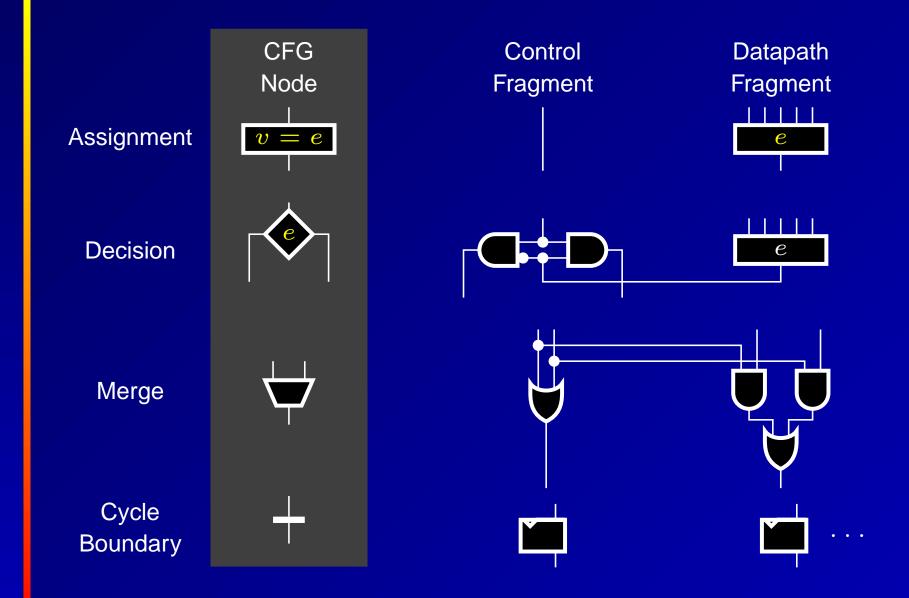

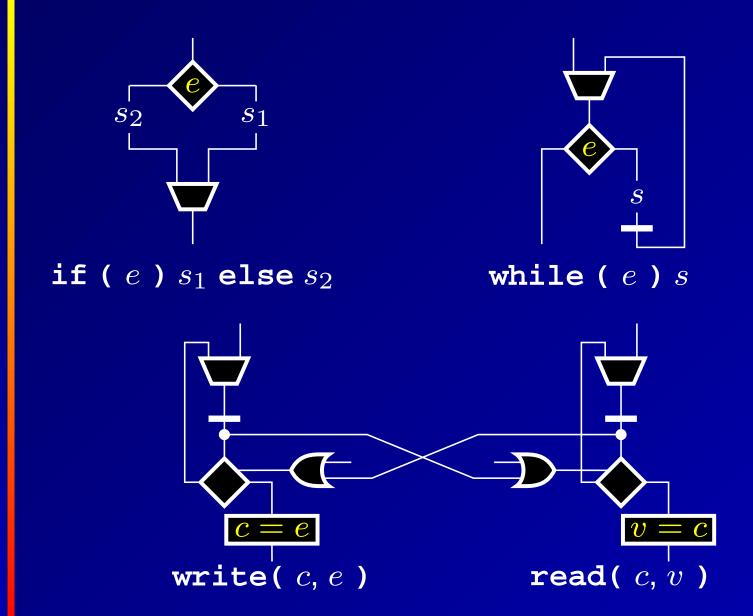

## **Translating Tiny-SHIM to Hardware**

## **Translation Patterns**

#### **Hardware Translation Example**

```

d = 0;

while (1) {

e = d;

while (e > 0) {

write(c, 1);

write(c, e);

e = e - 1;

write(c, 0);

d = d + 1;

a = 0;

b = 0;

while (1) {

r = 1;

while (r) {

read(c, r);

if (r != 0) {

read(c, v);

a = a + v;

```

## The SOS Semantics of Tiny-SHIM

Process memory state

$\langle \sigma, p \rangle$  Process p in state  $\sigma$

Single-process rule  $\Rightarrow$  System rule

$\mathcal{E}(\sigma,e)$  Value of e in  $\sigma$

$\langle \sigma \rangle$  Terminated in state  $\sigma$

$$\frac{\mathcal{E}(\sigma,e) = n}{\langle \sigma,v = e \rangle \to \langle \sigma[v \leftarrow n] \rangle} \qquad \text{(assign)}$$

$$\frac{\mathcal{E}(\sigma,e)\neq 0}{\langle \sigma, \text{if (e) } p \text{ else } q\rangle \rightarrow \langle \sigma,p\rangle} \qquad \text{(if-true)}$$

$$\frac{\mathcal{E}(\sigma,e)=0}{\langle \sigma, \text{if (e) } p \text{ else } q \rangle \rightarrow \langle \sigma,q \rangle} \qquad \text{(if-false)}$$

## **Semantics of Looping & Sequencing**

$$\frac{\mathcal{E}(\sigma,e)\neq 0}{\langle \sigma, \text{while (e) } p\rangle \to \langle \sigma, p \text{ ; while (e) } p\rangle} \quad \text{(while-true)}$$

$$\frac{\mathcal{E}(\sigma, e) = 0}{\langle \sigma, \text{while (e) } p \rangle \to \langle \sigma \rangle} \qquad \text{(while-false)}$$

$$\frac{\langle \sigma, p \rangle \xrightarrow{a} \langle \sigma', p' \rangle}{\langle \sigma, p ; q \rangle \xrightarrow{a} \langle \sigma', p' ; q \rangle}$$

(seq)

$$\frac{\langle \sigma, p \rangle \xrightarrow{a} \langle \sigma' \rangle}{\langle \sigma, p ; q \rangle \xrightarrow{a} \langle \sigma', q \rangle}$$

(seq-term)

#### **Communication and Concurrency**

$$\langle \sigma, \mathtt{read}(c, v) \rangle \xrightarrow{c \text{ get } n} \langle \sigma[v \leftarrow n] \rangle$$

(read)

$$\frac{\mathcal{E}(\sigma, e) = n}{\langle \sigma, \mathbf{write}(c, e) \rangle \xrightarrow{c \text{ put } n} \langle \sigma \rangle}$$

(write)

$$\frac{\langle \sigma, p \rangle \to s}{\{\langle \sigma, p \rangle\} \uplus S \Rightarrow \{s\} \uplus S}$$

(step)

$$\frac{\langle \sigma, p \rangle \xrightarrow{c \text{ put } n} s \quad \langle \sigma', p' \rangle \xrightarrow{c \text{ get } n} s'}{\{\langle \sigma, p \rangle, \langle \sigma', p' \rangle\} \uplus S \Rightarrow \{s, s'\} \uplus S} \quad \text{(sync)}$$

#### **Summary**

- SHIM: A delay-insensitive (deterministic) model of computation that supports synchrony and asynchrony

- Tiny-SHIM: A little language that embodies the model

- A procedure for translating Tiny-SHIM into software

- A procedure for translating Tiny-SHIM into hardware

- Formal operational semantics of Tiny-SHIM

#### **Ongoing Work**

- Relaxation of block-on-single-channel rule

- Complete hardware/software design language

- Static analysis of deadlock

- Translation optimization for hardware and software