#### Altera's Avalon Communication Fabric

#### Stephen A. Edwards

**Columbia University**

Spring 2015

Something like "PCI on a chip"

Described in Altera's Avalon Memory-Mapped Interface Specification document.

Protocol defined between peripherals and the "bus" (actually a fairly complicated circuit).

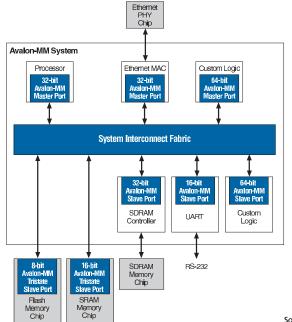

## Intended System Architecture

Source: Altera

#### **Masters and Slaves**

Most bus protocols draw a distinction between

**Masters**: Can initiate a transaction, specify an address, etc. E.g., the Nios II processor

**Slaves**: Respond to requests from masters, can generate return data. E.g., a video controller

Most peripherals are slaves.

Masters speak a more complex protocol

Bus arbiter decides which master gains control

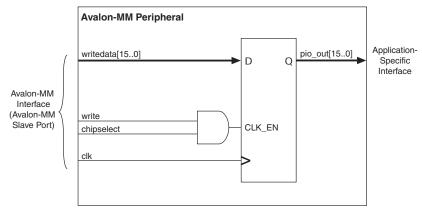

## The Simplest Slave Peripheral

Basically, "latch when I'm selected and written to."

#### **Slave Signals**

#### For a 16-bit connection that spans 32 halfwords,

clk reset chipselect address[4:0] read Avalon Slave write byteenable[1:0] writedata[15:0] readdata[15:0] irq

## **Avalon Slave Signals**

clk reset chipselect address[..] read write writedata[..] byteenable[..] readdata[..] irq

Master clock Reset signal to peripheral Asserted when bus accesses peripheral Word address (data-width specific) Asserted during peripheral→bus transfer Asserted during bus→peripheral transfer Data from bus to peripheral Indicates active bytes in a transfer Data from peripheral to bus peripheral→processor interrupt request

All are optional, as are many others for, e.g., flow-control and burst transfers.

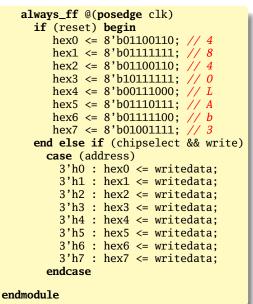

# In SystemVerilog

| <pre>module myslave(input</pre> | logic              | clk,        |

|---------------------------------|--------------------|-------------|

| input                           | logic              | reset,      |

|                                 | <b>logic</b> [7:0] | writedata,  |

| -                               | logic              | write,      |

| -                               | logic              | chipselect, |

| input                           | <b>logic</b> [2:0] | address);   |

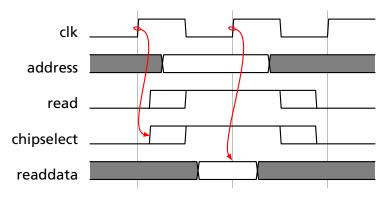

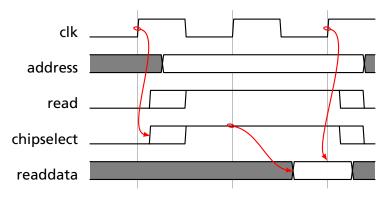

#### **Basic Slave Read Transfer**

Bus cycle starts on rising clock edge

Data latched at next rising edge

Such a peripheral must be purely combinational

### Slave Read Transfer w/ 1 Wait State

Bus cycle starts on rising clock edge

Data latched two cycles later

Approach used for synchronous peripherals

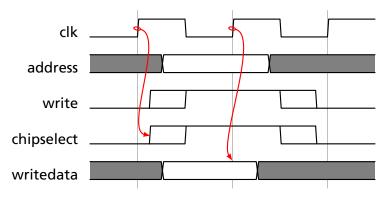

## Basic Async. Slave Write Transfer

Bus cycle starts on rising clock edge

Data available by next rising edge

Peripheral may be synchronous, but must be fast

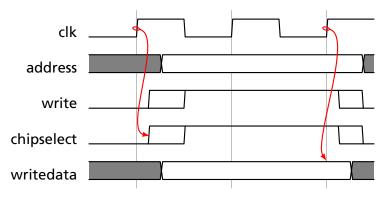

Basic Async. Slave Write w/ 1 Wait State

Bus cycle starts on rising clock edge

Peripheral latches data two cycles later

For slower peripherals

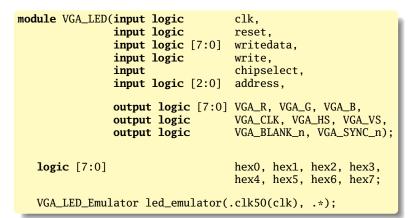

#### The VGA\_LED Emulator Peripheral

## The VGA\_LED Emulator Peripheral