## **CSEE W3827**

## Fundamentals of Computer Systems Homework Assignment 5

Profs. Stephen A. Edwards & Martha Kim

Columbia University

Due April 18, 2012 at 1:10 PM

Write your name and UNI on your solutions

Show your work for each problem; we are more interested in how you get the answer than whether you get the right answer.

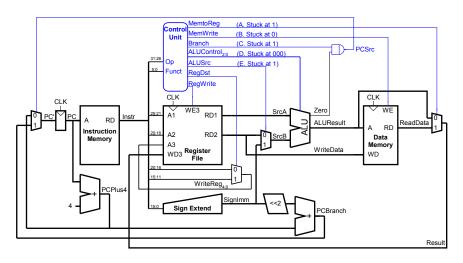

(25 pts.) Imagine each of the five control wires (A - E) in the above processor are stuck at a particular value. For each fault, provide an instruction that will still work and a second that will not. You should assume in each of the five cases, that all other wires are operating properly. Opcodes alone are sufficient, unless the operands are required to specify the scenario.

| Fault | Working Instruction | Broken Instruction       |  |  |  |  |

|-------|---------------------|--------------------------|--|--|--|--|

| A     |                     |                          |  |  |  |  |

| В     |                     |                          |  |  |  |  |

| С     |                     | e.g., add \$t0, \$0, \$0 |  |  |  |  |

| D     |                     |                          |  |  |  |  |

| E     |                     |                          |  |  |  |  |

2. (25 pts.) Extend the single-cycle MIPS processor to support jal (j-format, opcode=000011).

| Inst.  | OP     | RegWrite | RegDst | ALUSrc | Branch | MemWrite | MemToReg | ALUOp |

|--------|--------|----------|--------|--------|--------|----------|----------|-------|

| R-type | 000000 | 1        | 1      | 0      | 0      | 0        | 0        | 1-    |

| lw     | 100011 | 1        | 0      | 1      | 0      | 0        | 1        | 00    |

| SW     | 101011 | 0        | -      | 1      | 0      | 1        | -        | 00    |

| beq    | 000100 | 0        | -      | 0      | 1      | 0        | -        | 01    |

- 3. (25 pts.) Consider a program, P, with 1 billion dynamic instructions, 50% R-Rype, 10% each of loads and stores, and 30% branches.

- (a) How long would P take to execute on a single cycle processor with a 100MHz clock?

- (b) Assuming a multicycle processor where R-type instructions take 4 cycles, loads and stores 5 cycles, and branches 3 cycles, what is the CPI of P?

- (c) Assuming the multicycle processor operated at 400MHz, how long would it take to execute P?

4. (25 pts.) Consider a new MIPS instruction "conditional move" or cmov. The instruction cmov \$1, \$2, \$3 means "copy the value in register 2 into register 1 if register 3 is nonzero".

If a processor does not support the cmov instruction, the function of the cmov instruction can be executed via software:

```

beq $3, $0, DONE

add $1, $2, $0

DONE

```

Imagine two single-cycle MIPS processors, P and  $P_{cmov}$ . P runs at 100MHz and does not implement the cmov instruction.  $P_{cmov}$  runs at 90MHz does.

- (a) Consider a 1 billion instruction application, called  $A_{cmov}$ , of which 5% of the instructions are cmov instructions. How long would it take to execute  $A_{cmov}$  on  $P_{cmov}$ ?

- (b) If  $A_{cmov}$  were modified to remove all instances of cmov, creating A, how many dynamic instructions would A have? Assume that the condition was true for all dynamic cmovs in  $A_{cmov}$ .

- (c) How long would

- i. A take to execute on P?

- ii. A take to execute on  $P_{cmov}$ ?