# **CSEE W3827**

# Fundamentals of Computer Systems Homework Assignment 1

Profs. Stephen A. Edwards & Martha Kim

Columbia University

Due September 20th, 2012 at 10:00 AM

Fill in this PDF form using *Adobe Acrobat Reader*, save it as PDF, and submit it through CourseWorks.

Do not use Preview or another PDF viewer, which is unlikely to work correctly.

Name:

Uni:

1. (5 pts.) What are the values, in decimal, of the following bytes if they are interpreted as 8-bit numbers in

00001011 10001110

binary

one's complement

two's complement

| 2. | (5 pts.) Show how to        | perform $5 + -10 = -5$   | 5 in 5-bit               |

|----|-----------------------------|--------------------------|--------------------------|

|    | Signed-magnitude<br>numbers | One's Complement numbers | Two's Complement numbers |

|    | +                           | +                        | +                        |

3. (10 pts.) Complete the truth table for the following Boolean functions:

$$a = XY + \overline{X}\overline{Y}Z + X\overline{Z}$$

$$b = (X + Y)(Y + \overline{Z})(\overline{X} + Z)$$

| X | Y | Z | a | b |

|---|---|---|---|---|

| 0 | 0 | 0 |   |   |

| 0 | 0 | 1 |   |   |

| 0 | 1 | 0 |   |   |

| 0 | 1 | 1 |   |   |

| 1 | 0 | 0 |   |   |

| 1 | 0 | 1 |   |   |

| 1 | 1 | 0 |   |   |

| 1 | 1 | 1 |   |   |

4. (30 pts.) Consider the function *F*, whose truth table is below.

| X | Y | Z | F | (a) Write $F$ as a sum of minterms. Use a          |

|---|---|---|---|----------------------------------------------------|

| 0 | 0 | 0 | 0 | leading "!" to denote negation. Two                |

| 0 | 0 | 1 | 0 | have been done for you.                            |

| 0 | 1 | 0 | 1 |                                                    |

| 0 | 1 | 1 | 1 |                                                    |

| 1 | 0 | 0 | 1 | (b) Write F as a product of maxterms. Two          |

| 1 | 0 | 1 | 0 | have been done for you.                            |

| 1 | 1 | 0 | 1 |                                                    |

| 1 | 1 | 1 | 0 |                                                    |

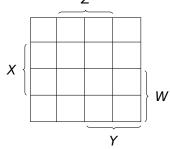

|   |   |   |   | (c) Fill in the Karnaugh map for <i>F</i> as shown |

below. You do not have to simplify it.

In Logisim,

(d) Implement the circuit corresponding to your minterms expression of F. Make sure to label the three inputs "X," "Y," and "Z" and the output "F." Verify your circuit using Logisim's Combinational Analysis feature (Project→Analyze Circuit).

Save your solution as "hw1-4d.circ" and upload it to CourseWorks along with your filled-in PDF file.

(e) Implement the circuit corresponding to your maxterms expression of *F*. Again, verify your work.

Save your solution as "hw1-4e.circ" and upload it.

5. (10 pts.) Consider the function *F* whose truth table is shown below

| W | X | Y | Z | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 |

|   |   |   |   |   |

(a) Write the function *F* in sum-of-minterms form. Two are given.

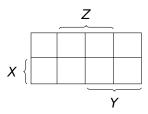

(b) Fill in this Karnaugh map for F

(c) Use your Karnaugh map to write a minimal sum-of-products representation for *F*

6. (40 pts.) Intel's 4004 microprocessor, released in 1971, was the first single-chip microprocessor. Most instructions were 8 bits long, but certain ones (JCN, FIM, JUN, JMS, and ISZ) took 16 bits.

Create a minimal circuit in Logisim that decodes the first byte of the instruction and generates a "1" only when the instruction has a second byte.

Name your eight inputs R3, R2, R1, R0, A3, A2, A1, A0, which represent the bits of the first "OPR" and "OPA" words mentioned in the attached data sheet. Have it generate a single output named "TWO."

Name your solution "hw1-6.circ" and submit it via Courseworks.

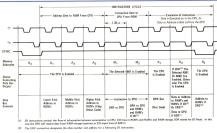

## MCS-4 Operation

Figure 2. MCS-4 Basic Instruction Cycle

## Instruction Set

[Those instructions preceded by an asterisk (\*) are 2 word instructions that occupy 2 successive locations in ROM] MACHINE INSTRUCTIONS

| MNEMONIC        | OPR<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>     | OPA<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>                                                         | DESCRIPTION OF OPERATION                                                                                                                                                                                               |

|-----------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP             | 0000                                                                   | 0000                                                                                                                       | No operation.                                                                                                                                                                                                          |

| *JCN            | 0 0 0 1<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | C <sub>1</sub> C <sub>2</sub> C <sub>3</sub> C <sub>4</sub><br>A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> | Jump to ROM address A2 A2 A2 A2 A1 A1 A1 A1 (within the same ROM that contains this JCN instruction) if condition $C_1 C_2 C_3 C_4^{(1)}$ is true, otherwise skip (go to the next instruction in sequence).            |

| *FIM            | 0 0 1 0<br>D <sub>2</sub> D <sub>2</sub> D <sub>2</sub> D <sub>2</sub> | R R R 0<br>D <sub>1</sub> D <sub>1</sub> D <sub>1</sub> D <sub>1</sub>                                                     | Fetch immediate (direct) from ROM Data $\mathrm{D}_2$ , $\mathrm{D}_1$ to Index register pair location RRR,(2)                                                                                                         |

| SRC             | 0 0 1 0                                                                | RRR1                                                                                                                       | Send the address (contents of index register pair RRR) to ROM and RAI at X <sub>2</sub> and X <sub>3</sub> time in the Instruction Cycle.                                                                              |

| FIN             | 0 0 1 1                                                                | RRRO                                                                                                                       | Fetch Indirect from ROM, Send contents of Index register pair location 0<br>out as an address. Data fetched is placed into register pair location RRR at<br>A1 and A2 time in the Instruction Cycle.                   |

| JIN             | 0 0 1 1                                                                | RRR1                                                                                                                       | Jump indirect. Send contents of register pair RRR out as an address<br>at A <sub>1</sub> and A <sub>2</sub> time in the Instruction Cycle.                                                                             |

| *JUN            | 0 1 0 0<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | A <sub>3</sub> A <sub>3</sub> A <sub>3</sub> A <sub>3</sub><br>A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> | Jump unconditional to ROM address A <sub>3</sub> , A <sub>2</sub> , A <sub>1</sub> .                                                                                                                                   |

| *JMS            | 0 1 0 1<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | A3 A3 A3 A3<br>A1 A1 A1 A1                                                                                                 | Jump to subroutine ROM address A <sub>3</sub> , A <sub>2</sub> , A <sub>1</sub> , save old address. (Up 1 leve<br>in stack.)                                                                                           |

| INC             | 0 1 1 0                                                                | RRRR                                                                                                                       | Increment contents of register RRRR, (3)                                                                                                                                                                               |

| *ISZ            | 0 1 1 1<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | R R R R<br>A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub>                                                     | Increment contents of register RRRR. Go to ROM address A <sub>2</sub> , A <sub>1</sub> (within the same ROM that contains this ISZ instruction) if result ≠0, otherwise skip (go to the next instruction in sequence). |

| ADD             | 1000                                                                   | RRRR                                                                                                                       | Add contents of register RRRR to accumulator with carry.                                                                                                                                                               |

| SUB             | 1 0 0 1                                                                | RRRR                                                                                                                       | Subtract contents of register RRRR to accumulator with borrow.                                                                                                                                                         |

| LD              | 1 0 1 1                                                                | RRRR                                                                                                                       | Load contents of register RRRR to accumulator.                                                                                                                                                                         |

| хсн             | 1 0 1 1                                                                | RRRR                                                                                                                       | Exchange contents of index register RRRR and accumulator,                                                                                                                                                              |

| BBL             | 1 1 0 0                                                                | DDDD                                                                                                                       | Branch back (down 1 level in stack) and load data DDDD to accumulator,                                                                                                                                                 |

| LDM             | 1 1 0 1                                                                | DDDD                                                                                                                       | Load data DDDD to accumulator.                                                                                                                                                                                         |

| e Notes on Page | a a                                                                    |                                                                                                                            | Continued on pag                                                                                                                                                                                                       |

#### INPUT/OUTPUT AND RAM INSTRUCTIONS

(The RAM's and ROM's operated on in the I/O and RAM instructions have been previously selected by the last SRC instruction executed.)

| MNEMONIC           | OPR<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | OPA<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | DESCRIPTION OF OPERATION                                                                              |

|--------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| WRM                | 1 1 1 0                                                            | 0 0 0 0                                                            | Write the contents of the accumulator into the previously selected<br>RAM main memory character.      |

| WMP                | 1 1 1 0                                                            | 0001                                                               | Write the contents of the accumulator into the previously selected<br>RAM output port. (Output Lines) |

| WRR                | 1 1 1 0                                                            | 0 0 1 0                                                            | Write the contents of the accumulator into the previously selected<br>ROM output port. (I/O Lines)    |

| WRφ (4)            | 1 1 1 0                                                            | 0 1 0 0                                                            | Write the contents of the accumulator into the previously selected<br>RAM status character 0.         |

| WR1 <sup>(4)</sup> | 1 1 1 0                                                            | 0 1 0 1                                                            | Write the contents of the accumulator into the previously selected<br>RAM status character 1.         |

| WR2 <sup>(4)</sup> | 1 1 1 0                                                            | 0 1 1 0                                                            | Write the contents of the accumulator into the previously selected<br>RAM status character 2.         |

| WR3 <sup>(4)</sup> | 1 1 1 0                                                            | 0 1 1 1                                                            | Write the contents of the accumulator into the previously selected<br>RAM status character 3.         |

| SBM                | 1 1 1 0                                                            | 1000                                                               | Subtract the previously selected RAM main memory character from accumulator with borrow.              |

| RDM                | 1 1 1 0                                                            | 1 0 0 1                                                            | Read the previously selected RAM main memory character<br>into the accumulator.                       |

| RDR                | 1 1 1 0                                                            | 1 0 1 0                                                            | Read the contents of the previously selected ROM input port into the accumulator, (I/O Lines)         |

| ADM                | 1 1 1 0                                                            | 1 0 1 1                                                            | Add the previously selected RAM main memory character to<br>accumulator with carry.                   |

| RDØ (4)            | 1 1 1 0                                                            | 1 1 0 0                                                            | Read the previously selected RAM status character 0 into accumulator.                                 |

| RD1 <sup>(4)</sup> | 1 1 1 0                                                            | 1 1 0 1                                                            | Read the previously selected RAM status character 1 into accumulator.                                 |

| RD2 <sup>(4)</sup> | 1 1 1 0                                                            | 1 1 1 0                                                            | Read the previously selected RAM status character 2 into accumulator.                                 |

| RD3 <sup>(4)</sup> | 1 1 1 0                                                            | 1 1 1 1                                                            | Read the previously selected RAM status character 3 into accumulator.                                 |

#### ACCUMULATOR GROUP INSTRUCTIONS

| CLB | 1 1 1 1 | 0 0 0 0 | Clear both. (Accumulator and carry)                                                                         |

|-----|---------|---------|-------------------------------------------------------------------------------------------------------------|

| CLC | 1 1 1 1 | 0 0 0 1 | Clear carry.                                                                                                |

| IAC | 1 1 1 1 | 0 0 1 0 | Increment accumulator.                                                                                      |

| CMC | 1 1 1 1 | 0 0 1 1 | Complement carry,                                                                                           |

| CMA | 1 1 1 1 | 0 1 0 0 | Complement accumulator.                                                                                     |

| RAL | 1 1 1 1 | 0 1 0 1 | Rotate left. (Accumulator and carry)                                                                        |

| RAR | 1 1 1 1 | 0 1 1 0 | Rotate right. (Accumulator and carry)                                                                       |

| тсс | 1 1 1 1 | 0 1 1 1 | Transmit carry to accumulator and clear carry.                                                              |

| DAC | 1 1 1 1 | 1000    | Decrement accumulator.                                                                                      |

| rcs | 1 1 1 1 | 1 0 0 1 | Transfer carry subtract and clear carry.                                                                    |

| STC | 1 1 1 1 | 1 0 1 0 | Set carry.                                                                                                  |

| DAA | 1 1 1 1 | 1 0 1 1 | Decimal adjust accumulator.                                                                                 |

| КВР | 1 1 1 1 | 1 1 0 0 | Keyboard process. Converts the contents of the accumulator from a<br>one out of four code to a binary code. |

| DCL | 1 1 1 1 | 1 1 0 1 | Designate command line.<br>(See note 1 on page 3.)                                                          |

### NOTES: (1) The condition code is assigned as follows:

C<sub>1</sub> = 1 Invert jump condition C<sub>1</sub> = 0 Not Invert jump condition C<sub>3</sub> = 1 Jump if carry/link is a 1

$C_2 = 1$  Jump if accumulator is zero  $C_4 = 1$  Jump if test signal is a 0

(2) RRR is the address of 1 of 8 index register pairs in the CPU.

(3) RRRR is the address of 1 of 16 index registers in the CPU.

(4) Each RAM chip has 4 registers, each with twenty 4-bit characters subdivided into 16 main memory characters and 4 status characters. Chip number. RAM register and main memory character are addressed by an SRC instruction. For the selected chip and register, however, status character locations are selected by the instruction code (OPA).