# Compiling Irregular Software to Specialized Hardware

**Richard Townsend**

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

**COLUMBIA UNIVERSITY**

2019

©2019 Richard Townsend All rights reserved

#### ABSTRACT

## Compiling Irregular Software to Specialized Hardware Richard Townsend

High-level synthesis (HLS) has simplified the design process for energy-efficient hardware accelerators: a designer specifies an accelerator's behavior in a "high-level" language, and a toolchain synthesizes register-transfer level (RTL) code from this specification. Many HLS systems produce efficient hardware designs for regular algorithms (i.e., those with limited conditionals or regular memory access patterns), but most struggle with irregular algorithms that rely on dynamic, data-dependent memory access patterns (e.g., traversing pointer-based structures like lists, trees, or graphs). HLS tools typically provide imperative, side-effectful languages to the designer, which makes it difficult to correctly specify and optimize complex, memory-bound applications.

In this dissertation, I present an alternative HLS methodology that leverages properties of functional languages to synthesize hardware for irregular algorithms. The main contribution is an optimizing compiler that translates pure functional programs into modular, parallel dataflow networks in hardware. I give an overview of this compiler, explain how its source and target together enable parallelism in the face of irregularity, and present two specific optimizations that further exploit this parallelism. Taken together, this dissertation verifies my thesis that **pure functional programs exhibiting irregular memory access patterns can be compiled into specialized hardware and optimized for parallelism**.

This work extends the scope of modern HLS toolchains. By relying on properties of pure functional languages, our compiler can synthesize hardware from programs containing constructs that commercial HLS tools prohibit, e.g., recursive functions and dynamic memory allocation. Hardware designers may thus use our compiler in conjunction with existing HLS systems to accelerate a wider class of algorithms than before.

## Contents

| Co  | Contents            |                                               |    |  |  |

|-----|---------------------|-----------------------------------------------|----|--|--|

| Lis | List of Figures v   |                                               |    |  |  |

| Lis | st of '             | Tables                                        | x  |  |  |

| Ac  | Acknowledgements xi |                                               |    |  |  |

| 1   | Intr                | oduction                                      | 1  |  |  |

|     | 1.1                 | My Thesis                                     | 1  |  |  |

|     | 1.2                 | Structure of the Dissertation                 | 2  |  |  |

|     | 1.3                 | High-Level Synthesis and Irregular Algorithms | 3  |  |  |

|     | 1.4                 | Contributions                                 | 4  |  |  |

| 2   | Rela                | ated Work                                     | 8  |  |  |

|     | 2.1                 | High-Level Synthesis                          | 8  |  |  |

|     |                     | 2.1.1 Functional HLS                          | 9  |  |  |

|     |                     | 2.1.2 Irregular HLS                           | 11 |  |  |

|     | 2.2                 | Hardware Dataflow Networks                    | 13 |  |  |

|     | 2.3                 | Parallelizing Divide-and-Conquer Algorithms   | 15 |  |  |

|     |                     | 2.3.1 Software Techniques                     | 15 |  |  |

|     |                     | 2.3.2 Memory Partitioning                     | 16 |  |  |

|     |                     | 2.3.3 HLS for Divide-and-Conquer              | 17 |  |  |

|     | 2.4                 | Optimizing Recursive Data Structures          | 19 |  |  |

| 3   | An (                | Overview of Our Compiler                      | 22 |  |  |

|     | 3.1                 | Our Main IR: a Variant of GHC Core            | 22 |  |  |

|   | 3.2 | The Eı | nd-to-End Compilation Flow                                                                                                          |

|---|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.3 | Lower  | ing Core                                                                                                                            |

|   |     | 3.3.1  | Removing Polymorphism                                                                                                               |

|   |     | 3.3.2  | Making Names Unique                                                                                                                 |

|   |     | 3.3.3  | Lambda Lifting                                                                                                                      |

|   |     | 3.3.4  | Removing Recursion                                                                                                                  |

|   |     | 3.3.5  | Tagging Memory Operations    47                                                                                                     |

|   |     | 3.3.6  | Simplifying Case 49                                                                                                                 |

|   |     | 3.3.7  | Adding <i>Go</i>                                                                                                                    |

|   |     | 3.3.8  | Lifting Expressions                                                                                                                 |

|   |     | 3.3.9  | Optimizing Reads                                                                                                                    |

|   | г   | г      |                                                                                                                                     |

| 4 |     |        | tional Programs to Dataflow Networks 55                                                                                             |

|   | 4.1 |        | ricted Dialect of Core: Floh                                                                                                        |

|   | 4.0 | 4.1.1  | An Example: Map         57                                                                                                          |

|   | 4.2 |        | $ w \text{ Networks } \dots $ |

|   | 4.3 |        | ation from Floh to Dataflow                                                                                                         |

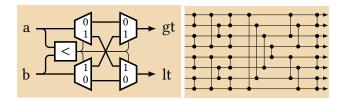

|   |     | 4.3.1  | Translating Expressions    62                                                                                                       |

|   |     | 4.3.2  | Translating Simple Functions and Cases    63                                                                                        |

|   |     | 4.3.3  | Translating Clustered Functions and Cases                                                                                           |

|   |     | 4.3.4  | Putting It All Together: Translating the Map Example                                                                                |

|   | 4.4 |        | ow Networks in Hardware    71                                                                                                       |

|   |     | 4.4.1  | Evaluation Order    72                                                                                                              |

|   |     | 4.4.2  | Stateless Actors                                                                                                                    |

|   |     | 4.4.3  | Stateful Actors    73                                                                                                               |

|   |     | 4.4.4  | Inserting Buffers                                                                                                                   |

|   | 4.5 | Experi | mental Evaluation                                                                                                                   |

|   |     | 4.5.1  | Methodology                                                                                                                         |

|   |     | 4.5.2  | Strict vs. Non-strict Tail Recursive Calls    78                                                                                    |

|   |     | 4.5.3  | Sensitivity to Memory Latency                                                                                                       |

|   |     | 4.5.4  | Sensitivity to Function Latency                                                                                                     |

|   |     |        |                                                                                                                                     |

## 5 Realizing Dataflow Networks in Hardware

| 5.1 | Specif  | fications: Kahn Networks                  | . 83  |

|-----|---------|-------------------------------------------|-------|

|     | 5.1.1   | Kahn Networks                             | . 83  |

|     | 5.1.2   | Dataflow Actors                           | . 85  |

|     | 5.1.3   | Unit-rate, Mux, and Demux Actors          | . 86  |

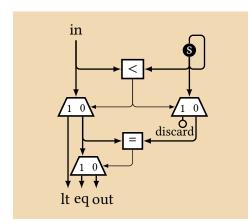

|     | 5.1.4   | Nondeterministic Merge                    | . 87  |

| 5.2 | Hardv   | ware Dataflow Actors                      | . 88  |

|     | 5.2.1   | Communication and Combinational Cycles    | . 88  |

|     | 5.2.2   | Unit-Rate Actors                          | . 89  |

|     | 5.2.3   | Mux and Demux Actors                      | . 90  |

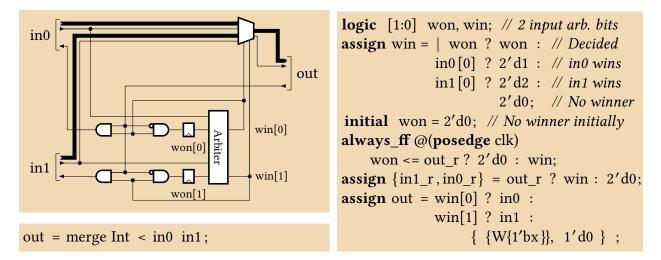

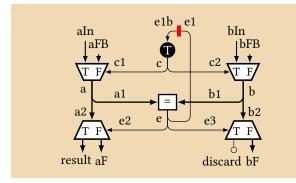

|     | 5.2.4   | Merge Actors                              | . 92  |

| 5.3 | Chanı   | nels in Hardware                          | . 95  |

|     | 5.3.1   | Data and Control Buffers                  | . 95  |

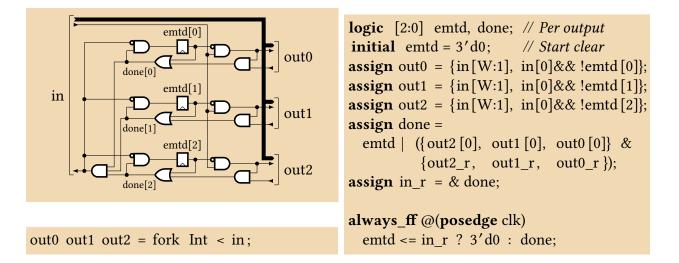

|     | 5.3.2   | Forks                                     | . 97  |

| 5.4 | The A   | argument for Correctness                  | . 98  |

| 5.5 | Our D   | Dataflow IR: DF                           | . 101 |

|     | 5.5.1   | Channel Type Definitions                  | . 101 |

|     | 5.5.2   | Actor Instances and Type Definitions      | . 104 |

|     | 5.5.3   | Checking DF Specifications                | . 106 |

| 5.6 | Exper   | imental Evaluation                        | . 107 |

|     | 5.6.1   | Experimental Networks                     | . 108 |

|     | 5.6.2   | Random Buffer Allocation                  | . 109 |

|     | 5.6.3   | Manual Buffer Allocation                  | . 110 |

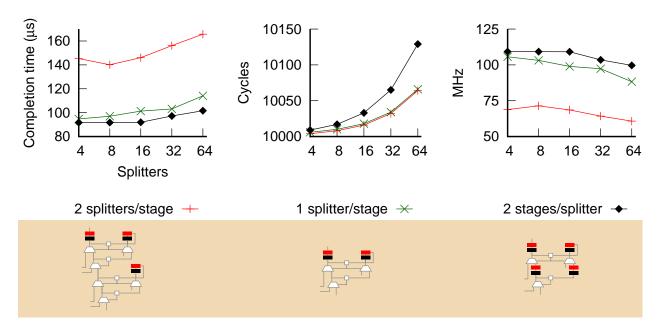

|     | 5.6.4   | Pipelining the Conveyor                   | . 110 |

|     | 5.6.5   | Memory in Dataflow Networks               | . 111 |

|     | 5.6.6   | Overhead of Our Method                    | . 112 |

| 0.4 |         |                                           |       |

| -   |         | g Irregular Divide-and-Conquer Algorithms | 114   |

| 6.1 |         | forming Code                              |       |

|     | 6.1.1   | Finding Divide-and-Conquer Functions      |       |

|     | 6.1.2   | Task-Level Parallelism: Copying Functions |       |

|     | 6.1.3   | Memory-Level Parallelism: Copying Types   |       |

|     | 6.1.4   | New Types and Conversion Functions        |       |

| 6.2 | Partiti | ioning On-Chip Memory                     | . 119 |

6

|    | 6.3   | Experi  | mental Evaluation                      | 121 |

|----|-------|---------|----------------------------------------|-----|

|    |       | 6.3.1   | Exposing Memory-Level Parallelism      | 123 |

|    |       | 6.3.2   | Exploiting Memory-Level Parallelism    | 124 |

| 7  | Pacl  | cing Re | ecursive Data Types                    | 127 |

|    | 7.1   | An Exa  | ample: Appending Lists                 | 128 |

|    | 7.2   | Packin  | g Algorithm                            | 131 |

|    |       | 7.2.1   | Packed Data Types                      | 132 |

|    |       | 7.2.2   | Pack and Unpack Functions              | 133 |

|    |       | 7.2.3   | Injection and Hoisting                 | 135 |

|    |       | 7.2.4   | Simplification                         | 138 |

|    |       | 7.2.5   | Heuristics to Limit Code Growth        | 143 |

|    | 7.3   | Experi  | mental Evaluation                      | 144 |

|    |       | 7.3.1   | Testing Scheme                         | 145 |

|    |       | 7.3.2   | Experimental Results                   | 146 |

| 8  | Con   | clusior | ns and Further Work                    | 150 |

|    | 8.1   | Conclu  | isions                                 | 150 |

|    | 8.2   | Furthe  | r Work                                 | 151 |

|    |       | 8.2.1   | Formalism                              | 151 |

|    |       | 8.2.2   | Extending the Compiler                 | 152 |

|    |       | 8.2.3   | Synthesizing a Realistic Memory System | 152 |

|    |       | 8.2.4   | Improved and Additional Optimizations  | 153 |

| Bi | bliog | raphy   |                                        | 155 |

# List of Figures

| 1.1 | A visualization of the research supporting my thesis. I focus on synthesizing hard-                |    |

|-----|----------------------------------------------------------------------------------------------------|----|

|     | ware from pure functional programs exhibiting irregular memory access patterns,                    |    |

|     | e.g., the function $map f l$ , which applies a function $f$ to each element of a linked list $l$ , |    |

|     | storing the results in a new list (a). I translate these programs into modular, parallel           |    |

|     | dataflow networks in hardware (b), and apply two optimizations that exploit more                   |    |

|     | parallelism in the synthesized circuits: the first improves memory-level parallelism               |    |

|     | in divide-and-conquer algorithms by combining a novel code transformation with                     |    |

|     | a type-based memory partitioning scheme (c); the second packs more data into re-                   |    |

|     | cursive types to improve spatial locality (i.e., data-level parallelism) and reduce an             |    |

|     | irregular program's memory footprint (d)                                                           | 5  |

|     |                                                                                                    |    |

| 3.1 | The abstract syntax of the compiler's main IR: a variant of GHC's Core [124]. We                   |    |

|     | augment this grammar with the regular expression meta-operators * (zero or more), $\mid$           |    |

|     | (choice), and + (one or more). Note that the   token in the <i>type-def</i> rule is actual Core    |    |

|     | syntax, not the choice meta-operator.                                                              | 23 |

| 3.2 | Overview of our compilation flow: we rewrite Haskell programs into increasingly                    |    |

|     | simpler representations until we can perform a syntax-directed translation into Sys-               |    |

|     | temVerilog.                                                                                        | 27 |

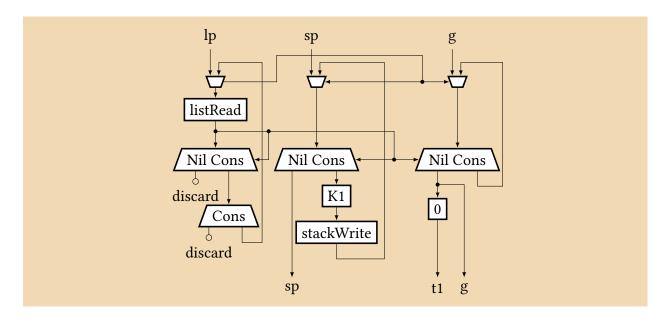

| 3.3 | A dataflow graph for the <i>callLength</i> function. This walks an input list, pushing $K1$        |    |

| 0.0 | onto the stack for each element traversed. Upon reaching the end of the list, the stack            |    |

|     | pointer, an accumulator, and a <i>Go</i> value are passed to the subnetwork implementing           |    |

|     | retLength.                                                                                         | 33 |

|     |                                                                                                    | 00 |

| 3.4 | SystemVerilog for a two output demultiplexer, with one output feeding into a destruct              |    |

|     | actor that dismantles a <i>Cons</i> cell into its respective fields                                | 34 |

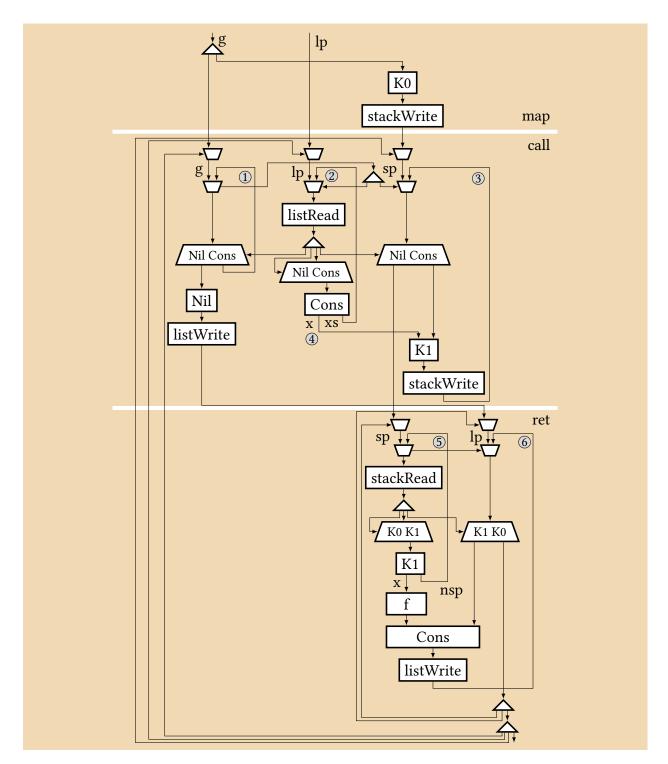

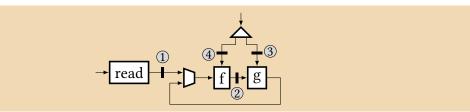

| 4.1 | The <i>map</i> function implemented in Floh. The <i>call</i> function walks the input list and pushes each element on a stack of continuations (replacing function activation records) encoded with a list-like data type; the <i>ret</i> function pops each element <i>x</i> from the stack,                                                                                                                                                                                                                                         |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | applies $f$ to it, and prepends the result to the returned list                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58 |

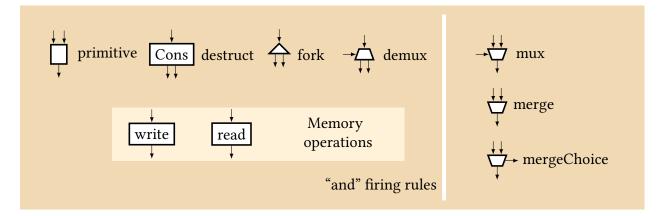

| 4.2 | Our menagerie of dataflow actors. Those left of the line require data on every input channel to fire.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60 |

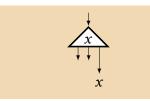

| 4.3 | Translating a reference to a variable $x$ : a connection is made to the fork actor that distributes its value.                                                                                                                                                                                                                                                                                                                                                                                                                        | 62 |

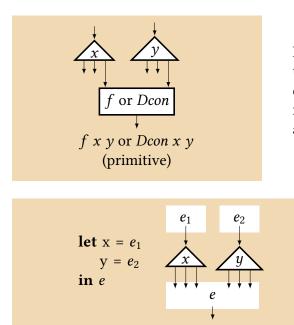

| 4.4 | Translating a data constructor or a primitive, constant-generating, or memory access function call: each argument (one or more variables) is taken from a new connection to that variable's fork actor and the result is the output of the primitive actor                                                                                                                                                                                                                                                                            | 63 |

| 4.5 | Translating a <i>let</i> construct: Each of the newly-bound variables is evaluated and connected to fork actors that make their values available to the body.                                                                                                                                                                                                                                                                                                                                                                         | 63 |

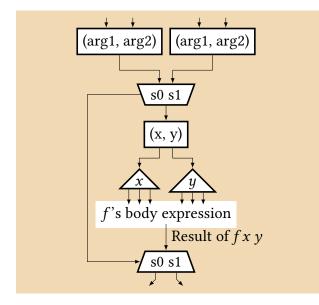

| 4.6 | Translating a simple two-argument function $f$ with two external call sites, $s0$ and $s1$ . Data constructor actors impose strictness by bundling a caller's arguments in a tuple; a destruct actor dismantles the tuple back into the constituent arguments. A mergeChoice actor selects which caller's tuple will access the function, while a demux routes the result to the caller.                                                                                                                                              | 64 |

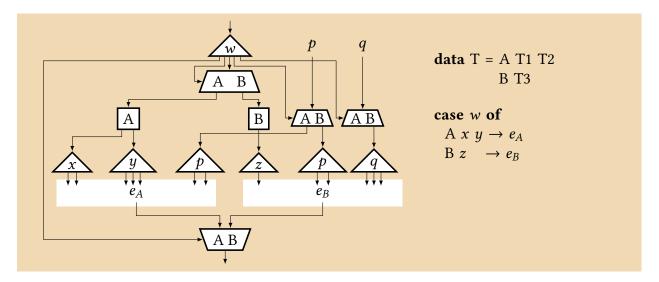

| 4.7 | Translating a <i>case</i> construct: a demux actor routes input $w$ to the destruct actor corresponding to $w$ 's data constructor. Each destruct splits the token into fields: $x$ and $y$ for $A$ or $z$ for $B$ . The data constructor from $w$ also serves as a choice token that drives both the mux that selects the <i>case</i> 's result and the demuxes that steer the values of live variables $p$ and $q$ to the alternatives that use them. The omitted demux output for $q$ means $e_A$ does not reference that variable | 65 |

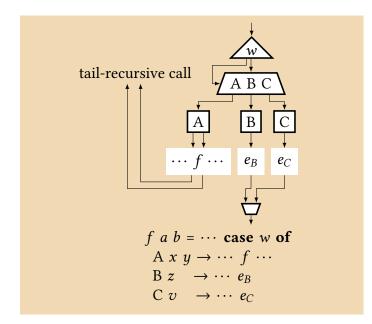

| 4.8 | Translating a <i>case</i> construct containing tail-recursive calls. Values produced by the alternatives are collected at a merge actor; arguments for intra-cluster tail calls are fed to each function's internal call site machinery. Not shown are the demuxes for live variables, which are treated the same as in Figure 4.7.                                                                                                                                                                                                   | 66 |

| 4.9  | Translating function clusters. Functions $f$ and $g$ comprise the cluster since they call                  |    |

|------|------------------------------------------------------------------------------------------------------------|----|

|      | one another recursively. Any values produced by members of a cluster are merged                            |    |

|      | together to form the cluster's output channel; using a mux instead could lead to dead-                     |    |

|      | lock. We omit local demuxes for clustered functions for the same reason. A layer of                        |    |

|      | mux actors below the argument tuple's destruct actor act as a "lock" by preventing                         |    |

|      | multiple external calls from overlapping within a cluster; the presence of a token on                      |    |

|      | the cluster's output channel triggers the "unlocking" of these muxes, allowing an-                         |    |

|      | other external call to access the cluster.                                                                 | 67 |

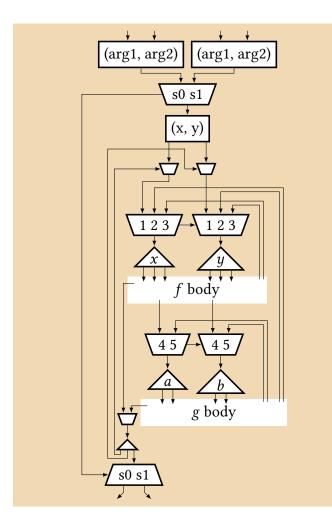

| 4.10 | A dataflow graph for <i>map</i> from Figure 4.1. This initializes the stack ( <i>map</i> ); walks the      |    |

|      | input list, pushing each element on the stack ( <i>call</i> ); then pops each element off the              |    |

|      | stack, applies $f_{i}$ , and places the result at the head of the new list ( <i>ret</i> ). Tail calls to   |    |

|      | <i>call</i> and <i>ret</i> are not strict, decoupling loops 1, 2, and 3, and more importantly, loops 5     |    |

|      | and 6, to enable pipelining                                                                                | 70 |

| 4.11 | A point-to-point link and its flow control protocol, after Cao et al. [18]. Data and                       |    |

|      | <i>valid</i> bits flow downstream, with <i>valid</i> indicating the data lines carry a token; <i>ready</i> |    |

|      | bits flow upstream, indicating that downstream is willing to consume a token. $\ . \ . \ .$                | 72 |

| 4.12 | An example of our buffer allocation scheme (using our third heuristic). We insert                          |    |

|      | buffers to break cycles in the network (e.g., 2) and prevent reconvergent deadlock                         |    |

|      | (e.g., 3)                                                                                                  | 75 |

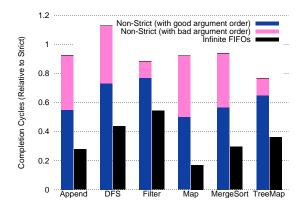

| 4.13 | Non-strict evaluation is generally superior to strict. When combined with a good                           |    |

|      | function argument ordering, the finite, non-strict implementations yield a 1.3–2×                          |    |

|      | speedup over strict.                                                                                       | 79 |

| 4.14 | Mitigating increasing memory latency with non-strict function evaluation                                   | 79 |

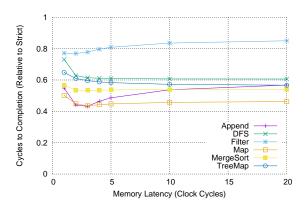

| 5.1  | A recursive definition of Euclid's greatest common divisor algorithm and a dataflow                        |    |

|      | network implementing it. The tail-recursion is implemented with feedback loops. $\ . \ .$                  | 81 |

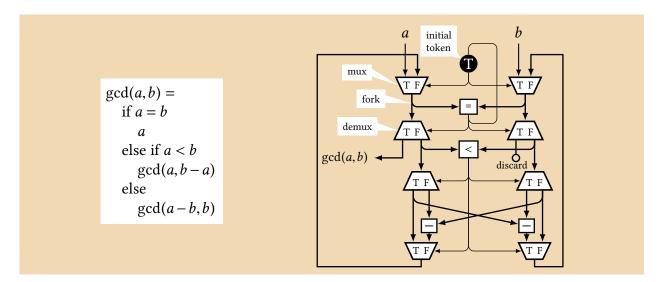

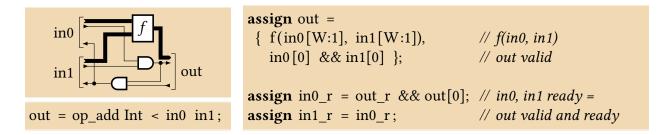

| 5.2  | A unit-rate actor that computes a combinational function $f$ of two $W$ -bit inputs (bit 0                 |    |

|      | of each port carries the "valid" flag) once both arrive. Depicted is the circuit, a sample                 |    |

|      | DF specification of the actor (assuming $f$ is a primitive addition function), and the                     |    |

|      | corresponding SystemVerilog.                                                                               | 90 |

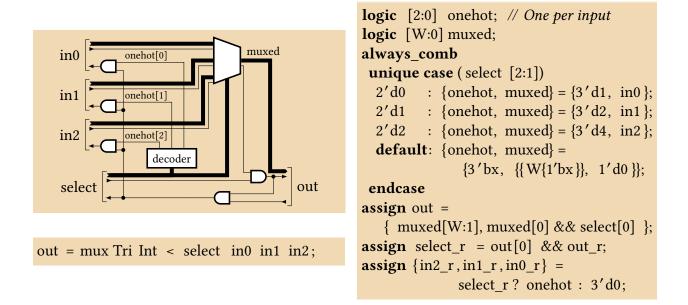

| 5.3  | A three-input <i>W</i> -bit multiplexer; select is 2 bits                                                  | 91 |

| 5.4  | A demultiplexer with a two-bit select input and three $W$ -bit outputs                                     | 91 |

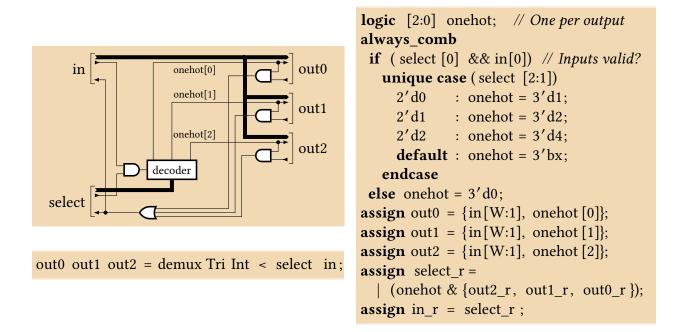

| 5.5  | A merge used to share a unit-rate subnetwork                                                               | 92 |

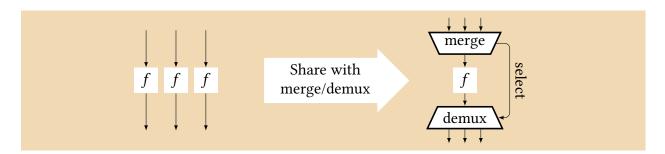

| 5.6  | A two-input nondeterministic merge that reports its arbitration decisions on the 1-bit output <i>sel</i>                                                                   | 93  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

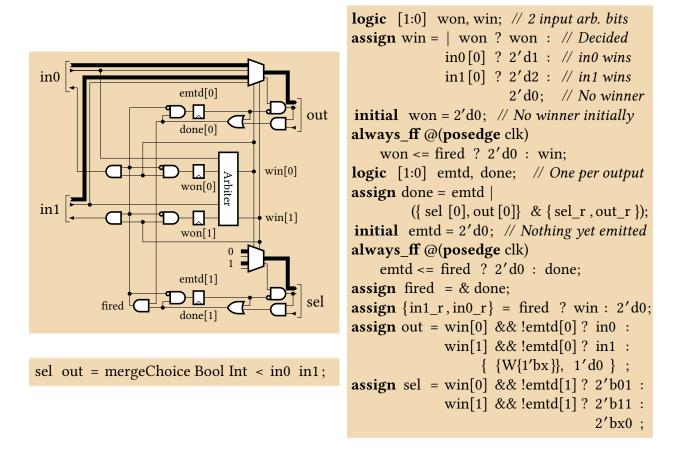

| 5.7  | A two-input nondeterministic merge that does not report its selection.                                                                                                     | 94  |

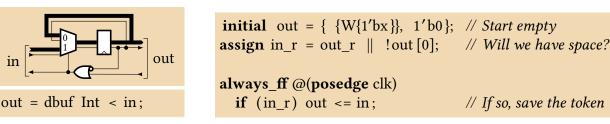

| 5.8  | A data (pipeline) buffer, after Cao et al. [18]. This breaks combinational paths in the data/valid network.                                                                | 95  |

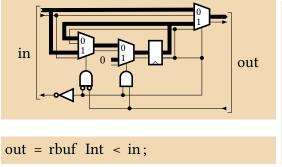

| 5.9  | A control buffer, after Cao et al. [18]. This breaks combinational paths in the (up-<br>stream) <i>ready</i> network.                                                      | 96  |

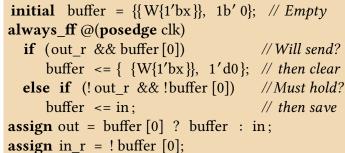

| 5.10 | A three-way fork. An output port's <i>emtd</i> flip-flop is set when the input token has been consumed on that port. All are reset after a token is consumed on every port | 97  |

| 5.11 | A DF program describing the topology and channel types for a portion of GCD from<br>Figure 5.1                                                                             | 102 |

| 5.12 | Syntax of DF. Brackets [], bar  , and asterisk * are meta-symbols denoting grouping, choice, and zero-or-more. Bold characters, including parentheses (), bar  , and caret |     |

| 5.13 | $\wedge$ , are tokens                                                                                                                                                      |     |

| 5.14 |                                                                                                                                                                            |     |

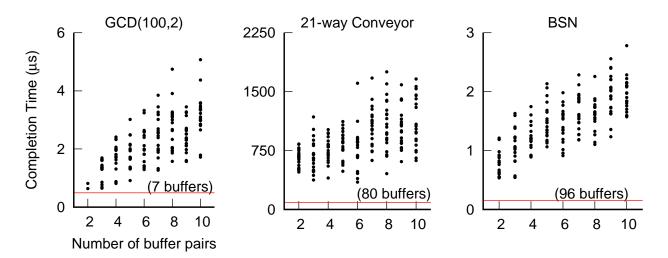

| 5.15 | Completion times under random buffer placement. Horizontal lines labeled with a buffer count indicate the completion time of the best manual design                        |     |

| 5.16 |                                                                                                                                                                            |     |

| 5.17 |                                                                                                                                                                            |     |

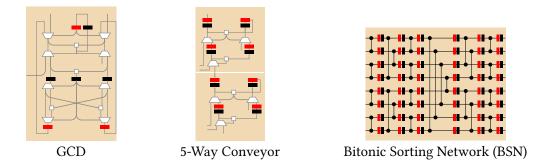

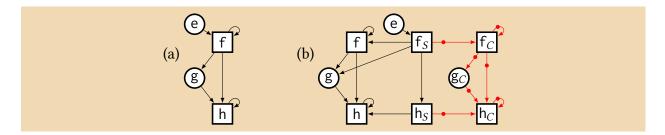

| 6.1  | (a) A divide-and-conquer function synthesized into a single block connected to a monolithic on-chip cache. (b) Our technique duplicates such functions and partitions      |     |

|      | the cache to enable task- and memory-level parallelism.                                                                                                                    | 115 |

- 6.2 A call graph (a) before and (b) after transformation. Divide-and-conquer (DAC) functions f and h are copied to form  $f_C$  and  $h_C$ ;  $f_S$  and  $h_S$  are additional versions that split the work between the originals and their copies. Non-DAC functions called from DAC functions are also copied ( $g_C$ ). "Copied" types flow along dotted red arrows. . . 117

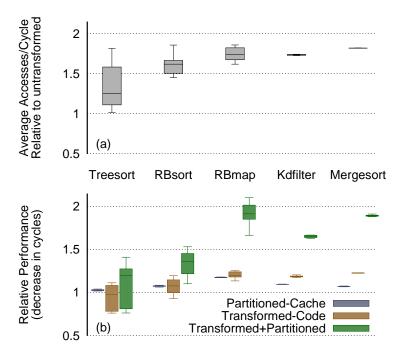

- 6.3 (a) Our code transformation consistently increases the number of memory accesses per cycle—a proxy for memory-level parallelism (oracle memory model). (b) Under the realistic memory model, cache partitioning and the code transformation each produce modest improvements; their combination is best because parallel tasks can exploit extra memory bandwidth.

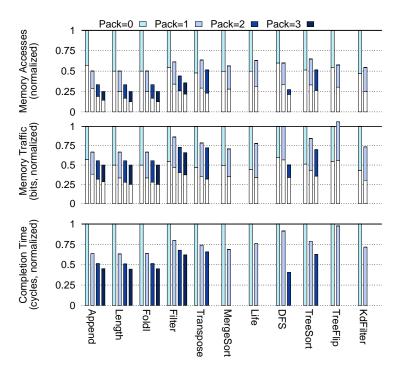

- 7.1 Performance under various degrees of packing (shorter is better): total number of memory accesses, total memory traffic in bits, and completion time in cycles. The numbers for each benchmark are normalized to its unpacked case (Table 7.1 lists base-lines). For accesses and traffic, solid bars denote reads; open bars are writes. . . . . 147

## List of Tables

| 5.1 | Comparing manually-coded RTL SystemVerilog with that generated from DF 112                                  |

|-----|-------------------------------------------------------------------------------------------------------------|

| 6.1 | Simulated Memory Parameters                                                                                 |

| 6.2 | Heap and Stack Partition Assignments for the Transformed & Partitioned Examples . 125                       |

| 7.1 | Baseline measurements for my benchmarks and area increases with packing factor.                             |

|     | Size is lines of code in Haskell source; Runtime is simulated execution time of the                         |

|     | circuit (in thousands of cycles); Traffic is the total amount of memory read and written                    |

|     | (in kilobytes); Area is the area (in adaptive logic modules for a Cyclone V FPGA). Area                     |

|     | <i>Increase</i> is the fractional increase under packing factors 1, 2, and 3 ( $2 \times$ is doubling). 146 |

## Acknowledgements

My path to a PhD (including writing this dissertation) was filled with bumps, forks with no signposts, and plenty of other obstacles that hindered any form of progress. The following individuals helped me find my way over the past 6 years, showing me how to smooth out the bumps, make decisions at each fork, and deal with the obstacles as they appeared.

I cannot thank Stephen A. Edwards enough for subverting every negative stereotype of a PhD advisor; I wouldn't have made it here without him. Things he didn't do: burden me with unnecessary work, research or administrative; force me to work certain hours/days to fit his schedule or expectations; ignore my attempts at regular communication. Things he did do: provide endless advice and guidance, both in my research and general academic decisions; support my research choices (in my later years, as he said he would) and passion for teaching; talk me out of every research slump I experienced.

I appreciate my co-advisor, Martha A. Kim, for her willingness to advise me and provide feedback as though I was one of her primary students. She guided me through much of the work for my first research paper submission (given that its subject was more in her field than Stephen's), helped design the experimental framework for all my papers, and heavily contributed to the aesthetic presentation of every chart, figure, and graph I have constructed.

I would like to thank the other faculty and staff at Columbia that made this dissertation possible. I thank Luca Carloni, Ronghui Gu, and David F. Bacon for agreeing to serve on my dissertation committee; particular thanks to Luca for also serving on the committees for my candidacy exam and thesis proposal defense. Jessica Rosa smoothed out the administrative burden that comes with managing a PhD career; I had no idea that distributing/defending/depositing a dissertation had so many moving parts, and would not have been able to navigate the process without her. Finally, I attribute much of my academic writing style to the inimitable Janet Kayfetz, whose Academic Writing course was a welcome change to my otherwise Computer Science-focused graduate career. I still reference her purple packet of wisdom regularly.

Three of my PhD peers deserve specific thanks. My desk neighbor, Emilio Cota, wrote and

defended his dissertation right before I started working on mine; he was always available to give insight into his process. Andrea Lottarini provided similar dissertation-based advice, and acted as a helpful sounding board for some of the key organizational decisions I made in this dissertation. Finally, Paolo Mantovani has been implicitly aiding me through the entire writing process: I usually had his dissertation in a saved Google Chrome tab, which I referenced weekly to validate my writing process. He also took the time to guide me through the use of hardware synthesis tools to obtain some of the experimental results in this dissertation.

Much thanks to Olin Shivers, whose excellent PhD dissertation served as an organizational template for mine (particularly the introduction and conclusions).

My time at Oberlin College (2009-2013) set me up for success as a graduate student. The Computer Science department filled me with the passion for this subject that got me to this point; much thanks to Ben Kuperman, Alexa Sharp, Tom Wexler, Cynthia Taylor, John Donaldson, Bob Geitz, and Richard Salter. Special thanks to Tom Reid, bowling guru and master of the mental game, who taught me mindfulness in a time when I needed it most.

I want to thank all the families that have supported me throughout the past six years. My barbershop families (Voices of Gotham, the Atlantic Harmony Brigade, and my quartet, Madhattan) helped develop leadership qualities that I used in my academic career, and provided stress outlets through singing and camaraderie. My Oberlin family has grown with me in the city for the past 6 years, and I appreciate everyone in the group for being there for me when things seemed academically darkest.

Finally, my family provided immeasurable emotional support; I would not have survived this experience without their love and advice. I particularly thank my mom, dad, and step-mom (Karen, John, and Suzy) for always being available to talk to me when I needed it.

### Chapter 1

## Introduction

## 1.1 My Thesis

Pure functional programs exhibiting irregular memory access patterns can be compiled into specialized hardware and optimized for parallelism.

A growing fraction of the area in modern chips is dedicated to application-specific hardware accelerators. These specialized cores consume less energy to perform a task than a general-purpose processor, and energy consumption is of critical, growing concern. To simplify their design, architects have turned to high-level synthesis (HLS) tools that produce circuits from high-level behavioral specifications. While these tools can produce efficient hardware for "regular" algorithms, they struggle with irregular algorithms that use recursion and dynamic pointer-based data structures like lists and trees.

One major issue with these HLS tools is their use of C-like languages as their source: the mutable memory model and side-effectful nature of these languages prevent standard HLS optimizations from exploiting parallelism in the face of irregularity (i.e., recursion and dynamically allocated memory). In this dissertation, I present an alternative HLS flow that uses a new compiler to synthesize hardware from pure functional programs. The compiler provides new optimizations that enable more parallelism in irregular programs and targets a specific model of computation, patient dataflow networks, that exploits this parallelism in hardware.

## **1.2** Structure of the Dissertation

This dissertation is organized as follows:

- The rest of this chapter provides background to motivate this dissertation and presents the contributions that support my thesis.<sup>1</sup>

- Chapter 2 surveys a selection of previous work related to these contributions.

- Next, Chapter 3 provides an introduction to functional languages (via a detailed presentation of our compiler's main intermediate representation), a high-level overview of our compiler, and the initial compiler passes that prepare a program for its translation into a dataflow network.

- I then dive into the translation from functional programs to hardware dataflow networks in Chapter 4 and present the novel compositional circuits that implement these networks in Chapter 5. Our networks' semantics are explained across these two chapters, both intuitively (Section 4.2) and formally (Section 5.1).

- The next two chapters describe our novel compiler optimizations. Chapter 6 covers how we optimize a specific class of irregular divide-and-conquer algorithms and presents the partitioned memory system our generated circuits use by default. Chapter 7 presents a "packing" algorithm that transforms recursive types (and the functions operating on them) at compile-time to improve the memory efficiency of our circuits.

- I conclude this dissertation in Chapter 8 with a summary of my work and some potential directions for future research.

<sup>&</sup>lt;sup>1</sup>Because this work is part of a larger project, I use first-person singular pronouns when describing this dissertation's organization and any experimental evaluation (I am the sole author of the dissertation and ran all the experiments myself); all other pronouns will be first-person plural. I mention others' specific contributions as they are presented in this dissertation.

## 1.3 High-Level Synthesis and Irregular Algorithms

In the mid-2000s, the landscape of computer architecture experienced a paradigm shift: while semiconductor manufacturers continued to pack more, smaller transistors onto chips (following Moore's Law [92]), it became increasingly difficult to switch them all simultaneously at their highest frequency without experiencing significant increases in power consumption (i.e., Dennard Scaling [38] broke down). In other words, current power constraints dictate that only a small fraction of transistors on a modern chip can be powered simultaneously, giving rise to a phenomenon known as *dark silicon* [14, 46].

Specialized hardware accelerators present a solution to this problem: accelerators are small (compared to general-purpose processors) application-specific circuits that have been carefully designed to execute a task (e.g., web search [105], machine learning [23], and database processing [136]) while providing higher performance and lower energy requirements than a generalpurpose processor [128]. Unfortunately, the traditional design process for accelerators makes them hard to adopt: architects must work at the register-transfer level (RTL) of abstraction, implementing high-level algorithms with low-level digital logic constructs like combinational gates and flip-flops. This leads to a tedious, error-prone process that precludes the rapid exploration of design trade-offs (e.g., between computing resources and memory) [4].

The high-level synthesis (HLS) design methodology is a promising alternative [32]: designers use high-level languages to describe their specifications, and a synthesis toolchain generates the RTL code that realizes these specifications in hardware. The majority of existing HLS tools synthesize hardware from C-like software specifications (Nane et al.'s survey [96] presents 33 HLS toolchains; 80% use a C-like input language), and have been shown to produce low-power, high-performing cores [88, 128]. HLS researchers tend to concern themselves with accelerating "regular" algorithms, i.e., computations with predictable memory access patterns. Prevalent HLS testsuites reflect this trend [65, 107]; the majority of benchmark programs provided in these testsuites use statically-sized arrays and matrices to structure data.

Modern HLS tools use loop-based optimizations and memory partitioning schemes to improve the performance of their synthesized accelerators. For example, given a simple array sum loop, an HLS tool could unroll the loop to reveal two array accesses per iteration, partition the array so its odd and even elements are stored in independent on-chip memories, and schedule the instructions to execute simultaneously or in a pipelined fashion (based on available resources). When the loop nests exhibit more convoluted access patterns or loop-carried dependencies, polyhedral analysis [25, 30, 31, 130] can guide code transformations that make the array accesses more amenable to pipelining and partitioning.

Irregular algorithms dealing with dynamically sized, pointer-based structures (e.g., lists, trees, or graphs) stymie these kinds of HLS optimizations. These algorithms appear in many settings and have the potential for parallelization [80], but their use of recursion and dynamic, datadependent memory operations render traditional HLS optimizations (e.g., polyhedral-based) ineffective or overly conservative. Commercial HLS tools like Xilinx's Vivado [138] prohibit dynamic memory allocation (which is necessary to implement truly dynamic data structures) for this very reason. New synthesis schemes and optimizations are thus required to synthesize these irregular algorithms in hardware.

Although others have recently suggested solutions to these issues [1, 36, 133, 142], they exacerbate the problem by using C-like languages as a specification: C's mutable memory model and direct control over pointers inhibits simple static analysis for memory-based optimizations, and the prevalence of side effects decreases opportunities for parallelization in general.

Pure functional languages are better suited for specifying irregular algorithms in this context. Functional languages in general provide higher-level abstractions (e.g., pattern matching, type inference, algebraic data types) that can improve designer productivity and simplify the correct specification of complex, irregular algorithms [54]. A "pure" language prohibits computations with side effects: an expression will always produce the same result when given the same arguments. Thus, compilers can freely reorder, modify, or parallelize more code in a pure functional language without modifying the underlying semantics [7, 59, 100, 101]. Purity also entails an immutable memory model (mutating a value in memory is a side effect) that admits specialized memory architectures and optimizations catered to irregular algorithms.

Pure functional languages thus have the potential to solve the problems faced by HLS systems handling irregular memory access patterns. This dissertation shows how to realize this potential.

## **1.4 Contributions**

To solve the irregular synthesis problem posed in the previous section, we have designed an optimizing compiler that synthesizes SystemVerilog (RTL) code from the pure functional language Haskell. This dissertation describes the compiler, which comprises the following research contributions (visualized in Figure 1.1):

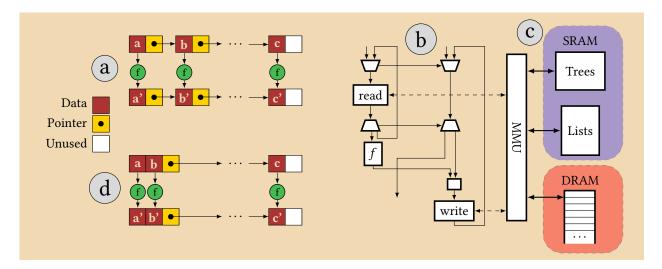

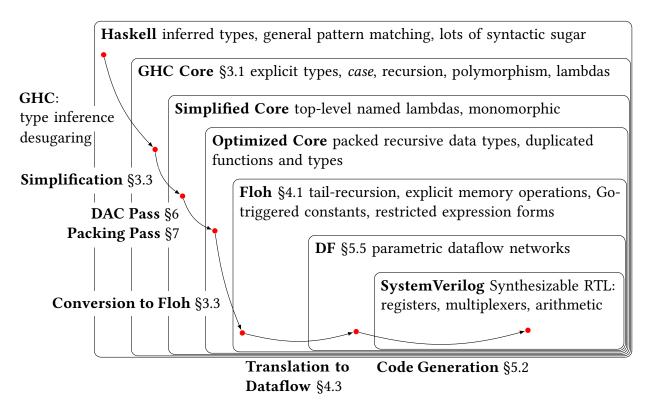

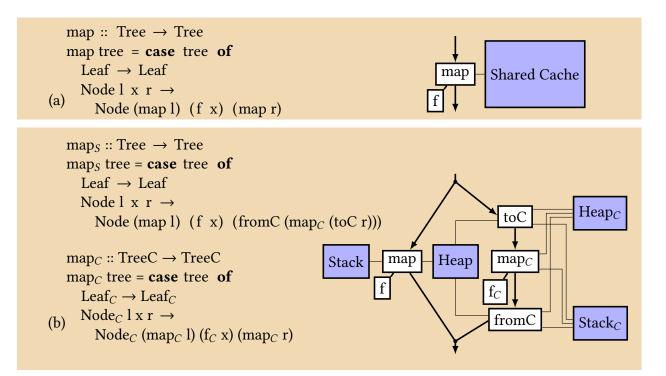

Figure 1.1: A visualization of the research supporting my thesis. I focus on synthesizing hardware from pure functional programs exhibiting irregular memory access patterns, e.g., the function *map* f l, which applies a function f to each element of a linked list l, storing the results in a new list (a). I translate these programs into modular, parallel dataflow networks in hardware (b), and apply two optimizations that exploit more parallelism in the synthesized circuits: the first improves memory-level parallelism in divide-and-conquer algorithms by combining a novel code transformation with a type-based memory partitioning scheme (c); the second packs more data into recursive types to improve spatial locality (i.e., data-level parallelism) and reduce an irregular program's memory footprint (d).

- Abstraction-lowering compiler passes. Our compiler takes in Haskell programs as its source. We use Haskell because its high-level abstractions and pure language model make it easy to correctly implement parallel algorithms operating on recursive data structures [85], e.g., a *map* function that applies a variable-latency operation *f* to each element of a dynamically-sized linked list to produce a new list (Figure 1.1a). To simplify their translation to hardware, we first transform these Haskell programs into a functional intermediate representation (IR) that prohibits constructs with no direct representation in hardware (e.g., recursion, recursively defined data types, anonymous functions). We perform this transformation with a number of abstraction-lowering compiler passes, including a novel algorithm for removing recursion (previously published in the 2015 CODES proceedings [141]) and a simple technique to introduce explicit pointers and memory operations.

- A translation from functional programs to patient dataflow networks. This contribution bridges the gap between software and hardware in our compiler. Given a program in our functional IR, we perform a (mostly) syntax-directed translation into abstract dataflow

#### CHAPTER 1. INTRODUCTION

networks (Figure 1.1b). These dataflow networks are inherently distributed, parallel, and "patient": they can handle long, unpredictable latencies from complex memory systems without any static scheduling or global controller. This property is ideal in our domain, since we target memory-bound irregular algorithms (instead of the more compute-bound scientific algorithms most HLS tools target). A novelty of our approach is how designers "ask for" pipeline parallelism through tail-recursion with *non-strict* functions: our recursive functions can begin execution immediately after their first argument arrives. When such a function calls itself tail-recursively, multiple invocations of the function run in parallel. This work has been published as part of the 2017 CC conference proceedings [125].

- **Compositional dataflow circuits.** After generating these abstract networks, we synthesize them into latency-insensitive [20] circuits that implement a restricted class of Kahn process (dataflow) networks [76]. These circuits may be connected to others with or without buffering, making it easy to consider a variety of designs. For example, buffer-free connections are fast but lead to combinational paths that limit clock speed; inserting buffers breaks long paths at the expense of latency. Our generated circuits retain the "patience" of Kahn's formalism through a valid/ready flow control protocol (i.e., backpressure); local handshaking eliminates any global controller (and thus long signal lines) and enables the insertion and removal of buffering. This accommodates blocks with dynamically varying latency (e.g., memory controllers) and makes it easy to adjust the number of pipeline stages, even in the presence of feedback. We have published work on these circuits in both the 2017 MEMOCODE conference proceedings [44] and a special volume of the TECS journal [43].

- A framework to accelerate irregular divide-and-conquer algorithms. We pair a compile-time code transformation with a type-based memory partitioning scheme to optimize recursive divide-and-conquer algorithms operating on recursive data structures. After finding functions that implement such algorithms in a source program, we duplicate the functions and split their input data structures in half ("divide") so each function copy may operate on its half in parallel ("conquer"). Each function becomes an independent circuit in hardware, exploiting task-level parallelism. To prevent a memory-induced bottleneck, we use the rich type information in our functional programs to allocate specific object types (e.g., lists, trees) to dedicated partitions of on-chip memory, and size each partition with a profiling-based heuristic (Figure 1.1c). To avoid local overflow, we back these on-chip partitions with larger, off-chip DRAM, and rely on a cache methodology to determine when to transfer data between on- and off-chip memories.

#### CHAPTER 1. INTRODUCTION

• An optimization for recursive data types. This optimization algorithm modifies the memory layout of recursive data types to reduce the number of high-latency trips to memory and increase data-level parallelism. Modern processors typically rely on caches for a similar purpose (and we use caches in our memory architecture), but the irregular memory access patterns associated with traversing recursive (i.e., pointer-based) structures inhibits the cache's ability to exploit spatial or temporal locality. Our algorithm thus packs recursive types such as lists and trees into cells that hold more data in an effort to improve spatial locality and data-level parallelism at compile-time (Figure 1.1d). This packing algorithm also reduces the total number of pointers in a recursive data structure, which can decrease the circuit's memory footprint and the number of trips made to memory (a common performance bottleneck in irregular algorithms).

The compiler has been implemented with both of the above optimizations included, and I have used it to generate hardware from various Haskell programs exhibiting irregular memory access patterns (due to their use of recursive data structures). This verifies the first part of my thesis: pure functional programs exhibiting irregular memory access patterns can be compiled into specialized hardware.

I have also run experiments that empirically validate the two optimizations described above; the results show that they can improve performance for a variety of Haskell programs realized in hardware. The first optimization exploits task- and memory-level parallelism, while the second exploits data-level parallelism. Taken together, these optimizations verify the second part of my thesis: hardware synthesized from irregular functional programs can be optimized for parallelism.

## Related Work

This chapter presents previous work that most closely relates to my thesis and contributions. I discuss the general problems motivating this dissertation, others' solutions to these problems, and how these solutions differ from or contribute to mine.

## 2.1 High-Level Synthesis

HLS relates to this work in that both raise the level of abstraction for hardware designers to promote rapid accelerator development and design-space exploration. A typical HLS flow starts with a designer specifying an algorithm in a C-like language; this specification may include hardwareaware constructs like clocks, ports, or timing constraints. The HLS tool analyzes the input program, applies standard compiler optimizations (e.g., common subexpression elimination, dead code removal), and transforms it into a control-flow graph: each node in the graph is an instruction or basic block, and edges indicate the flow of control between instructions (the graph may also include data-dependency information). The tool binds the instructions to hardware resources, and schedules when each instruction will be carried out by its assigned resource. Finally, it produces an RTL circuit specification that respects both the result of resource-binding and scheduling and any of the hardware designer's architectural constraints.

Here, I discuss how others have investigated alternative methods of hardware synthesis. Some use a functional input language to either provide higher-level abstractions to the designer or simplify the verification or optimization of the synthesized circuits. Others retain the imperative approach of typical HLS tools, but propose new hardware architectures to extend the reach of HLS past regular, loops-over-arrays algorithms. Our compiler combines both approaches: we use a functional input language to simplify the design process and reveal new compiler optimizations, and we target irregular algorithms to extend the scope of current HLS techniques.

#### 2.1.1 Functional HLS

Functional programming paradigms have appeared in hardware design research for decades; researchers long ago realized the strong connection between pure functions (those that always produce the same output for a given input) and synchronous digital circuits. These previous works sought to simplify circuit specification via functional constructs (e.g., higher-order functions, algebraic data types) while naturally capturing a circuit's structure and semantics.

Gammie's survey [54] covers much of the historical landscape, focusing on functional languages that take a *structural* approach to digital circuit description: functions represent gatelevel constructs (e.g., multiplexers, flip-flops) and operate on streams of data that capture values flowing on wires. Sheeran's  $\mu$ FP language [119] is often touted as the first of these functional hardware description language (HDLs); it leverages higher-order combinators to compose circuit primitives, and prescribes a set of algebraic laws that its specifications fulfill. Due to its focus on these combinators and lack of types,  $\mu$ FP is best for describing simple circuits with highly regular, repetitive structures.

Lava [13, 60, 61] is a family of *embedded* hardware description languages (EHDLs). These EHDLs are Haskell libraries that interpret pure functions as synchronous digital circuits. To capture a notion of time, Lava takes inspiration from the synchronous dataflow language Lustre [63] and provides a special *Signal* data type that defines an infinite sequence of values. Semantically, a *Signal* is a mapping from discrete, global clock cycles to values occurring on a physical vector of wires. Based on the library-defined types used by the programmer, executing a Lava program can either simulate the circuit on specified inputs, verify properties about the circuit, or generate an abstract syntax tree capturing the circuit's structure, which can then be analyzed or fed into other tools for more verification or RTL generation (e.g., to Verilog or VHDL).

Kuper's C $\lambda$ ash project [6, 7] is similar to Lava: it uses Haskell programs for structural circuit specification. However, C $\lambda$ ash has a subtle distinction that brings it closer to our work: instead of solely relying on Haskell's compiler for circuit generation (thus "embedding" the language), C $\lambda$ ash has a dedicated compiler that analyzes the language constructs comprising each Haskell function and synthesizes circuitry for those constructs. Functions thus do not require the special *Signal* type from Lava to be synthesized; a function without a *Signal* is synthesized into a combinational circuit, while the presence of the *Signal* type corresponds to sequential circuitry. While our compiler performs a similar syntax-directed translation to generate hardware, C $\lambda$ ash is still distinct in its use of structural hardware description and its lack of support for user-defined re-

cursive functions and data types (their online tutorial still specifies this restriction [5], although Raa's master's thesis [106] seems to remove it).

Bachrach et al. take a different tack with their Chisel HDL [8] by embedding it in Scala instead of Haskell. Chisel's types capture values flowing on wires (e.g., Bits, Bool, Fix for signed integers); a timing-aware type like Lava and  $C\lambda$ ash's *Signal* is not required, as Chisel programs include implicit clock and reset signals where necessary. Instead of Haskell's algebraic data types, Chisel provides an object-oriented model where users can extend base classes to represent collections of data, specific hardware interfaces (e.g., a FIFO input to a circuit), or hierarchical components (similar to Verilog's modules). Functions and classes may be polymorphic, and higher-order functions provide high-level abstractions to simplify the design process.

Unlike the structural approach taken by the above languages, we and others take a *behavioral* approach: designers specify the algorithmic behavior of a circuit (instead of its gate-level structure), and the compiler generates and optimizes the necessary logic to implement that behavior. For example, Kuga et al. [79] synthesize hardware from a subset of Haskell, focusing on the implementation of parallel design patterns like *map*, *zipWith*, and *reduce*. Unlike us, they do not specify whether they can handle recursion or arbitrary algebraic data types.

As a more notable example, the FLaSH compiler of Mycroft and Sharp [95, 117] synthesizes resource-aware hardware circuits from a simple functional language. While their original language (SAFL) was simpler than our compiler's intermediate representation, they later added "channel arguments" to functions to express communication between ports in hardware (SAFL+) [118] and a type-based approach for direct stream processing (SASL) [51, 50]. Their technique for sharing resources (i.e., functions called from multiple places) inspired ours; they place an arbiter at the entry to a shared function, remember which caller gained access, and finally route the result back to the caller. Furthermore, their most recent additions extended the compiler to admit function pipelining and synthesize dataflow networks, bringing them closer to our work. However, their compiler targets hardware with bounded storage requirements: no heaps or stacks are permitted in the synthesized circuits, so they cannot implement recursive data types. My thesis specifically concerns programs with recursive data types (since they elicit irregular memory access patterns); our compiler thus handles a larger class of programs.

The SHard compiler of Saint-Mleux et al. [111] compiles a functional language (Scheme) into a dataflow representation to produce custom hardware. They only implement strict functions: all arguments must arrive at a function before it can begin execution. Our compiler instead leverages a non-strict function policy to reduce execution time and improve throughput by exploiting

pipeline parallelism across function calls (see Section 4.1.1 for a specific example). Their treatment of memory is unusual: they only directly support function closures, so data structures such as lists must be coded as closures. Our language uses algebraic data types for data structures, providing a more intuitive approach for the hardware designer.

Bluespec [4] takes an alternative behavioral approach, but still draws inspiration from Haskell to provide a rich type system and inherent parallelism. Designers describe behavior with guarded atomic actions, which are then synthesized into globally scheduled combinational logic blocks. Conversely, our synthesized dataflow networks employ a flow control protocol that effectively acts as a distributed scheduler, eliminating the need for Bluespec's dedicated control logic.

Our translation of a functional language to dataflow networks was inspired by that of Arvind and Nikhil [3], but differs in two important ways. First, they generate dynamic dataflow graphs, i.e., loops and function calls are unrolled on-the-fly as their programs run. We choose a more challenging, higher performance target: physical networks, which means we have to build dataflow graphs with loops that explicitly arbitrate shared resources. Our solution will produce superior results because it avoids general-purpose overhead.

Second, their virtual approach (i.e., using a stored-program implementation) allows them to support unbounded buffers. While this does eliminate the danger of insufficient buffering, it requires the introduction of additional dataflow components to throttle loops and is impossible to implement directly in hardware. Our compiler targets physical hardware with finite buffers and provides a natural throttling mechanism in the form of a flow control protocol.

#### 2.1.2 Irregular HLS

My dissertation shows how to synthesize hardware for irregular algorithms implemented as functional programs; others have instead augmented imperative-based HLS tools to handle these kinds of algorithms. Specifically, four recent works have all proposed novel methods to exploit parallelism in hardware synthesized from irregular C programs (although their definitions of "irregularity" have slight differences). Each leverages the LLVM compiler framework to first translate the input C program into a standardized intermediate representation (IR), which they optimize to generate efficient specialized hardware. They all target loop-based programs and, due to the input language, must grapple with complications caused by a mutable memory model; our compiler instead deals with recursive programs that admit simpler program analysis due to our language's immutable memory model.

Like us, Josipovic et al. [75] describe a synthesis technique that realizes programs as latencyinsensitive dataflow networks. Their network building blocks are similar to ours, and they use the same handshaking protocol as us to implement latency-insensitivity. However, their translation process yields inherently sequential networks: their compiler partitions a program's instructions into sequential basic blocks, each basic block is individually translated into a dataflow subnetwork, and special dataflow components are inserted between these subnetworks to implement control flow. They also must correct for potentially out-of-order memory accesses, which can lead to data hazards under C's mutable memory model. Their solution is a complex load-store queue that must be carefully connected to the rest of the network to ensure functional correctness.

The Coarse-Grained Pipelined Accelerator (CGPA) framework of Liu et al. [84] synthesizes novel hardware architectures for C/C++ programs containing complex control flow or irregular memory access patterns. After translating the program to the LLVM IR, their HLS flow implements each loop's instructions with a multi-stage pipeline of hardware "workers" separated by FIFO buffers: sequential workers in one stage supply data to multiple parallel workers in the next, exploiting pipeline parallelism. The sequential workers typically implement irregular data structure traversal, while the parallel workers implement any independent instructions from multiple loop iterations; this decoupling tolerates variable latency (e.g., cache misses may slow down traversal, but the parallel workers can continue executing as long as they have input data in their FIFOs) and enables more parallelism (parallel workers operate independently). Their framework inserts additional LLVM primitives to aid in their analysis, and they impose instruction scheduling constraints to ensure the correctness of their synthesized pipelines. Our synthesized dataflow networks perform dynamic scheduling on their own (no static scheduling is required), and our input language is side-effect free, simplifying our translation to hardware.

Tan et al.'s ElasticFlow HLS tool [122] is similar to CGPA. Given a loop nest with a regular outer loop (i.e., it does not exhibit loop-carried dependencies) and at least one dynamic-bound inner loop, they synthesize a multi-stage pipeline where each inner loop becomes a "loop processing array" (LPA), and all other operations in the loop nest are synthesized into traditional, fixed-latency pipeline stages; the stages are then connected via FIFOs. The LPA architecture is their main contribution: it contains multiple loop processing units (LPUs) that can each execute an inner loop to completion (instead of just some of its instructions), a distributor that dispatches inner loop results are passed to the next pipeline stage in-order with the help of a reorder buffer (ROB). They use an integer linear programming technique to determine the number of LPUs for

a given LPA and the size of each LPA's ROB, maximizing the dynamic throughput of the LPUs under a given hardware area constraint. They improve upon CGPA by handling out-of-order execution for entire loop nests (as opposed to just individual instructions) and achieving higher resource efficiency with special LPUs that can implement one of many inner loop nests.

Zhao et al. [142] present a similar C++-based HLS architectural template, but they specifically focus on decoupling complex data structures (e.g., priority queues and trees) from the algorithms that use them. In their work, a data structure is *complex* if any of its functions exhibit long or variable latency and contain variable-bound loops or memory dependencies. Their templates have four components (like those in ElasticFlow's LPAs), which communicate via latency-insensitive handshaking (like our dataflow networks): mutator function units and accessor function units implement the data structures' mutator and accessor functions; a dispatcher receives function calls from the algorithm and passes them off to the appropriate function units, respecting function dependencies; and a collector receives results from the function units, but mutator functions cannot be overlapped with any other since they may modify memory. We rely on an immutable memory model in our work to avoid this restriction; if two writes of different type are available (e.g., writing a tree cell vs. a list cell), we can service them in parallel.

### 2.2 Hardware Dataflow Networks

Our compiler translates Haskell programs into latency-insensitive dataflow networks in hardware. Dataflow networks are a natural model for parallel, distributed computation: processes in a network (called "actors") execute in parallel and communicate via sequences of tokens passed over unbounded channels. These networks are well-suited to specifying complex hardware designs because of their "patience": process speed has no effect on network function. While the underlying formalism of these networks is well-defined [39, 76, 81, 82], different approaches have been taken to realize these networks in physical hardware.

Tripakis et al. [126] survey a number of these dataflow-to-hardware projects; most focus on statically schedulable models such as SDF that do not support data-dependent actors, e.g., multiplexers and demultiplexers. Carloni et al. and Carmona et al. champion patient dataflow networks following this model with their respective Latency-Insensitive Design [19, 20] and Elastic Circuits projects [21]. Both of these works implement the patience of the abstract dataflow model

with a handshaking protocol. Possignolo et al. [104] also consider token/handshaking pipelines for processor design: they start with a synchronous circuit with no handshaking and transform it into a patient dataflow network by introducing four actor circuits (unit-rate, fork, demultiplexer, and merge) based on designer annotations. Although their fork and merge actors can induce deadlock in general (a danger in any dataflow design), they provide a set of design rules that prevent deadlock. They use Colored Petri Nets to model throughput, an augmented form of the model Collins and Carloni used to analyze and optimize their latency-insensitive systems [27].

While many handshaking protocols exist to implement latency-insensitivity, one of the most common ones uses a *valid* bit to indicate that a process is sending a token downstream, and a *ready* bit to indicate that the downstream process can consume that token. This 2-bit protocol is standard in asynchronous systems [115]. Intel's 8008 used a similar protocol in 1972 to wait for slow memory [70], but the protocol likely appeared even earlier. We use this protocol in our networks, specifically taking inspiration from Li et al. [83], but the same system can be found in Cortadella et al. [34, 35], Dimitrakopoulos et al. [40], ARM's AXI4-stream protocol [2], and the FIFOs provided in Altera and Xilinx FPGAs (Field-Programmable Gate Arrays).

Careful implementation of this handshaking protocol is required to prevent combinational cycles, e.g., due to a *valid* bit depending on a *ready* bit and vice versa. ForSyDe [86, 112, 113] avoids these handshaking-induced combinational cycles by always inserting delays on channels. These channels are not user-visible: their system presents the user with a synchronous model of computation (i.e., unit-rate dataflow with no decisions). This makes it difficult for a user to specify variable-rate processes in ForSyDe. Our networks rely on a special pair of buffers and a three-phase evaluation order (data, then *valid*, then *ready*) to prevent combinational cycles, yielding faster designs than the fully-buffered networks of ForSyDe.

The above works apply latency-insensitive design practices to existing hardware systems; others are closer to our work in their use of patient dataflow networks as targets for high-level synthesis. Keinert et al.'s [78] SystemCoDesigner employs behavioral synthesis (Forte's Cynthesizer product) to synthesize hardware for coarse-grained dataflow actors expressed in SystemC with the SysteMoC library [47]. Inter-actor communication is done through FIFOs taken from a library [67]. Janneck et al. synthesize networks from Cal [45]: a rich, functional-inspired language for expressing dataflow process actors and networks. They have a hardware synthesis system for these networks [12, 71, 72], although little has been published about its internals. Thavot et al. [123] instead synthesize hybrid hardware/software systems from Cal; they are unique in that all of their actors are nondeterministic, going against the typical desire to retain determinism

across all dataflow actors and the network itself.

Our dataflow networks depart from each of the aforementioned works. We provide datadependent actors that can make choices, which cannot be modeled in the typical SDF framework, and include a single nondeterministic actor to share resources and help implement recursion in hardware. Our actors are fairly lightweight due to our use of latency-insensitive buffers, making simple actors like adders and multiplexers practical. Finally, our actors are compositional: each actor becomes a circuit that may be connected to others with or without buffering, and combinational cycles arise only from a completely unbuffered cycle. We formalize our networks, present our actor implementations, and argue for their correctness in Chapter 5.

## 2.3 Parallelizing Divide-and-Conquer Algorithms

Divide-and-conquer ("DAC") algorithms are intuitively simple to parallelize: after breaking down a task into distinct subtasks, execute the subtasks in parallel before merging the final result. Depending on the implementation of the algorithm, though, it can be difficult for a compiler to automatically find and enable this parallelism. Much work has been done to solve this issue, mostly in purely software-facing frameworks, although a few others have specifically leveraged specialized hardware to parallelize DAC algorithms. Here, I first list some of the techniques the software community has devised; then, I discuss how previous work on memory partitioning can be applied to DAC parallelization, even if that was not the main motivation for the work; finally, I present how others have parallelized DAC algorithms with the help of specialized hardware, which most closely resembles the work I present in Chapter 6.

### 2.3.1 Software Techniques

Many software techniques rely on the use of specialized language constructs to find and exploit DAC parallelism. Language extensions like Cilk [53] (C++), Satin [127] (Java), and Tapir [114] (LLVM) add extra primitives to express "fork-join" parallelism: *spawn* indicates that a function call can operate in parallel with surrounding statements (or be assigned to a dedicated core), while *sync* specifies where execution must stall in a given function until all spawned processes have terminated. Multiple recursive calls in a DAC function can use *spawn* to execute in parallel, and *sync* can merge their results. Morita et al. [94] take a significantly different tack: they parallelize DAC algorithms on lists, but only if the algorithm is expressed with a pair of sequential functions

that perform computation by scanning the list leftwards and rightwards. Their programs are written in a restricted language that forces the user to express DAC functions with this list-scanning paradigm, from which they generate parallel C++ code to run on a distributed system. Collins et al. [28] also generate parallel C code for DAC algorithms. Their Huckleberry tool takes in DAC functions written with a special API, and produces code that distributes data for independent subtasks across multiple cores.

Other software techniques *automatically* parallelize DAC functions by relying on the compiler to find subtasks that may safely execute in parallel. For example, both Gupta et al. [62] and Rugina and Rinard [109] focus on automatically parallelizing recursive DAC algorithms in C programs. As a result of C's mutable memory model, both of these works rely on complex pointer analysis and other data-dependence compiler algorithms to verify that no two subtasks of a DAC function ever write or read the same section of an array simultaneously. Otherwise, if the subtasks were executed simultaneously, a data race could occur and break the program's functionality.

Our technique deviates from these works in two ways. First, it eschews special language constructs to find DAC parallelism; it instead finds this parallelism by analyzing the structures of general Haskell programs. Second, our compiler's immutable memory model prohibits the overwriting of any live data; we can exploit more parallelism than Gupta et al. or Rugina and Rinard by copying shared data to different memory partitions without fear of races.

#### 2.3.2 Memory Partitioning

In general, the HLS community has focused less on DAC function parallelization specifically, and more on how to partition on-chip memory so multiple segments of a (typically staticallysized) data structure can be accessed in parallel. Such on-chip memory partitioning can exploit memory-level parallelism in DAC functions; I discuss some notable work on this subject here.

Most of the previous work on memory partitioning in HLS frameworks has focused on accelerating highly regular, loops-over-arrays programs [25, 29, 31, 90, 130]. If a loop nest accesses an array and does not exhibit loop-carried dependencies, then the loop may be unrolled to reveal more independent accesses per iteration and enable instruction-level parallelism. The memory system exploits this parallelism with banking: the array is distributed across multiple memory banks such that the multiple elements accessed on a given iteration reside in separate banks; this leverages the high memory bandwidth provided by modern FPGAs. If there are datadependencies in the original loop nest, various linear algebraic transformations may be applied

to restructure the array's access pattern into a form that is more amenable to memory banking. These techniques rely on the array residing in contiguous memory and a highly regular access pattern; my dissertation specifically targets programs operating on dynamic data structures that may be distributed throughout the address space and accessed in an irregular fashion.

Others have applied memory partitioning to programs with less regular access patterns. Zhou et al. [143] use a trace-driven technique to exploit memory-level parallelism in loops with nonaffine access patterns, i.e., the addresses used to access the array are not affine functions of the loop's iteration variable. Instead of performing static analysis and applying linear algebraic transformations to loops over arrays, they instrument the program to obtain a memory access trace and use important address bits in the trace to guide their banking and array segmentation. Ben-Asher and Rotem [11] present a similar trace-based method that applies to both array and dynamic data structure accesses. For the dynamic data structures, they rely on the assumption that the structures are created with custom memory allocators that always place the data structures at consistent, structure-aligned addresses. This lets them treat any data structure as an array of C structs, simplifying their partitioning algorithm. In our partitioning scheme, we make no assumptions on addresses of the dynamic data structures generated by the input program.

#### 2.3.3 HLS for Divide-and-Conquer

Four specific prior works are closest to ours; they parallelize DAC functions either with specialized hardware support or as part of a full HLS toolchain. Luk et al. [87] parallelize DAC functions with a software/hardware co-design technique: a CPU divides input data into partitions, the partitions are passed to an FPGA-based accelerator that "conquers" the data with a homogeneous network of tightly-coupled functional units, and the results are passed back to the CPU for merging. They use a functional language to present their strategy. Our work is completely hardware based (i.e., our synthesized hardware does not communicate with a general-purpose processor), and we use loosely-coupled, heterogeneous dataflow networks to perform parallel computation.