# Design of Embedded Systems: Formal Models, Validation, and Synthesis

Stephen Edwards, Luciano Lavagno, Edward A. Lee, and Alberto Sangiovanni-Vincentelli

Abstract—This paper addresses the design of reactive real-time embedded systems. Such systems are often heterogeneous in implementation technologies and design styles, for example by combining hardware ASICs with embedded software. The concurrent design process for such embedded systems involves solving the specification, validation, and synthesis problems. We review the variety of approaches to these problems that have been taken.

#### I. INTRODUCTION

Reactive real-time embedded systems are pervasive in the electronics system industry. Applications include vehicle control, consumer electronics, communication systems, remote sensing, and household appliances. In such applications, specifications may change continuously, and time-to-market strongly affects success. This calls for the use of software programmable components with behavior that can be fairly easily changed. Such systems, which use a computer to perform a specific function, but are neither used nor perceived as a computer, are generically known as embedded systems. More specifically, we are interested in reactive embedded systems. Reactive systems are those that react continuously to their environment at the speed of the environment. They can be contrasted with interactive systems, which react with the environment at their own speed, and transformational systems, which take a body of input data and transform it into a body of output data [1].

A large percentage of the world-wide market for microprocessors is filled by micro-controllers that are the programmable core of embedded systems. In addition to microcontrollers, embedded systems may consist of ASICs and/or field programmable gate arrays as well as other programmable computing units such as Digital Signal Processors (DSPs). Since embedded systems interact continuously with an environment that is analog in nature, there must typically be components that perform A/D and D/A conversions. A significant part of the design problem consists of deciding the software and hardware architecture for the system, as well as deciding which parts should be implemented in software running on the programmable components and which should be implemented in more specialized hardware.

Embedded systems often are used in life critical situations, where reliability and safety are more important criteria than performance. Today, embedded systems are designed with an ad hoc approach that is heavily based on earlier experience with similar products and on manual design. Use of higher level languages such as C helps somewhat, but with increasing complexity, it is not sufficient. Formal verification and automatic synthesis of implementations are the surest ways to guarantee safety. However, both formal verification and synthesis from high levels of abstraction have been demonstrated only for small, specialized languages with restricted semantics. This is at odds with the complexity and heterogeneity found in typical embedded systems.

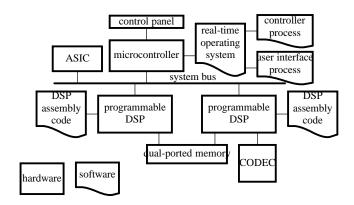

Fig. 1. A typical reactive real-time embedded system architecture.

We believe that the design approach should be based on the use of one or more formal models to describe the behavior of the system at a high level of abstraction, before a decision on its decomposition into hardware and software components is taken. The final implementation of the system should be made as much as possible using automatic synthesis from this high level of abstraction to ensure implementations that are "correct by construction." Validation (through simulation or verification) should be done as much as possible at the higher levels of abstraction.

A typical hardware architecture for an embedded system is illustrated in Figure 1. This type of architecture combines custom hardware with embedded software, lending a certain measure of complexity and heterogeneity to the design. Even within the software or hardware portions themselves, however, there is often heterogeneity. In software, control-oriented processes might be mixed under the supervision of a multitasking realtime kernel running on a microcontroller. In addition, hard-realtime tasks may run cooperatively on one or more programmable DSPs. The design styles used for these two software subsystems are likely to be quite different from one another, and testing the interaction between them is unlikely to be trivial.

The hardware side of the design will frequently contain one or more ASICs, perhaps designed using logic or behavioral synthesis tools. On the other hand, a significant part of the hardware design most likely consists of interconnections of commodity components, such as processors and memories. Again, this time on the hardware side, we find heterogeneity. The design styles used to specify and simulate the ASICs and the interconnected commodity components are likely to be quite different. A typical system, therefore, not only mixes hardware design with software design, but also mixes design styles within each of these categories.

Most often the set of tasks that the system implements are not specified in a rigorous and unambiguous fashion, so the design process requires several iterations to obtain convergence. Moreover, during the design process, the level of abstraction, detail, and specificity in different parts of the design varies. To complicate matters further, the skill sets and design styles used by different engineers on the project are likely to be different. The net result is that during the design process, many different specification and modeling techniques will be used.

Managing the design complexity and heterogeneity is the key problem. We believe that the use of formal models and highlevel synthesis for ensuring safe and correct designs depends on understanding the interaction between diverse formal models. Only then can the simplicity of modeling required by verification and synthesis be reconciled with the complexity and heterogeneity of real-world design.

The concurrent design process for mixed hardware/software embedded systems involves solving the following subproblems: specification, validation, and synthesis. Although these problems cannot be entirely separated, we deal with them below in three successive sections.

# II. SPECIFICATION AND MODELING

The design process is often viewed as a sequence of steps that transforms a set of specifications described informally into a detailed specification that can be used for manufacturing. All the intermediate steps are characterized by a transformation from a more abstract description to a more detailed one.

A designer can perform one or more steps in this process. For the designer, the "input" description is a *specification*, the final description of the design is an *implementation*. For example, a software designer may see a set of routines written in C as an implementation of her/his design even though several other steps may be taken before the design is ready for manufacturing. During this process, verification of the quality of the design with respect to the demands placed on its performance and functionality has to be carried out. Unfortunately, the descriptions of the design at its various stages are often informal and not logically connected by a set of precise relationships.

We advocate a design process that is based on representations with precise mathematical meaning so that both the verification and the map from the initial description to the various intermediate steps can be carried out with tools of guaranteed performance. Such an approach is standard in certain communities, where languages with strong formal properties are used to ensure robust design. Examples include ML [2], dataflow languages (e.g. Lucid [3], Haskell [4]) and synchronous languages (e.g., Lustre, Signal, Esterel [5]).

There is a broad range of potential formalizations of a design, but most tools and designers describe the behavior of a design as a relation between a set of inputs and a set of outputs. This relation may be informal, even expressed in natural language. It is easy to find examples where informal specifications resulted in unnecessary redesigns. In our opinion, a *formal model of a design* should consist of the following components:

1. A *functional specification*, given as a set of explicit or implicit relations which involve inputs, outputs and possibly internal (state) information.<sup>1</sup>

- 2. A *set of properties* that the design must satisfy, given as a set of relations over inputs, outputs, and states, that can be checked against the functional specification.

- 3. A *set of performance indices* that evaluate the quality of the design in terms of cost, reliability, speed, size, etc., given as a set of equations involving, among other things, inputs and outputs.

- 4. A *set of constraints* on performance indices, specified as a set of inequalities.

The functional specification fully characterizes the operation of a system, while the performance constraints bound the cost (in a broad sense). The set of properties is redundant, in that in a properly constructed design, the functional specification satisfies these properties. However, the properties are listed separately because they are simpler and more abstract (and also incomplete) compared to the functional specification. A property is an assertion about the behavior, rather than a description of the behavior. It is an abstraction of the behavior along a particular axis. For example, when designing a network protocol, we may require that the design never deadlock (this is also called a liveness property). Note that liveness does not completely specify the behavior of the protocol; it is instead a property we require our protocol to have. For the same protocol, we may require that any request will eventually be satisfied (this is also called fairness). Again this does not completely specify the behavior of the protocol but it is a required property.

Given a formal model of the functional specifications and of the properties, we can classify properties in three groups:

- 1. Properties that are *inherent* in the model of computation (i.e., they can be shown formally to hold for all specifications described using that model).

- 2. Properties that can be verified *syntactically* for a given specification (i.e., they can be shown to hold with a simple, usually polynomial-time, analysis of the specification).

- 3. Properties that must be verified *semantically* for a given specification (i.e., they can be shown to hold by executing, at least implicitly, the specification for all inputs that can occur).

For example, consider the property of *determinate behavior*, i.e., the fact that the output of a system depends only on its inputs and not on some internal, hidden choice. Any design described by a dataflow network (a formal model to be described later) is determinate, and hence this property need not be checked. If the design is represented by a network of FSMs, determinacy can be assessed by inspection of the state transition function. In some discrete event models (for example those embodied in Verilog and VHDL) determinacy is difficult to prove: it must be checked by exhaustive simulation.

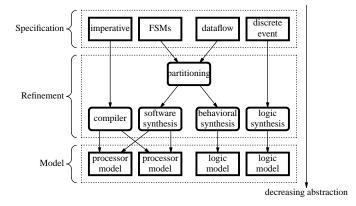

The design process takes a model of the design at a level of abstraction and *refines* it to a lower one. In doing so, the designer must ensure that the properties at that level of abstraction are verified, that the constraints are satisfied, and that the performance indices are satisfactory. The refinement process involves also mapping constraints, performance indices and properties to the lower level so that they can be computed for the next level down.<sup>2</sup> Figure 2 shows a key refinement stage in embedded system design. The more abstract specification in this case is an

<sup>&</sup>lt;sup>1</sup>We will define later on what we mean exactly by inputs, outputs and state information. For now, consider them as sequences of values.

<sup>&</sup>lt;sup>2</sup>The refinement process can be defined formally once the models of the design are formally specified, see McMillan [6].

Fig. 2. An example of a design refinement stage, which uses hardware and software synthesis to translate a functional specification into a model of hardware.

executable functional model that is closer to the problem level. The specification undergoes a synthesis process (which may be partly manual) that generates a model of an implementation in hardware. That model itself may still be fairly abstract, capturing for example only timing properties. In this example the model is presumably used for hardware/software partitioning.

While figure 2 suggests a purely top-down process, any real design needs more interaction between specification and implementation. Nonetheless, when a design is complete, the best way to present and document it is top down. This is enough to require that the methodology support top-down design.

### A. Elements of a Model of Computation

A *language* is a set of symbols, rules for combining them (its *syntax*), and rules for interpreting combinations of symbols (its *semantics*). Two approaches to semantics have evolved, *denota-tional* and *operational*. A language can have both (ideally they are consistent with one another, although in practice this can be difficult to achieve). Operational semantics, which dates back to Turing machines, gives meaning of a language in terms of actions taken by some abstract machine, and is typically closer to the implementation. Denotational semantics, first developed by Scott and Strachey [7], gives the meaning of the language in terms of relations.

How the abstract machine in an operational semantics can behave is a feature of what we call the *model of computation* underlying the language. The kinds of relations that are possible in a denotational semantics is also a feature of the model of computation. Other features include communication style, how individual behavior is aggregated to make more complex compositions, and how hierarchy abstracts such compositions.

A design (at all levels of the abstraction hierarchy from functional specification to final implementation) is generally represented as a set of components, which can be considered as isolated monolithic blocks, interacting with each other and with an environment that is not part of the design. The model of computation defines the behavior and interaction of these blocks.

In the sections that follow, we present a framework for comparing elements of different models of computation, called the tagged-signal model, and use it to contrast different styles of sequential behavior, concurrency, and communication. We will give precise definitions for a number of terms, but these definitions will inevitably conflict with standard usage in some communities. We have discovered that, short of abandoning the use of most common terms, no terminology can be consistent with standard usage in all related communities. Thus we attempt to avoid confusion by being precise, even at the risk of being pedantic.

### A.1 The Tagged-Signal Model

Two of the authors (Lee and Sangiovanni-Vincentelli) have proposed the tagged-signal model [8], a formalism for describing aspects of models of computation for embedded system specification. It is denotational in the Scott and Strachey [7] sense, and it defines a semantic framework (of signals and processes) within which models of computation can be studied and compared. It is very abstract—describing a particular model of computation involves imposing further constraints that make it more concrete.

The fundamental entity in the Tagged-Signal Model is an event—a value/tag pair. Tags are often used to denote temporal behavior. A set of events (an abstract aggregation) is a signal. Processes are relations on signals, expressed as sets of n-tuples of signals. A particular model of computation is distinguished by the order it imposes on tags and the character of processes in the model.

Given a set of *values* V and a set of *tags* T, an *event* is a member of  $T \times V$ , i.e., an event has a tag and a value. A *signal* s is a set of events. A signal can be viewed as a subset of  $T \times V$ . A *functional signal* is a (possibly partial) function from T to V. The set of all signals is denoted S. A *tuple* of n signals is denoted s, and the set of all such tuples is denoted  $S^n$ .

The different models of time that have been used to model embedded systems can be translated into different order relations on the set of tags T in the tagged signal model. In particular, in a *timed system* T is totally ordered, i.e., there is a binary relation < on members of T such that if  $t_1, t_2 \in T$  and  $t_1 \neq t_2$ , then either  $t_1 < t_2$  or  $t_2 < t_1$ . In an *untimed system*, T is only partially ordered.

A process P with n signals is a subset of the set of all n-tuples of signals,  $S^n$  for some n. A particular  $s \in S^n$  is said to satisfy the process if  $s \in P$ . An s that satisfies a process is called a *behavior* of the process. Thus a *process* is a set of possible *behaviors*, or a relation between signals.

For many (but not all) applications, it is natural to partition the signals associated with a process into *inputs* and *outputs*. Intuitively, the process does not determine the values of the inputs, and does determine the values of the outputs. If n = i + o, then  $(S^i, S^o)$  is a partition of  $S^n$ . A process with *i* inputs and *o* outputs is a subset of  $S^i \times S^o$ . In other words, a process defines a *relation* between input signals and output signals. A (i + o)tuple  $\mathbf{s} \in S^{i+o}$  is said to *satisfy* P if  $\mathbf{s} \in P$ . It can be written  $\mathbf{s} = (\mathbf{s}_1, \mathbf{s}_2)$ , where  $\mathbf{s}_1 \in S^i$  is an *i*-tuple of *input signals* for process P and  $\mathbf{s}_2 \in S^o$  is an *o*-tuple of *output signals* for process P. If the input signals are given by  $\mathbf{s}_1 \in S^i$ , then the set  $I = \{(\mathbf{s}_1, \mathbf{s}_2) \mid \mathbf{s}_2 \in S^o\}$  describes the inputs, and  $I \cap P$  is the set of behaviors consistent with the input  $\mathbf{s}_1$ .

A process F is *functional* with respect to a partition if it is a single-valued, possibly partial, mapping from  $S^i$  to  $S^o$ . That is, if  $(\mathbf{s}_1, \mathbf{s}_2) \in F$  and  $(\mathbf{s}_1, \mathbf{s}_3) \in F$ , then  $\mathbf{s}_2 = \mathbf{s}_3$ . In this case,

we can write  $\mathbf{s}_2 = F(\mathbf{s}_1)$ , where  $F : S^i \to S^o$  is a (possibly partial) function. Given the input signals, the output signals are determined (or there is unambiguously no behavior).

Consider, as a motivating example introducing these several mechanisms to denote temporal behavior, the problem of modeling a time-invariant dynamical system on a computer. The underlying mathematical model, a set of differential equations over continuous time, is not directly implementable on a digital computer, due to the double quantization of real numbers into finite bit strings, and of time into clock cycles. Hence a first translation is required, by means of an *integration rule*, from the differential equations to a set of *difference equations*, that are used to compute the values of each signal with a given tag from the values of some other signals with previous and/or current tags.

If it is possible to identify several strongly connected components in the dependency graph<sup>3</sup>, then the system is *decoupled*. It becomes then possible to go from the total order of tags implicit in physical time to a *partial order* imposed by the depth-first ordering of the components. This partial ordering gives us some freedom in implementing the integration rule on a computer. We could, for example, play with scheduling by embedding the partial order into the total order among clock cycles. It is often convenient, for example, to evaluate a component completely, for all tags, before evaluating components that depend on it. Or it is possible to spread the computation among multiple processors.

In the end, time comes back into the picture, but the *double mapping*, from total to partial order, and back to total order again, is essential to

- 1. *prove properties* about the implementation (e.g., stability of the integration method, a bound on the maximum execution time, ...),

- 2. *optimize* the implementation with respect to a given cost function (e.g., size of the buffers required to hold intermediate signals versus execution time, satisfaction of a constraint on the maximum execution time, ...),

## A.2 State

Most models of computation include components with state, where behavior is given as a sequence of state transitions. In order to formalize this notion, let us consider a process F that is functional with respect to partition  $(S^i, S^o)$ . Let us assume for the moment that F belongs to a timed system, in which tags are totally ordered. Then for any tuple of signals s, we can define  $s_{>t}$  to be a tuple of the (possibly empty) subset of the events in s with tags greater than t.

Two input signal tuples  $\mathbf{r}, \mathbf{s} \in S^i$  are in relation  $E_t^F$  (denoted  $(r^i, s^i) \in E_t^F$ ) if  $\mathbf{r}_{>t} = \mathbf{s}_{>t}$  implies  $F(\mathbf{r})_{>t} = F(\mathbf{s})_{>t}$ . This definition intuitively means that process F cannot distinguish between the "histories" of  $\mathbf{r}$  and  $\mathbf{s}$  prior to time t. Thus, if the inputs are identical after time t, then the outputs will also be identical.

$E_t^F$  is an equivalence relation, partitioning the set of input signal tuples into equivalence classes for each t. Following a long tradition, we call these equivalence classes the *states* of F. In the hardware community, components with only one state for

each t are called *combinational*, while components with more than one state for some t are called *sequential*. Note however that the term "sequential" is used in very different ways in other communities.

## A.3 Decidability

Components with a *finite* number of states differ significantly from those with an *infinite* number of states. For certain infinitestate models (those that are Turing-complete), many desirable properties are undecidable—they cannot be determined in a finite amount of time for all systems. These properties include whether a system will need more memory than is available, whether a system will halt, and how fast a system will run. Hopcroft and Ullman [9] discuss these issues at length.

Undecidability is not an insurmountable barrier, and decidability is not sufficient to answer all questions in practice (e.g., because the required run-time may be prohibitive). Many successful systems have been designed using undecidable languages (i.e., those in which questions about some programs are undecidable). Although no algorithm can solve an undecidable problem for *all* systems, algorithms exist that can solve them for *most* systems. Buck's Boolean Dataflow scheduler [10], for example, can answer the halting and bounded memory problems for many systems specified in a Turing-complete dataflow model, although it does, necessarily, fail to reach a conclusion for some systems.

The non-terminating nature of embedded systems opens the possibility of using infinite time to solve certain undecidable problems. Parks' [11] scheduler, for example, will execute a potentially infinite-state system forever in bounded memory *if it is possible to do so*. However, it does not answer the question of how much memory is needed or whether the program will eventually halt.

The classical von Neumann model of computation<sup>4</sup> is a familiar model of sequential behavior. A memory stores the state and a processor advances the state through a sequence of memory operations. Most commonly-used programming languages (e.g., C, C++, Lisp, Pascal, FORTRAN) use this model of computation. Often, the memory is viewed as having an unbounded number of finite-valued words, which, when coupled with an appropriate choice of processor instructions, makes the model Turing complete<sup>5</sup>. Modern computer systems make this model practical by simulating unbounded memory with an elaborate hierarchy (registers, cache, RAM, hard disk). Few embedded systems, however, can currently afford such a scheme.

#### A.4 Concurrency and Communication

While sequential or combinational behavior is related to individual processes, embedded systems will typically contain several coordinated concurrent processes. At the very least, such systems interact with an environment that evolves independently, at its own speed. But it is also common to partition the overall model into tasks that also evolve more or less independently, occasionally (or frequently) interacting with one another.

$<sup>^{3}</sup>$ A directed graph with a node for each signal, and an edge between two signals whenever the equation for the latter depends on the former.

<sup>&</sup>lt;sup>4</sup>It is formalized in the abstract model called random access machine or random access stored program [12].

<sup>&</sup>lt;sup>5</sup>Turing-completeness can be obtained also with a finite number of infinitevalued words.

Communication between processes can be *explicit* or *implicit*. In explicit communication, a *sender* process informs one or more *receiver* processes about some part of its state. In implicit communication, two or more processes share a common notion of state.

Time plays a larger role in embedded systems than in classical computation. In classical transformational systems, the correct result is the primary concern—when it arrives is less important (although *whether* it arrives, the termination question, *is* important). By contrast, embedded systems are usually real-time systems, where the time at which a computation takes place can be more important than the computation itself.

As we discussed above, different models of time become different order relations on the set of tags T in the tagged signal model. Recall that in a *timed system* T is totally ordered, while in an *untimed system* T is only partially ordered. Implicit communication generally requires totally ordered tags, usually identified with physical time.

The tags in a *metric-time system* have the notion of a "distance" between them, much like physical time. Formally, there exists a partial function  $d : T \times T \rightarrow \mathbf{R}$  mapping pairs of tags to real numbers such that  $d(t_1, t_2) = 0 \Leftrightarrow t_1 = t_2$ ,  $d(t_1, t_2) = d(t_2, t_1)$  and  $d(t_1, t_2) + d(t_2, t_3) >= d(t_1, t_3)$ .

A *discrete-event system* is a timed system where the tags in each signal are order-isomorphic with the integers (for a *two-sided* system) or the natural numbers (for a *one-sided* system) [8]. Intuitively, this means that any pair of ordered tags has a finite number of intervening tags.

Two events are *synchronous* if they have the same tag. Two signals are synchronous if each event in one signal is synchronous with an event in the other signal and vice versa. A *system* is *synchronous* if every signal in the system is synchronous with every other signal in the system. A *discrete-time system* is a synchronous discrete-event system.

Synchronous/reactive languages (see e.g. [5]) are synchronous in exactly this sense. The set of tags in a behavior of the system denotes a global "clock" for the system. Every signal conceptually has an event at every tag, although in some models this event could have a value denoting the absence of an event (called *bottom*). At each clock tick, each process maps input values to output values. If cyclic communication is allowed, then some mechanism must be provided to resolve or prevent circular dependencies. One possibility is to constrain the output values to have tags corresponding to the next tick. Another possibility (all too common) is to leave the result unspecified, resulting in nondeterminacy (or worse, infinite computation within one tick). A third possibility is to use fixed-point semantics, where the behavior of the system is defined as a set of events that satisfy all processes.

Concurrency in physical implementations of systems occurs through some combination of *parallelism*, having physically distinct computational resources, and *interleaving*, sharing of a common physical resource. Mechanisms for achieving interleaving vary widely, ranging from operating systems that manage context switches to fully-static interleaving in which concurrent processes are converted (compiled) into a single nonconcurrent process. We focus here on the mechanisms used to manage communication between concurrent processes.

Parallel physical systems naturally share a common notion of

time, according to the laws of physics. The time at which an event in one subsystem occurs has a natural ordering relationship with the time at which an event occurs in another subsystem. Physically interleaved systems also share a natural common notion of time.

Logical systems, on the other hand, need a mechanism to explicitly share a notion of time. Consider two imperative programs interleaved on a single processor under the control of time-sharing operating system. Interleaving creates a natural ordering between events in the two processes, but this ordering is generally unreliable, because it heavily depends on scheduling policy, system load and so on. Some synchronization mechanism is required if those two programs need to cooperate.

More generally, in logically concurrent systems, maintaining a coherent *global* notion of time as a total order on events, can be extremely expensive. Hence in practice this is replaced whenever possible with an *explicit synchronization*, in which this total order is replaced by a partial order. Returning to the example of two processes running under a time-sharing operating system, we take precautions to ensure an ordering of two events only if the ordering of these two events matters.

A variety of mechanisms for managing the order of events, and hence for communicating information between processes, has arisen. Some of the most common ones are:

• Unsynchronized

In an unsynchronized communication, a producer of information and a consumer of the information are not coordinated. There is no guarantee that the consumer reads valid information produced by the producer, and there is no guarantee that the producer will not overwrite previously produced data before the consumer reads the data. In the tagged-signal model, the repository for the data is modeled as a process, and the reading and writing events have no enforced ordering relationship between their tags.

• Read-modify-write

Commonly used for accessing shared data structures, this strategy locks a data structure between a read and write from a process, preventing any other accesses. In other words, the actions of reading, modifying, and writing are atomic (indivisible). In the tagged-signal model, the repository for the data is modeled as a process where events associated with this process are totally ordered (resulting in a globally partially ordered model). The read-modify-write is modeled as a single event.

Unbounded FIFO buffered

This is a point-to-point communication strategy, where a producer generates a sequence of data tokens and consumer consumes these tokens, but only after they have been generated. In the tagged-signal model, this is a simple connection where the signal on the connection is constrained to have totally ordered tags. The tags model the ordering imposed by the FIFO model. If the consumer implements blocking reads, then it imposes a total order on events at all its input signals. This model captures essential properties of both Kahn process networks and dataflow [13].

Bounded FIFO buffered

In this case, the data repository is modeled as a process that imposes ordering constraints on its inputs (which come from the producer) and the outputs (which go to the consumer). Each of the input and output signals are internally totally ordered. The simplest case is where the size of the buffer is one, in which case the input and output events must be interleaved so that each output event lies between two input events. Larger buffers impose a maximum difference (often called *synchronic distance*) between the number of input and output events.

Note that some implementations of this communication mechanism may not really block the writing process when the buffer is full, thus requiring some higher level of flow control to ensure that this never happens, or that it does not cause any harm.

Rendezvous

In the simplest form of rendezvous, implemented for example in Occam and Lotos, a single writing process and a single reading process must simultaneously be at the point in their control flow where the write and the read occur. It is a convenient communication mechanism, because it has the semantics of a single assignment, in which the writer provides the right-hand side, and the reader provides the left-hand side. In the tagged-signal model, this is imposed by events with identical tags [8]. Lotos offers, in addition, multiple rendezvous, in which one among multiple possible communications is *non-deterministically* selected. Multiple rendezvous is more flexible than single rendezvous, because it allows the designer to specify more easily several "expected" communication ports at any given time, but it is very difficult and expensive to implement correctly.

Of course, various combinations of the above models are possible. For example, in a partially unsynchronized model, a consumer of data may be required to wait until the first time a producer produces data, after which the communication is unsynchronized.

The essential features of the concurrency and communication styles described above are presented in Table I. These are distinguished by the number of transmitters and receivers (e.g., broadcast versus point-to-point communication), the size of the communication buffer, whether the transmitting or receiving process may continue after an unsuccessful communication attempt (blocking reads and writes), and whether the result of each write can be read at most once (single reads).

#### B. Common Models of Computation

We are now ready to use the scheme developed in the previous Section to classify and analyze several models of computation that have been used to describe embedded systems. We will consider issues such as ease of modeling, efficiency of analysis (simulation or formal verification), automated synthesizability, optimization space versus over-specification, and so on.

## **B.1** Discrete-Event

Time is an integral part of a discrete-event model of computation. Events usually carry a totally-ordered time stamp indicating the time at which the event occurs. A DE simulator usually maintains a global event queue that sorts events by time stamp.

Digital hardware is often simulated using a discrete-event approach. The Verilog language, for example, was designed as an input language for a discrete-event simulator. The VHDL

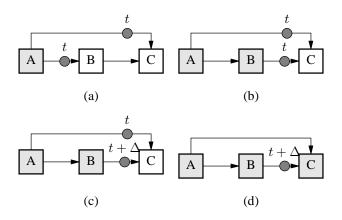

Fig. 3. Simultaneous events in a discrete-event system. (a) Process A produces events with the same time stamp. Should B or C be fired next? (b) Zerodelay process B has fired. How many times should C be fired? (c) Deltadelay process B has fired; C will consume A's output next. (d) C has fired once; it will fire again to consume B's output.

language also has an underlying discrete-event model of computation.

Discrete-event modeling can be expensive—sorting time stamps can be time-consuming. Moreover, ironically, although discrete-event is ideally suited to modeling distributed systems, it is very challenging to build a distributed discrete-event simulator. The global ordering of events requires tight coordination between parts of the simulation, rendering distributed execution difficult.

Discrete-event simulation is most efficient for large systems with large, frequently idle or autonomously operating sections. Under discrete-event simulation, only the changes in the system need to be processed, rather than the whole system. As the activity of a system increases, the discrete-event paradigm becomes less efficient because of the overhead inherent in processing time stamps.

Simultaneous events, especially those arising from zero-delay feedback loops, present a challenge for discrete-event models of computation. In such a situation, events may need to be ordered, but are not.

Consider the discrete-event system shown in Figure 3. Process B has zero delay, meaning that its output has the same time stamp as its input. If process A produces events with the same time stamp on each output, there is ambiguity about whether B or C should be invoked first, as shown in Figure 3(a).

Suppose B is invoked first, as shown in Figure 3(b). Now, depending on the simulator, C might be invoked once, observing both input events in one invocation, or it might be invoked twice, processing the events one at a time. In the latter case, there is no clear way to determine which event should be processed first.

The addition of delta delay makes such nondeterminacy easier to prevent, but does not avoid it completely. It introduces a two-level model of time in which each instant of time is broken into (a potentially infinite number of) totally-ordered delta steps. The simulated time reported to the user, however, does not include delta information. A "zero-delay" process in this model actually has delta delay. For example, Process B would have delta delay, so firing A followed by B would result in the situation in Figure 3(c). The next firing of C will see the event

| TABLE I                                                |  |  |  |  |

|--------------------------------------------------------|--|--|--|--|

| A COMPARISON OF CONCURRENCY AND COMMUNICATION SCHEMES. |  |  |  |  |

|                     | Transmitters | Receivers | Buffer Size | Blocking Reads | Blocking Writes | Single Reads |

|---------------------|--------------|-----------|-------------|----------------|-----------------|--------------|

| Unsynchronized      | many         | many      | one         | no             | no              | no           |

| Read-Modify-Write   | many         | many      | one         | yes            | yes             | no           |

| Unbounded FIFO      | one          | one       | unbounded   | yes            | no              | yes          |

| Bounded FIFO        | one          | one       | bounded     | yes            | maybe           | yes          |

| Single Rendezvous   | one          | one       | one         | yes            | yes             | yes          |

| Multiple Rendezvous | one          | one       | one         | no             | no              | yes          |

from A only; the firing after that will see the (delay-delayed) event from B.

Other simulators, including the DE simulator in Ptolemy [14], attempt to statically analyze data precedences within a single time instant. Such precedence analysis is similar to that done in synchronous languages (Esterel, Lustre, and Signal) to ensure that simultaneous events are processed deterministically. It determines a partial ordering of events with the same time stamp by examining data precedences.

Adding a feedback loop from Process C to A in Figure 3 would create a problem if events circulate through the loop without any increment in time stamp. The same problem occurs in synchronous languages, where such loops are called causality loops. No precedence analysis can resolve the ambiguity. In synchronous languages, the compiler may simply fail to compile such a program. Some discrete-event simulators will execute the program nondeterministically, while others support tighter control over the sequencing through graph annotations.

#### **B.2** Communicating Finite State Machines

Finite State Machines (FSMs) are an attractive model for embedded systems. The amount of memory required by such a model is always decidable, and is often an explicit part of its specification. Halting and performance questions are always decidable since each state can, in theory, be examined in finite time. In practice, however, this may be prohibitively expensive.

A traditional FSM consists of:

- a set of input symbols (the Cartesian product of the sets of values of the input signals),

- a set of output signals (the Cartesian product of the sets of values of the output signals),

- a finite set of states with a distinguished initial state,

- an output function mapping inputs and states to outputs, and

- a next-state function mapping inputs and states to (next) states.

The input to such a machine is a sequence of input symbols, and the output is a sequence of output symbols.

Traditional FSMs are good for modeling sequential behavior, but are impractical for modeling concurrency or memory because of the so-called state explosion problem. A single machine mimicking the concurrent execution of a group of machines has a number of states equal to the *product* of the number of states of each machine. A memory has as many states as the number of values that can be stored at each location *raised to the power* of the number of locations. The number of states alone is not always a good indication of complexity, but it often has a strong correlation. Harel advocated the use of three major mechanisms that reduce the size (and hence the visual complexity) of finite automata for modeling practical systems [15]. The first one is hierarchy, in which a state can represent an enclosed state machine. That is, being in a particular state a has the interpretation that the state machine enclosed by a is active. Equivalently, being in state a means that the machine is in one of the states enclosed by a. Under the latter interpretation, the states of a are called "or states." Or states can exponentially reduce the complexity (the number of states) required to represent a system. They compactly describe the notion of *preemption* (a high-priority event suspending or "killing" a lower priority task), that is fundamental in embedded control applications.

The second mechanism is concurrency. Two or more state machines are viewed as being simultaneously active. Since the system is in one state of each parallel state machine simultaneously, these are sometimes called "and states." They also provide a potential exponential reduction in the size of the system representation.

The third mechanism is non-determinism. While often nondeterminism is simply the result of an imprecise (maybe erroneous) specification, it can be an extremely powerful mechanism to reduce the complexity of a system model by *abstraction*. This abstraction can either be due to the fact that the exact functionality must still be defined, or that it is irrelevant to the properties currently considered of interest. E.g., during verification of a given system component, other components can be modeled as non-deterministic entities to compactly constrain the overall behavior. A system component can also be described non-deterministically to permit some optimization during the implementation phase. Non-determinism can also provide an exponential reduction in complexity.

These three mechanisms have been shown in [16] to cooperate synergistically and orthogonally, to provide a potential triple exponential reduction in the size of the representation with respect to a single, flat deterministic  $FSM^6$ .

Harel's Statecharts model uses a synchronous concurrency model (also called synchronous composition). The set of tags is a totally ordered countable set that denotes a global "clock" for the system. The events on signals are either produced by state transitions or inputs. Events at a tick of the clock can trigger state transitions in other parallel state machines at the same

<sup>&</sup>lt;sup>6</sup>The exact claim in [16] was that "and" type non-determinism (in which all non-deterministic choices must be successful), rather than hierarchical states, was the third source of exponential reduction together with "or" type non-determinism and concurrency. Hierarchical states, on the other hand, were shown in that paper to be able to simulate "and" non-determinism with only a polynomial increase in size.

clock. Unfortunately, Harel left open some questions about the semantics of causality loops and chains of instantaneous (same tick) events, triggering a flurry of activity in the community that has resulted in at least twenty variants of Statecharts [17].

Most of these twenty variants use the synchronous concurrency model. However, for many applications, the tight coordination implied by the synchronous model is inappropriate. In response to this, a number of more loosely coupled asynchronous FSM models have evolved, including behavioral FSMs [18], SDL process networks [18], and codesign FSMs [19].

A model that is closely related to FSMs is Finite Automata. FAs emphasize the acceptance or rejection of a sequence of inputs rather than the sequence of output symbols produced in response to a sequence of input symbols. Most notions, such as composition and so on, can be naturally extended from one model to the other.

In fact, any of the concurrency models described in this paper can be usefully combined with FSMs. In the Ptolemy project [14], FSMs are hierarchically nested with dataflow, discrete-event, or synchronous/reactive models [20]. The nesting is arbitrarily deep and can mix concurrency models at different levels of the hierarchy. This very flexible model is called "\*charts," pronounced "star charts," where the asterisk is meant to suggest a wildcard.

Control Flow Expressions (CFEs, [21]) have been recently proposed to represent the control flow of a set of operations in a cycle-based specification language. CFEs are an algebraic model extending Regular Expressions [9] and can be compiled into FSMs that can be used in the synthesis of a control unit.

## B.3 Synchronous/Reactive

In a synchronous model of computation, all events are synchronous, i.e., all signals have events with identical tags. The tags are totally ordered, and globally available. Simultaneous events (those in the same clock tick) may be totally ordered, partially ordered, or unordered, depending on the model of computation. Unlike the discrete-event model, all signals have events at all clock ticks, simplifying the simulator by requiring no sorting. Simulators that exploit this simplification are called cyclebased or cycle-driven simulators. Processing all events at a given clock tick constitutes a cycle. Within a cycle, the order in which events are processed may be determined by data precedences, which define microsteps. These precedences are not allowed to be cyclic, and typically impose a partial order (leaving some arbitrary ordering decisions to the scheduler). Cyclebased models are excellent for clocked synchronous circuits, and have also been applied successfully at the system level in certain signal processing applications.

A cycle-based model is inefficient for modeling systems where events do not occur at the same rate in all signals. While conceptually such systems can be modeled (using, for example, special tokens to indicate the absence of an event), the cost of processing such tokens is considerable. Fortunately, the cyclebased model is easily generalized to multirate systems. In this case, every *n*th event in one signal aligns with the events in another.

A multirate cycle-based model is still somewhat limited. It is an excellent model for synchronous signal processing systems where sample rates are related by constant rational multiples, but in situations where the alignment of events in different signals is irregular, it can be inefficient.

The more general synchronous/reactive model is embodied in the so-called synchronous languages [22]. Esterel [23] is a textual imperative language with sequential and concurrent statements that describe hierarchically-arranged processes. Lustre [24] is a textual declarative language with a dataflow flavor and a mechanism for multirate clocking. Signal [25] is a textual relational language, also with a dataflow flavor and a more powerful clocking system. Argos [26], a derivative of Harel's Statecharts [27], is a graphical language for describing hierarchical finite state machines. Halbwachs [5] gives a good summary of this group of languages.

The synchronous/reactive languages describe systems as a set of concurrently-executing synchronized modules. These modules communicate through signals that are either present or absent in each clock tick. The presence of a signal is called an event, and often carries a value, such as an integer. The modules are reactive in the sense that they only perform computation and produce output events in instants with at least one input event.

Every signal in these languages is conceptually (or explicitly) accompanied by a clock signal, which has meaning relative to other clock signals and defines the global ordering of events. Thus, when comparing two signals, the associated clock signals indicate which events are simultaneous and which precede or follow others. In the case of Signal and Lustre, clocks have complex interrelationships, and a clock calculus allows a compiler to reason about these ordering relationships and to detect inconsistencies in the definition. Esterel and Argos have simpler clocking schemes and focus instead on finite-state control.

Most of these languages are static in the sense that they cannot request additional storage nor create additional processes while running. This makes them well-suited for bounded and speedcritical embedded applications, since their behavior can be extensively analyzed at compile time. This static property makes a synchronous program finite-state, greatly facilitating formal verification.

Verifying that a synchronous program is causal (noncontradictory and deterministic) is a fundamental challenge with these languages. Since computation in these languages is delayfree and arbitrary interconnection of processes is possible, it is possible to specify a program that has either no interpretation (a contradiction where there is no consistent value for some signal) or multiple interpretations (some signal has more than one consistent value). Both situations are undesirable, and usually indicate a design error. A conservative approach that checks for causality problems structurally flags an unacceptably large number of programs as incorrect because most will manifest themselves only in unreachable program states. The alternative, to check for a causality problem in any reachable state, can be expensive since it requires an exhaustive check of the state space of the program.

In addition to the ability to translate these languages into finite-state descriptions, it is possible to compile these languages directly into hardware. Techniques for translating both Esterel [28] and Lustre [29] into hardware have been proposed. The result is a logic network consisting of gates and flip-flops that can be optimized using traditional logic synthesis tools. To execute such a system in software, the resulting network is simply simulated. The technique is also the basis to perform more efficiently causality checks, by means of implicit state space traversal techniques [30].

## **B.4 Dataflow Process Networks**

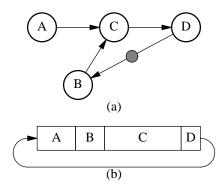

In dataflow, a program is specified by a directed graph where the nodes (called *actors*) represent computations and the arcs represent totally ordered sequences (called *streams*) of events (called *tokens*). In figure 4(a), the large circles represent actors, the small circle represents a token and the lines represent streams. The graphs are often represented visually and are typically hierarchical, in that an actor in a graph may represent another directed graph. The nodes in the graph can be either language primitives or subprograms specified in another language, such as C or FORTRAN. In the latter case, we are mixing two of the models of computation from figure 2, where dataflow serves as the coordination language for subprograms written in an imperative host language.

Dataflow is a special case of Kahn process networks [13], [31]. In a Kahn process network, communication is by unbounded FIFO buffering, and processes are constrained to be continuous mappings from input streams to output streams. "Continuous" in this usage is a topological property that ensures that the program is determinate [13]. Intuitively, it implies a form of causality without time; specifically, a process can use partial information about its input streams to produce partial information about its output streams. Adding more tokens to the input stream will never result in having to change or remove tokens on the output stream that have already been produced. One way to ensure continuity is with blocking reads, where any access to an input stream results in suspension of the process if there are no tokens. One consequence of blocking reads is that a process cannot test an input channel for the availability of data and then branch conditionally to a point where it will read a different input.

In dataflow, each process is decomposed into a sequence of firings, indivisible quanta of computation. Each firing consumes and produces tokens. Dividing processes into firings avoids the multitasking overhead of context switching in direct implementations of Kahn process networks. In fact, in many of the signal processing environments, a major objective is to statically (at compile time) schedule the actor firings, achieving an interleaved implementation of the concurrent model of computation. The firings are organized into a list (for one processor) or set of lists (for multiple processors). Figure 4(a) shows a dataflow graph, and Figure 4(b) shows a single processor schedule for it. This schedule is a list of firings that can be repeated indefinitely. One cycle through the schedule should return the graph to its original state (here, state is defined as the number of tokens on each arc). This is not always possible, but when it is, considerable simplification results [32]. In many existing environments, what happens within a firing can only be specified in a host language with imperative semantics, such as C or C++. In the Ptolemy system [14], it can also consist of a quantum of computation specified with any of several models of computation, such as FSMs, a synchronous/reactive subsystem, or a discrete-event subsystem [33].

A useful formal device is to constrain the operation of a firing to be functional, i.e., a simple, stateless mapping from input

Fig. 4. (a) A dataflow process network (b) A single-processor static schedule for it

values to output values. Note, however, that this does not constrain the process to be stateless, since it can maintain state in a self-loop: an output that is connected back to one of its inputs. An initial token on this self-loop provides the initial value for the state.

Many possibilities have been explored for precise semantics of dataflow coordination languages, including Karp and Miller's computation graphs [34], Lee and Messerschmitt's synchronous dataflow graphs [35], Lauwereins *et al.*'s cyclo-static dataflow model [36], [37], Kaplan *et al.*'s Processing Graph Method (PGM) [38], Granular Lucid [39], and others [40], [41], [42], [43]. Many of these limit expressiveness in exchange for formal properties (e.g., provable liveness and bounded memory).

Synchronous dataflow (SDF) and cyclo-static dataflow require processes to consume and produce a fixed number of tokens for each firing. Both have the useful property that a finite static schedule can always be found that will return the graph to its original state. This allows for extremely efficient implementations [32]. For more general dataflow models, it is undecidable whether such a schedule exists [10].

A looser model of dataflow is the tagged-token model, in which the partial order of tokens is explicitly carried with the tokens [44]. A significant advantage of this model is that while it logically preserves the FIFO semantics of the channels, it permits out-of-order execution.

Some examples of graphical dataflow programming environments intended for signal processing (including image processing) are Khoros [45], and Ptolemy [14].

#### B.5 Other models

Another commonly used partially ordered concurrency model is based on rendezvous. Two or more concurrent sequential processes proceed autonomously, but at certain points in their control flow, coordinate so that they are simultaneously at specified points. Rendezvous has been developed into elaborate process calculi (e.g., Hoare's CSP [46] and Milner's CCS [47]). It has also been implemented in the Occam and Lotos programming languages. Ada also uses rendezvous, although the implementation is stylistically quite different, using remote procedure calls rather than more elementary synchronization primitives.

Rendezvous-based models of computation are often called *synchronous*. However, by the definition we have given, they are not synchronous. Events are partially ordered, not totally

ordered, with rendezvous points imposing the partial ordering constraints.

No discussing of concurrent models of computation would be complete without mentioning Petri nets [48], [49]. Petri nets are, in their basic form, neither Turing complete nor finite state. They are interesting as uninterpreted model for several very different classes of problems, including some relevant to embedded system design (e.g., process control, asynchronous communication, scheduling, ...). Many questions about Petri nets can be answered in finite time. Moreover, a large user community has developed a large body of theoretical results and practical design aids and methods based on them. In particular, partial orderbased verification methods (e.g. [50], [51], [6]) are one possible answer to the state explosion problem plaguing FSM-based verification techniques.

## C. Languages

The distinction between a language and its underlying model of computation is important. The same model of computation can give rise to fairly different languages (e.g., the imperative Algol-like languages C, C++, Pascal, and FORTRAN). Some languages, such as VHDL and Verilog, support two or more models of computation<sup>7</sup>.

The model of computation affects the *expressiveness* of a language — which behaviors can be described in the language, whereas the syntax affects compactness, modularity, and reusability. Thus, for example, object-oriented properties of imperative languages like C++ are more a matter of syntax than a model of computation.

The expressiveness of a language is an important issue. At one extreme, a language that is not expressive enough to specify a particular behavior is clearly unsuitable, but the other extreme also raises problems. A language that is too expressive often raises the complexity of analysis and synthesis. In fact, for very expressive languages, many analysis and synthesis problems become undecidable: no algorithm will solve all problem instances in finite time.

A language in which a desired behavior cannot be represented succinctly is also problematic. The difficulty of solving analysis and synthesis problems is at least linear in the size of the problem description, and can be as bad as several times exponential, so choosing a language in which the desired behavior of the system is compact can be critical.

A language may be very incomplete and/or very abstract. For example, it may specify only the interaction between computational modules, and not the computation performed by the modules. Instead, it provides an interface to a host language that specifies the computation, and is called a coordination language (examples include Linda [41], Granular Lucid [39], and Ptolemy domains [14]). Or the language may specify only the causality constraints of the interactions without detailing the interactions themselves nor providing an interface to a host language. In this case, the language is used as a tool to prove properties of systems, as done, for example, in process calculi [46], [47] and Petri nets [48], [49]. In still more abstract modeling, components in the system are replaced with nondeterminate specifications that give constraints on the behavior, but not the behavior itself. Such abstraction provides useful simplifications that help formal verification.

## D. Heterogeneous Models of Computation

The variety of models of computation that have been developed is only partially due to immaturity in the field. It appears that different models fundamentally have different strengths and weaknesses, and that attempts to find their common features result in models that are very low level, difficult to use. These low level models (such as Dijkstra's P/V systems [52]) provide a good theoretical foundation, but not a good basis for design.

Thus we are faced with two alternatives in designing complex, heterogeneous systems. We can either use a single unified approach and suffer the consequences, or we can mix approaches. To use the unified approach today we could choose between VHDL and C for a mixed hardware and software design, doing the entire design in one or the other (i.e. specifying the software in VHDL or the hardware in C). Or worse, we could further bloat the VHDL language by including a subset designed for software specification (e.g. by making Ada a subset of VHDL). In the alternative that we advocate, we mix approaches while keeping them conceptually distinct, for example by using both VHDL *and* C in a mixed hardware/software design.

The key problem in the mixed approach, then, is to define the semantics of the interaction of fundamentally different models of computation. It is not simply a problem of interfacing languages. It is easy, for example, to provide a mechanism for calling C procedures from VHDL. But what does it mean if two concurrent VHDL entities call C procedures that interact? The problem is exacerbated by the lack of agreed-upon semantics for C or VHDL.

Studying the interaction semantics of mixed models of computation is the main objective of the Ptolemy project [14]. There, a hierarchical framework is used, where a specification in one model of computation can contain a primitive that is internally implemented using another model of computation. The object-oriented principle of information hiding is used to isolate the models from one another as much as possible.

## III. VALIDATION

Validation loosely refers to the process of determining that a design is correct. Simulation remains the main tool to validate a model, but the importance of formal verification is growing, especially for safety-critical embedded systems. Although still in its infancy, it shows more promise than verification of arbitrary systems, such as generic software programs, because embedded systems are often specified in a more restricted way. For example, they are often finite-state.

Many safety properties (including deadlock detection) can be detected in a time-independent way using existing model checking and language containment methods (see, e.g., Kurshan [53] and Burch *et al.* [54]). Unfortunately, verifying most temporal properties is much more difficult (Alur and Henzinger [55] provide a good summary). Much more research is needed before this is practical.

<sup>&</sup>lt;sup>7</sup>They directly support the Imperative model within a process, and the Discrete Event model among processes. They can also support Extended Finite State Machines under suitable restrictions known as the "synthesizable subset".

# A. Simulation

Simulating embedded systems is challenging because they are heterogeneous. In particular, most contain both software and hardware components that must be simulated at the same time. This is the co-simulation problem.

The basic co-simulation problem is reconciling two apparently conflicting requirements:

- to execute the software as fast as possible, often on a host machine that may be faster than the final embedded CPU, and certainly is very different from it; and

- to keep the hardware and software simulations synchronized, so that they interact just as they will in the target system.

One approach, often taken in practice, is to use a generalpurpose software simulator (based, e.g., on VHDL or Verilog) to simulate a model of the target CPU, executing the software program on this simulation model. Different models can be employed, with a tradeoff between accuracy and performance:

· Gate-level models

These are viable only for small validation problems, where either the processor is a simple one, or very little code needs to be run on it, or both.

• Instruction-set architecture (ISA) models augmented with hardware interfaces

An ISA model is a standard processor simulator (often written in C) augmented with hardware interface information for coupling to a standard logic simulator.

• Bus-functional models

These are hardware models only of the processor interface; they cannot run any software. Instead, they are configured (programmed) to make the interface appear as if software were running on the processor. A stochastic model of the processor and of the program can be used to determine the mix of bus transactions.

Translation-based models

These convert the code to be executed on a processor into code that can be executed natively on the computer doing the simulation. Preserving timing information and coupling the translated code to a hardware simulator are the major challenges.

When more accuracy is required, and acceptable simulation performance is not achievable on standard computers, designers sometimes resort to *emulation*. In this case, configurable hardware emulates the behavior of the system being designed.

Another problem is the accurate modeling of a controlled electromechanical system, which is generally governed by a set of differential equations. This often requires interfacing to an entirely different kind of simulator.

# A.1 Co-simulation Methods

In this section, we present a survey of some of the representative co-simulation methods, summarized in Table II. A unified approach, where the entire system is translated into a form suitable for a single simulator, is conceptually simple, but computationally inefficient. Making better use of computational resources often means distributing the simulation, but synchronization of the processes becomes a challenge.

The method proposed by Gupta *et al.* [56] is typical of the unified approach to co-simulation. It relies on a single custom simulator for hardware and software that uses a single event queue and a high-level, bus-cycle model of the target CPU.

Rowson [57] takes a more distributed approach that loosely links a hardware simulator with a software process, synchronizing them with the standard interprocess communication mechanisms offered by the host operating system. One of the problems with this approach is that the relative clocks of software and hardware simulation are not synchronized. This requires the use of handshaking protocols, which may impose an undue burden on the implementation. This may happen, for example, because hardware and software would not need such handshaking since the hardware part runs in reality much faster than in the simulation.

Wilson [58] describes the use of a commercial hardware simulator. In this approach, the simulator and software compiled on the host processor interact via a bus-cycle emulator inside the hardware simulator. The software and hardware simulator execute in separate processes and the two communicate via UNIX pipes. Thomas *et al.* [59] take a similar approach.

Another approach keeps track of time in software and hardware independently, using various mechanisms to synchronize them periodically. For example, ten Hagen et al. [60] describe a two-level co-simulation environment that combines a timed and untimed level. The untimed level is used to verify timeindependent properties of the system, such as functional correctness. At this level, software and hardware run independent of each other, passing messages whenever needed. This allows the simulation to run at the maximum speed, while taking full advantage of the native debugging environments both for software and for hardware. The timed level is used to verify timedependent properties, requiring the definition of time in hardware and software. In hardware, time can be measured either on the basis of clock cycles (cycle-based simulation, assuming synchronous operation) for maximum performance, or on the basis of estimated or extracted timing information for maximum precision. In software, on the other hand, time can be measured either by profiling or clock cycle counting information for maximum performance, or by executing a model of the CPU for maximum precision. The authors propose two basic mechanisms for synchronizing time in hardware and software.

- 1. Software is the master and hardware is the slave. In this case, software decides when to send a message, tagged with the current software clock cycle, to the hardware simulator. Depending on the relation between software and hardware time, the hardware simulator can either continue simulation until software time or back-up the simulation to software time (this requires checkpointing capabilities, which few hardware simulators currently have).

- 2. Hardware is the master and software is the slave. In this case, the hardware simulator directly calls communication procedures which, in turn, call user software code.

Kalavade and Lee [61] and Lee and Rabaey [63] take a similar approach. The simulation and design environment Ptolemy [14] is used to provide an interfacing mechanism between different domains. In Ptolemy, objects described at different levels of abstraction and using different semantic models are composed hierarchically. Each abstraction level, with its own semantic model, is a "domain" (e.g., dataflow, discrete-event). Atomic objects (called "stars") are the primitives of the domain (e.g.,

| Author             | Hardware Simulation | Software Simulation  | Synchronization Mechanism |

|--------------------|---------------------|----------------------|---------------------------|

| Gupta [56]         | logic custom        | bus-cycle custom     | single simulation         |

| Rowson [57]        | logic commercial    | host-compiled        | handshake                 |

| Wilson [58]        | logic commercial    | host-compiled        | handshake                 |

| Thomas [59]        | logic commercial    | host-compiled        | handshake                 |

| ten Hagen (1) [60] | logic commercial    | host-compiled        | handshake                 |

| ten Hagen (2) [60] | cycle-based         | cycle-counting       | tagged messages           |

| Kalavade (1) [61]  | logic custom        | host-compiled        | single simulation         |

| Kalavade (2) [61]  | logic custom        | ISA                  | single simulation         |

| Lee [61]           | logic custom        | host-compiled        | single simulation         |

| Sutarwala [62]     | logic commercial    | ISA on HW simulation | single simulation         |

TABLE II A comparison of co-simulation methods.

dataflow operators, logic gates). They can be used either in simulation mode (reacting to events by producing events) or in synthesis mode (producing software or a hardware description). "Galaxies" are collections of instances of stars or other galaxies. An instantiated galaxy can belong to a domain different than the instantiating domain. Each domain includes a scheduler, which decides the order in which stars are executed, both in simulation and in synthesis. For synthesis, it must be possible to construct the schedule statically. Whenever a galaxy instantiates a galaxy belonging to another domain (typical in co-simulation), Ptolemy provides a mechanism called a "wormhole" for the two schedulers to communicate. The simplest form of communication is to pass time-stamped events across the interface between domains, with the appropriate data-type conversion.

Kalavade and Lee [61] perform co-simulation at the specification level by using a dataflow model and at the implementation level by using an ISA processor model augmented with the interfaces within a hardware simulator, both built within Ptolemy.

Lee and Rabaey [63] simulate the specification by using concurrent processes communicating via queues within a timed model (the Ptolemy communicating processes domain). The same message exchanging mechanism is retained in the implementation (using a mix of microprocessor-based boards, DSPs, and ASICs), thus performing co-simulation of one part of the implementation with a simulation model of the rest. For example, the software running on the microprocessor can also be run on a host computer, while the DSP software runs on the DSP itself.

Sutarwala and Paulin [62] describe an environment coupled with a retargetable compiler [64] for cycle-based simulation of a user-definable DSP architecture. The user only provides a description of the DSP structure and functionality, while the environment generates a behavioral bus-cycle VHDL model for it, which can then be used to run the code on a standard hardware simulator.

#### B. Formal Verification

Formal verification is the process of mathematically checking that the behavior of a system, described using a formal model, satisfies a given property, also described using a formal model. The two models may or may not be the same, but must share a common semantic interpretation. The ability to carry out formal verification is strongly affected by the model of computation, which determines decidability and complexity bounds. Two distinct types of verification arise:

- Specification Verification: checking an abstract property of a high-level model. An example: checking whether a protocol modeled as a network of communicating FSMs can ever deadlock.

- Implementation Verification: checking if a relatively lowlevel model correctly implements a higher-level model or satisfies some implementation-dependent property. For example: checking whether a piece of hardware correctly implements a given FSM, or whether a given dataflow network implementation on a given DSP completely processes an input sample before the next one arrives.

Implementation verification for hardware is a relatively welldeveloped area, with the first industrial-strength products beginning to appear. For example, most logic synthesis systems have a mechanism to verify a gate-level implementation against a set of Boolean equations or an FSM, to detect bugs in the synthesis software<sup>8</sup>.

While simulation could fall under these definitions (if the property is "the behavior under this stimulus is as expected"), the term formal verification is usually reserved for checking properties of the system that must hold for all or a broad class of inputs. The properties are traditionally broken into two classes:

- Safety properties, which state that no matter what inputs are given, and no matter how non-deterministic choices are resolved inside the system model, the system will not get into a specific undesirable configuration (e.g., deadlock, emission of undesired outputs, etc.)

- Liveness properties, which state that some desired configuration will be visited eventually or infinitely often (e.g., expected response to an input, etc.)

More complex checks, such as the correct implementation of a specification, can usually be done in terms of those basic properties. For example, Dill [65] describes a method to define and check correct implementation for asynchronous logic circuits in an automata-theoretic framework.

In this section we only summarize the major approaches that have been or can be applied to embedded system verification. These can be roughly divided into the following classes:

• Theorem proving methods provide an environment that assists the designer in carrying out a formal proof of specifica-

<sup>8</sup>This shows that the need for implementation verification is not eliminated by the introduction of automated synthesis techniques.

tion or implementation correctness. The assistance can be either in the form of checking the correctness of the proof, or in performing some steps of the proof automatically (e.g., Gordon and Melham's HOL [66], the Boyer-Moore system [67] and PVS [68]). The main problems with this approach are the undecidability of some higher order logics and the large size of the search space even for decidable logics.

- Finite automata methods restrict the power of the model in order to automate proofs. A Finite Automaton, in its simplest form, consists of a set of states, connected by a set of edges labeled with symbols from an alphabet. Various criteria can be used to define which finite or infinite sequences of symbols are "accepted" by the automaton. The set of accepted sequences is generally called the *language* of the automaton. The main verification methods used in this case are language containment and model checking.

- In language containment, both the system and the property to be verified are described as a synchronous composition of automata. The proof is carried out by testing whether the language of one is contained in the language of the other (Kurshan's approach is typical [53]). One particularly simple case occurs when comparing a synchronous FSM with its hardware implementation. Then both automata are on finite strings, and the proof of equivalence can be performed by traversing the state space of their product [69].

- Simulation relations are an efficient *sufficient* (i.e., conservative) criterion to establish language containment properties between automata, originating from the process algebraic community ([47], [46]). Informally, a simulation relation is a relation R between the states of the two automata such that for each pair of states s, s' in R, for each symbol labeling an edge from s, the pair of next states under that symbol is also in R. This relation can be computed much more quickly than the exact language containment test (that in the case of non-deterministic automata requires an exponential determinization step), and hence can be used as a fast heuristic check.