## An Esterel Compiler for a Synchronous/Reactive Development System

Stephen  $Edwards^1$

June 16, 1994

$<sup>^0{\</sup>rm This}$  material is based upon work supported under a National Science Foundation Graduate Research Fellowship. Additional support provided by Interval Research Corporation, Digital Equipment Corporation, and the Semiconductor Research Corporation under grant number  $94{-}\rm DC{-}008$

<sup>&</sup>lt;sup>1</sup>email: sedwards@alumni.caltech.edu

#### Abstract

The objective of this project was to create a different scheme for compiling the Esterel synchronous reactive programming language [6, 5, 4, 9] which could handle larger programs, facilitates debugging, and could be easily retargeted toward different architectures. The approach presented here uses an intermediate representation which is somewhere between a high-level reactive language like Esterel and assembly code for a traditional processor. This is similar to the **ic** format used in the Esterel V3 compiler [8] and Baker's NDAM[2, 3]. Compilation proceeds by translating this into assembly code for a SPARC processor.

This differs significantly from the scheme used in the V3 compiler, which derives a single finite-state machine representing the behavior of the program. The FSM approach offers fast executables and exact causality checking, but suffers from exponential growth of compile times and object code sizes.

This report describes the Esterel language, the intermediate representation used by this new compiler, and how the format is translated into executable SPARC assembly code. Its intended audience are those who wish to understand the workings of this Esterel compiler and those simply curious about the Esterel language.

# Contents

| 1 | $\mathbf{Intr}$ | roduction 4                     |    |  |

|---|-----------------|---------------------------------|----|--|

|   | 1.1             | Reactive Systems                | 6  |  |

|   | 1.2             | Synchrony                       | 6  |  |

|   | 1.3             | Signals                         | 7  |  |

|   | 1.4             | Previous Work                   | 8  |  |

|   | 1.5             | An Alternative                  | 10 |  |

| 2 | $\mathbf{The}$  | he Esterel Language 1           |    |  |

|   | 2.1             | Esterel's Model of Time         | 12 |  |

|   | 2.2             | Signals, Sensors, and Variables | 12 |  |

|   | 2.3             | -                               | 13 |  |

|   | 2.4             | Structure                       | 14 |  |

|   | 2.5             | Core Instructions               | 14 |  |

|   |                 |                                 | 14 |  |

|   |                 | 2.5.2 Var                       | 15 |  |

|   |                 | 2.5.3 Emit                      | 15 |  |

|   |                 | 2.5.4 Halt                      | 15 |  |

|   |                 |                                 | 15 |  |

|   |                 |                                 | 16 |  |

|   |                 |                                 | 18 |  |

|   |                 | -                               | 18 |  |

|   |                 | -                               | 18 |  |

|   |                 |                                 | 19 |  |

|   |                 | -                               | 19 |  |

|   |                 | -                               | 19 |  |

|   |                 | •                               | 19 |  |

|   | 2.7             |                                 | 20 |  |

|   |                 | 2.7.1 Signals                   | 20 |  |

|   |                 |                                 | 20 |  |

|   |                 |                                 | 20 |  |

|   |                 | -,                              | 21 |  |

|   |                 | 1 0                             | 21 |  |

| 3        | Th€            | e Intermediate Representation       | <b>23</b> |

|----------|----------------|-------------------------------------|-----------|

|          | 3.1            | Data Objects                        | 24        |

|          |                | 3.1.1 Signals                       | 24        |

|          |                | 3.1.2 Variables                     | 24        |

|          |                | 3.1.3 Registers                     | 25        |

|          |                | 3.1.4 Exceptions                    | 25        |

|          |                | 3.1.5 Counters                      | 25        |

|          | 3.2            | Processes                           | 25        |

|          | 3.3            | Simple Instructions                 | 26        |

|          |                | 3.3.1 Assignment Statments          | 26        |

|          |                | 3.3.2 Flow-of-Control Statements    | 26        |

|          |                | 3.3.3 emit                          | 27        |

|          |                | 3.3.4 exit                          | 27        |

|          |                | 3.3.5 halt                          | 27        |

|          |                | 3.3.6 require                       | 27        |

|          | 3.4            | The try Instruction                 | 28        |

|          | 3.5            | Translating Esterel                 | 29        |

|          |                |                                     |           |

| 4        | Exe            | ecution                             | 32        |

|          | 4.1            | Causal Interleaving                 | 32        |

|          | 4.2            | Process Routines                    | 33        |

|          | 4.3            | Processor Registers                 | 34        |

|          | 4.4            | Simple Instructions                 | 34        |

|          |                | 4.4.1 Assignment Statements         | 36        |

|          |                | 4.4.2 Flow-of-Control Statements    | 37        |

|          |                | 4.4.3 emit                          | 37        |

|          |                | 4.4.4 exit                          | 37        |

|          |                | 4.4.5 halt                          | 38        |

|          |                | 4.4.6 Require                       | 38        |

|          | 4.5            | The try Instruction                 | 39        |

|          | 4.6            | Example                             | 40        |

|          | 4.7            | Outer Loop                          | 42        |

|          |                |                                     |           |

| <b>5</b> | Cau            | ısality                             | 43        |

| 6        | Res            | ults and Conclusions                | 46        |

| -        | 6.1            | Results for The Esterel V3 Compiler | 46        |

|          | 6.2            | Results for This Compiler           | 48        |

|          | 6.3            | Comments                            | 48        |

|          | 6.4            | Conclusions                         | 50        |

|          | 0.1            |                                     | 00        |

| Α        | $\mathbf{Lex}$ | ical Aspects of Esterel             | 51        |

| в        | Syn            | tax of Esterel                      | 52        |

| $\mathbf{C}$ | A La | urge Example                 | 56 |

|--------------|------|------------------------------|----|

|              | C.1  | Testing Scheme               | 58 |

|              | C.2  | The Main Module              | 58 |

|              | C.3  | The Time Module              | 61 |

|              | C.4  | The Time Control Module      | 66 |

|              | C.5  | The Alarm Module             | 68 |

|              | C.6  | The Alarm Control Module     | 71 |

|              | C.7  | The Timer Module             | 72 |

|              | C.8  | The Timer Control Module     | 76 |

|              | C.9  | The Stopwatch Module         | 78 |

|              |      | The Stopwatch Control Module |    |

|              |      | -                            |    |

## Bibliography

## Chapter 1

# Introduction

The synchronous, reactive programming language Esterel was devised by Berry and Cosserat [6] to describe controllers for real-time systems. Esterel resembles many high-level languages, but incorporates a model of time.

This document describes a compiler that translates Esterel into an intermediate form which is an assembly language for an ideal synchronous, reactive machine, and then translates this into SPARC assembly code. This scheme avoids the problems of rapidly-growing object code size and compilation times in the Esterel V3 compiler supported by CISI Ingenierie [8].

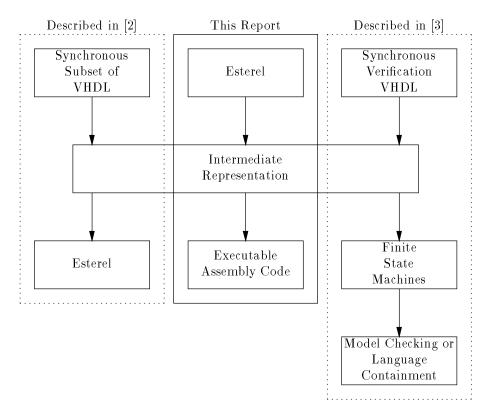

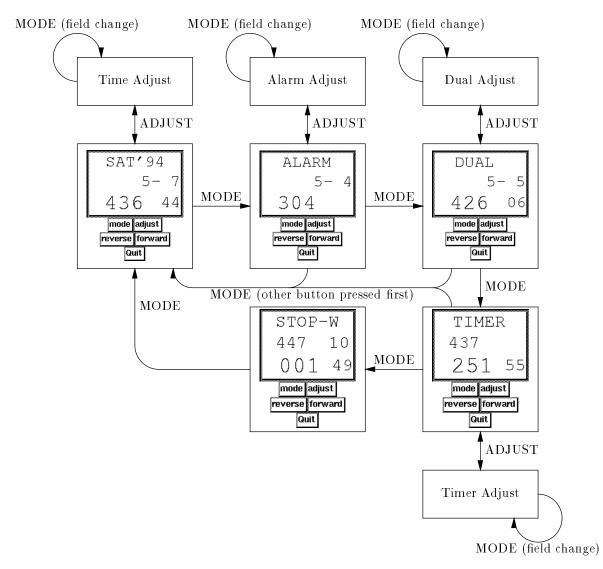

Figure 1.1 illustrates where the compiler presented here fits into the synchronous, reactive development environment being developed at the University of California, Berkeley. Baker [2] uses a similar intermediate format to define a synchronous, reactive subset of the VHDL language, which is compiled into Esterel and run with the Esterel V3 compiler. In addition, Baker [3] has also shown that the intermediate representation can be compiled into finite state machines which can then be forwarded to a model checking or language containment verification system for further analysis.

In all development systems, the ability to simulate the system under development is important. Often, this is done exclusively to catch bugs, but it can be used for other purposes. For example, the mock-up of the digital watch presented in Appendix C could be used to evaluate the user interface of the watch. However, since this is a reactive system, the utility of a simulator would drop rapidly if the simulation was too slow.

The path used in [2] (S-VHDL  $\rightarrow$  NDAM  $\rightarrow$  Esterel) facilitates such simulation, but the Esterel compiler used in that study can have prohibitively long compilation times and large executables. The compiler presented here compiles quickly and produces a fast, small executable.

This document is arranged in roughly the order in which the compiler performs its tasks. Chapter 2 presents the Esterel language in some detail. Chapter 3 contains a description of the representation used as an intermediate be-

Figure 1.1: Where this compiler fits in the synchronous/reactive environment.

tween Esterel source and assembly code. Chapter 4 discusses the issues in the run-time system. Chapter 5 discusses the important notion of causality in Esterel. Finally, Chapter 6 presents some experimental results and raises some questions about the language. Appendices A and B describe the lexical aspects of Estereland a BNF grammar. Appendix C describes a large Esterel program—a digital watch with five functions.

### 1.1 Reactive Systems

Reactive systems respond continuously to their environment at a speed determined by their environment. These differ from transformational systems which have all input available at the beginning of execution and produce all output by the end. Between these two extremes are interactive systems, which also respond to their environment continuously, but do so at the system's rate, not the environment's.

The C programming language is well-suited to constructing transformational systems. The event model employed in the X Window System supports interactive systems. Neither of these, however, directly supports the strict time requirements imposed by reactive systems.

Many embedded systems are required to be reactive. For example, an antilock braking system in a modern automobile would be of little use if it required anywhere between a second and a minute to detect and react to a wheel skidding. An elevator controller which occasionally ignores a floor request would quickly annoy its users.

## 1.2 Synchrony

To support reactive programming, Esterel adopts the strong synchrony model:<sup>1</sup>

The program reacts *instantly* to external events. Most instructions take no time, including control structures. Instructions which do take time, such as delay instructions, do so explicitly.

Adopting this model leads to time being treated as a sequence of discrete *instants* between which nothing of interest happens. Events, such as a button being depressed, happen in a particular instant. In the same instant, the program computes and presents its reaction to the event.

This leads to a straightforward notion of concurrency. When two events occur, either they occur in exactly the same instant (are concurrent), or in different instants.

<sup>&</sup>lt;sup>1</sup> called the strong synchrony hypothesis elsewhere

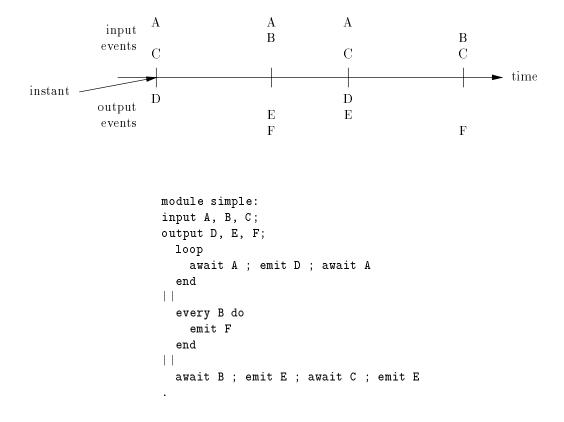

Figure 1.2: Esterel's model of time.

Presented the input events shown above the time line, the Esterel program shown produces the events listed below the time line.

Figure 1.2 on page 7 illustrates these concepts. An instant is denoted by a vertical tick on the time line. The input events for that instant are listed above this and the events these produce are shown below.

Real machines are not, of course, infinitely fast. But if the machine always has enough time to compute its reaction before the next event arrives, then the perfect synchrony model is satisfied.

## 1.3 Signals

A signal is a channel on which events occur. For example, a digital stopwatch with a button labeled start/stop might have an input signal called START/STOP which has an event each time the button is pressed. It might also employ signals called SECOND and MINUTE which have events every second and minute

respectively. It would be natural to synchronize these so that an event on MINUTE occured every sixty seconds. Such synchronization can be specified *exactly* in Esterel:

every 60 SECOND do emit MINUTE end

Esterel supports two types of signal. A *pure* signal is only ever present or absent. A *valued* signal is either absent, or present with some value. For example, in an elevator controller, there might be a pure signal DOORCLOSED indicating that the door has closed, and a valued signal called **FLOOR** indicating on which floor the car has just arrived.

## 1.4 Previous Work

Berry and Cosserat, the designers of Esterel, write [6]

The goal of the ESTEREL project is to develop a real-time language based on a *rigorous formal model*, and actually to develop simultaneously the language, its semantics and its implementation.

They give the semantics [6] through a set of rewrite rules. These take an Esterel program, a set of input events, and a memory state to produce a set of output events, a new memory state, and a new Esterel program which does in its first instant what the old program would do in its second instant.

With a program to perform such a rewrite (originally implemented in a LISP-like language), it is a straightforward task to build an interpreter, albeit a slow one.

Shortly after the interpreter was developed, it was discovered that the rules could also produce an Esterel compiler. Because Esterel has no dynamic data allocation (in particular it contains no recursion), every Esterel program can be treated as a finite-state machine. This is made easier when the data portion (separate from the signal portion) is abstracted away.

To compile an Esterel program, an FSM is formed whose states are labeled with complete Esterel programs and whose transitions are labeled with sets of input events. The reset state is labeled with the program to be compiled. The rewrite rules are applied to this program to find the program which results from *every* possible set of input events. Each of these is a potential new state, which is then rewritten with every possible set of input events which may form new states. This process continues until all states, when rewritten with every possible set of input signals, take transitions to other established states. When this process is completed, the state labels can be discarded. At each step, in effect, the *derivative* of the state machine with respect to some input symbols is taken[7].

To keep the number of states within reason, all data-dependent actions are treated separately. When a transition (the execution of a program in an instant) affects memory, perhaps by evaluating an expression, the transition is labeled with that expression. At run-time, the expression is evaluated and the result stored when that transition is taken.

Data-dependent conditional statements (i.e., if statements) complicate things. Every time an if statement is encountered in a transition, it effectively splits that transition into two branches. At run-time, the if condition is tested and the appropriate branch is taken. Each if statement can, at worst, double the size of the state machine.

This compilation scheme was used in an earlier Esterel compiler. The latest, the Esterel V3 compiler currently supported by CISI INGENIERIE [8] takes a similar approach: it translates the pure Esterel source into an intermediate representation (called ic) which is then used to form an FSM (represented in the oc file format) which captures all behavior of the program.

This approach has nice theoretical properties, but has a few shortcomings. In particular, the number of states is potentially exponential in the size of the program, and compilation (i.e., determining the FSM) takes time proportional to the product of the number of states and the number of possible input signal combinations, which is potentially exponential in the number of input signals. For an example of how bad this can be, see Table 6.1 on page 47.

To partially alleviate the explosion in the number of input signal combinations, the keyword **relation** was included, which allows the programmer to reduce the number of possible input combinations by placing constraints on input signals. For example, signals can be marked as mutually exclusive.

The FSM approach allows for the possibility of many instructions being compiled away so that they take *no* time during execution, leading to a program with a constant response time. Manipulation of pure internal signals can be treated in this manner, but data manipulation cannot, making truly constant response time unlikely.

The main advantage of compiling Esterel source into an FSM is that it ensures the program is *causal* and actually makes sense as a specification. It is comparatively easy in Esterel to specify a program which is a paradox, usually of the form "if this happened, then it did not." If a FSM can be found, then the program is guaranteed, at least, to run. For further discussion of this, see Chapter 5.

The V3 compiler attempts to address the problems of large programs with the -cascade option, but this is limited to cases where the program can be broken up into modules which have no feedback, i.e., there exists an ordering of the modules where module *i* only depends on the actions of modules  $0, \ldots, i-1$ . However, the correctness of this decomposition is only ensured if the program can be compiled without the option, which can be simply impossible due to memory/disk space constraints.

The other problem with the FSM approach is debugging. Since a particular Esterel instruction does not usually map directly to a specific section of code in the executable, it's difficult to say which instructions were executed. In particular, "single-stepping" is not practical.

### 1.5 An Alternative

The approach to compiling Esterel presented here is far more traditional. The scheme first mechanically translates the source text into an intermediate representation similar to three-address code used in modern optimizing compilers, then translates the intermediate representation directly into assembly code for a processor. Currently, this compiler produces code for the SPARC environment. This target was chosen mostly out of convenience—the compiler could easily be adapted to another assembly language, or to produce C code.

Calculating the response for each instant is performed as a fixed-point computation, effectively breaking each instant into a series of steps, as shown in Figure 1.3 on page 11. The compiler produces a routine which, when called, takes one of these steps. This is called by a common outer loop which handles signals from the environment and a few housekeeping chores. The issue of convergence is subtle, but in practice the number of iterations required is small (< 20) and fairly constant during the execution of a program.

This compilation approach works well with larger programs. The effort required by the compiler, the size of the executable, and its execution time are all approximately linear in the size of the original Esterel source. This advantage becomes very clear for large programs, where there can be over two orders of magnitude difference in times/sizes compared to the V3 compiler (see Table 6.2 on page 47).

Another advantage to this approach is that it is more easily debugged. Since most instructions in the source program have a direct manifestation in the final executable, stepping through the program and observing the effects of each instruction is feasible.

Finally, a slight variant of the intermediate representation used here has been used to compile a synchronous, reactive subset of VHDL (see [2, 3]). This suggests that a more general synchronous-reactive compiler could be built by adding additional front ends which use the same intermediate representation.

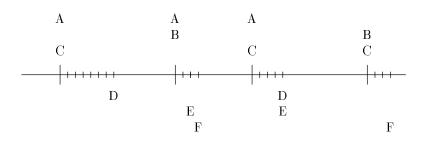

Figure 1.3: Computing the reaction of an Esterel program.

As in Figure 1.2, the input events are shown above the time line. The program computes its reaction in a series of steps following each instant. As long as these steps are completed before the next instant, the perfect synchrony model is satisfied.

A programmer need not and should not consider this—the program will behave as if the signals appear as shown in Figure 1.2.

## Chapter 2

# The Esterel Language

Esterel is a block-structured textual language with a syntax similar to many high-level languages. It has nested if-then-else statements, loops, and the familiar infix expression syntax. It also has constructs for parallel execution, preemption, and exception handling.

Esterel's semantics are defined by a set of core instructions. The remaining instructions are convenient shorthands for combinations of these. This scheme is attractive because it simplifies formal treatments of the language, yet allows a programmer to write programs whose behavior is much clearer to the human reader.

## 2.1 Esterel's Model of Time

Esterel's model of time is fundamental to the definition of the language. As described earlier, Esterel invokes the strong synchrony model and assumes the program reacts instantly to stimulus. In this framework, the execution of the program is divided up into discrete instants. In each instant, some set of input events is presented and the program computes a set of output events.

## 2.2 Signals, Sensors, and Variables

A signal is a broadcast channel for events. Esterel supports two varieties

- Pure signals are either present or absent in an instant, but never both.

- Valued signals are pure signals with an associated value which only changes on event boundaries, but may be read at any time. The ? operator returns the value of a signal in an expression. For example, ?A refers to the value of signal A.

Sensors are used to represent continuously-varying environmental inputs. Their values are read in the same manner as valued signals, but there is never an event on a sensor, even when the value changes. Sensors may only be inputs from the environment.

Esterel has local variables, but no global variables. These may take boolean or integer values.<sup>1</sup> The value of a variable is set by assignment, and may be tested by an if-then construct.

Signals are used copiously throughout Esterel programs, both for communication with the environment and for internal communication. For most applications, signals are preferred over variables because of their synchronizing ability—and instruction which requires the value of a signal is suspended until the signal has been emitted by another part of the program. Shared variables (written in one part of the program, read in another section executing in parallel in the same instant) are not guaranteed to contain the correct values.

## 2.3 Occurrences

An occurrence describes an instant (the instant in which the occurrence is said to *elapse*) in terms of one or more signal events. Occurrences are used throughout Esterel for synchronization between signals and instructions. For example, the **await** instruction, which simply delays until its occurrence has elapsed, provides a simple form of synchronization.

Occurrences take one of three forms:

#### • Simple

The occurrence elapses in the instant the given signal has an event, excluding any in the current instant.

#### • Immediate

The occurrence elapses in the instant the given signal has an event, including any in the current instant.

#### • Counted

The occurrence elapses in the same instant as the nth event on the given signal, excluding any in the current instant.

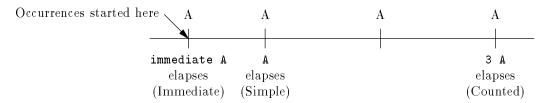

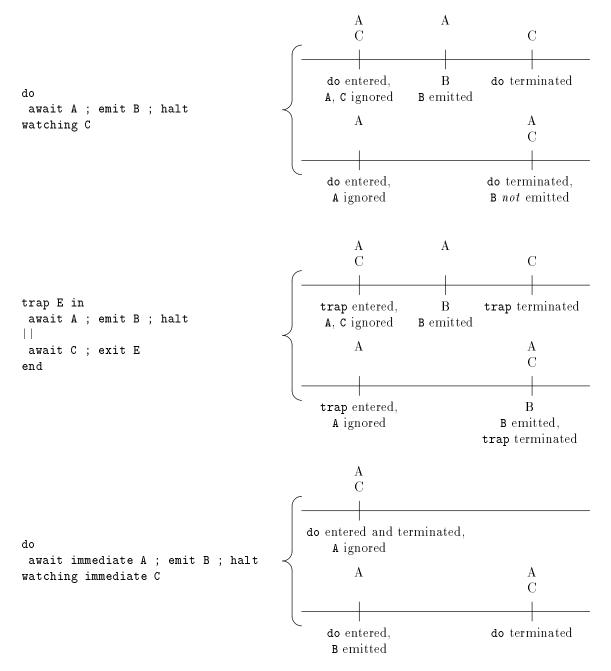

The three types of occurrences are depicted in Figure 2.1.

<sup>&</sup>lt;sup>1</sup>The Esterel V3 compiler supports the importation of variables with more complex types from a host language (such as C), which may be used as arguments to functions from that language. The compiler described herein does not support this.

Figure 2.1: Illustration of the three types of occurrences.

## 2.4 Structure

An Esterel program is broken into a number of modules that execute in parallel. Each module definition contains an interface portion and a body composed of instructions.

Instructions may be composed in sequence or in parallel. Any instruction may be such a composition.

•  $i_1$  ;  $i_2$  ;  $\cdots$  ;  $i_n$

Instructions in a semicolon-delimited sequence are executed in order. First,  $i_1$  is executed. When  $i_1$  terminates,  $i_2$  is executed, and so on. When  $i_n$  terminates, the sequence itself terminates.

These instructions may terminate instantly, leading to an ordering of instructions within an instant. However, something like emit A ; emit B is equivalent to emit B ; emit A since there is no ordering of *events* within an instant.

$\bullet \ i_1 \ | \ | \ i_2 \ | \ | \ \cdots \ | \ | \ i_n$

Instructions delimited by double vertical bars are executed in parallel.  $i_1$  through  $i_n$  are executed immediately. When all instructions have terminated, then the parallel construct terminates.

## 2.5 Core Instructions

### 2.5.1 Signal

A local signal s is introduced an instruction i by the following construct

```

signal s in

i

end

```

The signal s can only be used within the instruction i (which may be a composition of instructions), and is not visible outside of the **signal** construct.

#### 2.5.2 Var

A local variable v with type t (integer or boolean) is introduced into an instruction i with

```

var v : t in

i

end

```

An initializing expression e may be included. This is evaluated when the **var** construct is first entered.

```

\operatorname{var} v := e : t \text{ in}

i

end

```

Like the signal construct, the variable v can only be used within the instruction i, and is not visible elsewhere.

#### 2.5.3 Emit

The emit instruction places an event on a signal s in the current instant and terminates instantly.

$\verb"emit" s$

If the signal s is valued, then the **emit** instruction includes an expression which is also evaluated instantly.

```

emit s( e )

```

#### 2.5.4 Halt

The halt instruction does nothing and never terminates. This is the fundamental time consumer in Esterel. It appears in many composite instructions, often in situations where it can be preempted.

#### 2.5.5 Preemption and Exceptions

The core preemption construct takes the form

```

do i_1 watching o timeout i_2 end

```

The instruction  $i_1$  is executed while occurrence o is watched. If  $i_1$  terminates before o elapses, then the whole do construct terminates. If o does elapse,  $i_1$  is terminated before it has a chance to execute for that the instant and  $i_2$  is executed.

Esterel's exception construct is

The instruction  $i_1$ , which somewhere contains the instruction **exit** E, is executed while exception E is watched. If  $i_1$  terminates without E being raised by the **exit** instruction, then the **trap** construct terminates. If  $i_1$  raises E, then  $i_1$  is terminated and  $i_2$  is executed. However, when E is raised,  $i_1$  is allowed to finish for the instant.

Figure 2.2 on page 17 illustrates the differences between do and trap. It employs the composite instruction await o which is a shorthand for do halt watching o, which simply waits for the given occurrence to elapse before terminating.

An exception may be given a value that can be read within the instruction  $i_2$  with the ?? operator. For example, ??F refers to the value of exception F, given by the expression e in exit F(e).

#### 2.5.6 Conditionals

The if statement in Esterel has the familiar form

The boolean expression e is evaluated instantly. If true, then instruction  $i_1$  is executed, otherwise,  $i_2$  is executed.

The other conditional statement in Esterel checks for the presence of a signal.

```

\begin{array}{l} {\rm present} \ s \ {\rm then} \ i_1 \\ {\rm else} \ i_2 \\ {\rm end} \end{array}

```

Here, instruction  $i_1$  is executed if signal s is present in the current instant. Otherwise,  $i_2$  is executed.

For both conditional statements, either the then  $i_1$  or the else  $i_2$  clause may be omitted.

Figure 2.2: An illustration of the differences between do and trap and the effect of the immediate keyword.

On the left are the responses of the fragments on the right to two different sequences of input events.

#### 2.5.7 Loop

Esterel includes an infinite loop instruction:

loop *i* end

This executes the instruction i, waits for it to finish, and executes it again. True infinite loops are often desired in controllers, but when necessary, these can be terminated through preemption or an exception. It is an error for the instruction i to take no time. For example, **loop emit S end**. This corresponds to the program doing an infinite amount of work in zero time.

### 2.6 Composite Instructions

#### 2.6.1 await

The await instruction is one of the most common. It waits for its occurrence to elapse and then terminates.

```

do

await o translates to halt

watching o

```

await also comes in the following elaborate form:

```

await

case o_1 do i_1

case o_2 do i_2

:

case o_n do i_n

end

```

This waits for one of the occurrences  $o_1, \ldots, o_n$  to elapse, say  $o_j$ . Then, instruction  $i_j$  is executed and the **await** terminates. If two occurrences elapse in the same instant, the one *listed first* takes precedence.

This can be built using preemption and exceptions:

```

await

case o_1 do i_1

end

translates to

translates to

i_1

translates to

i_2

translates to

i_1

timeout exit E1 end

i_1

do halt watching <math>o_2

timeout exit E2 end

handle E2 do i_2 end

handle E1 do i_1 end

```

#### 2.6.2 do ... upto

| do       |               | do           |

|----------|---------------|--------------|

| i        | translates to | i ; halt     |

| upto $o$ |               | watching $o$ |

In effect, this forces the duration of instruction i to be exactly the length of occurrence o, terminating i early if it does not finish before o elapses.

#### 2.6.3 loop ... each

This modification of the loop instruction restarts itself whenever its occurrence elapses:

|        |               | loop         |

|--------|---------------|--------------|

| loop   |               | do           |

| i      | translates to | i ; halt     |

| each o |               | watching $o$ |

|        |               | end          |

#### 2.6.4 every ... do

This repeatedly synchronizes its instruction with its occurrence:

|                               |               | await $o$    |

|-------------------------------|---------------|--------------|

| ovorv o do                    |               | loop         |

| every <i>o</i> do<br><i>i</i> | translates to | do           |

| ·                             |               | i ; halt     |

| end                           |               | watching $o$ |

|                               |               | end          |

#### 2.6.5 sustain

Although signals are often thought of as events, the **sustain** instruction allows them to be used as flags. It uses a special signal, **TICK**, which is present in every instant by definition. Thus, **sustain** forces another signal to be present in every instant.

Typically, sustain is used with a do or a trap that defines the length of time that it is executing, and hence, the length of time that its flag is asserted.

```

every TICK do sustain s translates to emit s end

```

## 2.7 A Stopwatch Controller in Esterel

Figure 2.3 on page 22 depicts a simple stopwatch controller illustrating many common characteristics of Esterel programs. The module consists of four (elaborate) instructions running in parallel, each responsible for some part of the stopwatch. All communication, both with the outside world and between different parts of the program, is done through signals. Preemption and exceptions are used liberally.

#### 2.7.1 Signals

A typical digital stopwatch has two buttons marked start/stop and lap/reset, here conveyed through the SS and LR input signals respectively. SECOND is a periodic signal assumed to be generated by an external oscillator once a second.

When in lap mode, the stopwatch continues to measure time, but the display does not change. The **FROZEN** output is present when the display is in this mode. The integer-valued output **TIME** is the value for the display, and does not change when the stopwatch is lap mode.

The internal signal RESET resets the counter. LAP indicates a switch between lap and normal mode. RUN is used as a flag to indicate that the stopwatch is running, and is present in every such instant.

#### 2.7.2 The Start/Stop Button Handler

The first process is responsible for the action of the start/stop button, which is a simple toggle. When the stopwatch is running, the **RUN** signal present in every instant, which is enforced by the **sustain** instruction.

This illustrates how simply state information can be incorporated into Esterel code. Here, there are two states: one which waits for SS, and one which sustains the RUN signal until the next SS signal.

#### 2.7.3 The Lap/Reset Button Handler

The second process is responsible for decoding the action of the lap/reset button. When lap/reset is pressed and the the stopwatch is running, the stopwatch switches into or out of lap mode. If the stopwatch is not running and not in lap mode, then the action is to reset. The **every** construct ensures that these actions are taken exactly when the lap/reset button is pressed.

This behavior could be described by the following boolean equations

$$LAP = B2 \cdot RUN$$

$$RESET = B2 \cdot \overline{RUN} \cdot \overline{FROZEN}$$

Esterel's representation is more flexible than this. Currently this process contains no state information, but in Esterel, it can be added without a significant change to the code. The precedence of the operations is made explicit by the familiar form of the **present** instruction.

#### 2.7.4 The Frozen Display Handler

The third process keeps track of the lap mode and generates the FROZEN signal accordingly. Similar to the first process, it implements a toggle which sustains the FROZEN signal after an odd number of LAP events.

This uses the trap construct to ensure that FROZEN is sustained up to and including the instant LAP appears. This is in contrast with the first process which does not emit RUN when the start/stop button is pressed the second time.

#### 2.7.5 The Counter

The fourth process, the counter, illustrates the use of a local variable and how the explicit initialization feature can be used. By enclosing the **var** declaration and its initialization expression in a loop...upto preemption construct, the reset behavior is automatic and straightforward. The way to think about it is this: A counter is something that starts at zero and goes up every second that the stopwatch is running. If the display is not frozen, then this count should be broadcast to the display. After every reset, this process is restarted.

```

module STOPWATCH:

% Frozen Display Handler

input SS, LR, SECOND;

loop

output TIME(integer);

await LAP ;

trap T in

signal RESET, LAP, RUN, FROZEN in

sustain FROZEN

% Start/Stop Button Handler

await LAP ; exit T

end

loop

\operatorname{end}

await SS;

do

sustain RUN

upto SS

% Counter

end

loop

var second := 0 : integer in

emit TIME(second) ;

% Lap/Reset Button Handler

every SECOND do

present RUN then

every LR do

second := second + 1

present RUN then emit LAP

end ;

else present FROZEN

present FROZEN else

else emit RESET

emit TIME(second)

end

end

end

end

end

end

upto RESET

\operatorname{end}

.

```

Figure 2.3: A stopwatch controller written in Esterel.

## Chapter 3

# The Intermediate Representation

Like many compilers, this compiler translates source code into an intermediate representation before generating assembly language for the target processor. The intermediate representation used here was chosen using the following criteria:

- Completeness—Every construct in Esterel must have a correct translation into the intermediate representation. In particular, it must support the parallel execution and preemption semantics of Esterel.

- Generality—A similar representation has been used in a compilation scheme for a synchronous subset of VHDL [2, 3]. Mimicking this work ensures that this intermediate representation could be used in other situations, allowing the reuse of the code generator.

- Simplicity—Keeping the intermediate representation as simple as possible simplifies the final code generation phase and makes optimization much easier.

The result of balancing these sometimes conflicting requirements is presented below. The intermediate representation chosen is very close to the three-address code used in modern optimizing compilers [1]. All but one of the instructions are "simple" in some sense—they translate into only a few assembly-language instructions. The remaining instruction, **try**, is responsible for parallel execution and preemption and is really the workhorse of the language.

The notion of time employed in the intermediate representation is the same synchronous/reactive one used by Esterel. Only the **halt** instruction takes any time—the rest happen instantly, but in an order.

The following presentation introduces an informal syntax which corresponds directly with the data structures used inside the compiler<sup>1</sup>. This syntax is intended to be illustrative rather than machine-readable, although the compiler can produce it.

## 3.1 Data Objects

Unlike a typical assembly language, the intermediate representation manipulates objects at a higher level than memory and registers. In particular, valued and pure signals identical to Esterel's are included, as well as valued and pure exceptions.

All objects in the intermediate representation are globally accessible—the correct scoping is imposed by the structure of the Esterel program.

#### 3.1.1 Signals

#### $\texttt{s0},\,\texttt{s1},\,\texttt{s2},\,\ldots$

The intermediate representation deals with both pure and valued (with an integer value) signals. At any time during the execution of the program, each signal is in one of the following three states:

- **present**: The signal is present in the current instant.

- absent: The signal is absent in the current instant.

- **unknown**: The presence or absence of the signal in the current instant is unknown.

All the signals used in the program are listed in the Signals block. Each is listed along with its name from the Esterel program, and its type. For example, s1: RING specifies that pure signal s1 represents the signal called RING in the Esterel source program. s5: A(int) indicates that signal A in the Esterel source has been assigned to signal s5.

#### 3.1.2 Variables

#### $v0, v1, v2, \ldots$

Variables take integer values. Esterel's booleans are implemented using the integer values 1 and 0 for true and false respectively. Variable are listed in the **Local Variables** block along with their names from the Esterel program. No type is specified—all are integers.

<sup>&</sup>lt;sup>1</sup>Processes are classes with variable-sized arrays of instruction objects, an integer denoting the process's number, and an integer denoting its program counter. Each instruction is a subclass of a general instruction class. For example, the **try** class contains an array of pointers to the subprocesses it calls, an array of watch clauses, and an array of handle clauses. Information about data objects is also stored in arrays.

#### 3.1.3 Registers

#### $\texttt{r0},\,\texttt{r1},\,\texttt{r2},\,\ldots$

Like variables, these take integer values, but their values are only guaranteed to persist until the next non-assignment statement. Registers are used primarily to store intermediate results in evaluating expressions.

#### 3.1.4 Exceptions

#### e0, e1, e2, ...

The intermediate representation contains both pure and valued exceptions. At any time during execution, each exception is either

- raised: An exit statement has raised the exception

- lowered: The exception is being observed, but no corresponding exit has been executed.

Like signals, each exception is listed in the Exceptions block along with an (int) designation when the exception is valued, and its name from the Esterel program.

#### 3.1.5 Counters

c0, c1, c2, ...

Counters are used in the intermediate representation to keep track of the number of events that have been observed on a particular signal in a counted occurrence. Like signals, each counter is listed along with its name (the name of the signal being counted in that occurrence) in the **Counters** block.

## 3.2 Processes

The program of the intermediate format is build from a hierarchically-arranged group of *processes*—sequences of instructions. A single process behaves like a program on a standard processor—each has a program counter pointing to the instruction currently being executed. Once that instruction has been executed, the program counter is moved to the next instruction to be executed (usually the next in the sequence, but branches are allowed) and execution continues. Each instruction in a process is assigned a small integer label used for branch targets.

Execution of a process may not "fall off the end." The last instruction of a process is a halt, which makes the process's execution cease but does not terminate it, an exit which terminates the process, or an unconditional goto.

Each process is introduced with a line giving its unique name (PO, P1, etc.) and which program counter it uses, e.g., PC1, PC5, etc. Each instruction in

a process is given an index. (0:, 1:, etc.) These labels are used as branch destinations and simplifies correlating assembly language instructions with those in the intermediate format.

## 3.3 Simple Instructions

#### 3.3.1 Assignment Statments

The intermediate representation has one all-encompassing assignment statement which handles most data manipulation. It may have two or three arguments, each of which may be one of the data objects described above or a constant integer. Many combinations of these are unused—for example, the destination of an assignment may not be constant, and only the simple assignment form is allowed to have non-register operands. These policies of use were imposed to simplify the translation of these instructions into assembly code for the SPARC RISC processor, and would simplify the translation for other processors.

• d := s

Simple assignment. The value of the source is written into the destination.

• d := op s

Unary operation. The operator is applied to the value of the source and the result written into the destination. The unary operators are integer negate, binary NOT, and decrement.

•  $d := s_1 \ op \ s_2$

Binary operation. The operator is applied to the values of the two sources and the result written into the destination. The binary operators are integer add, subtract, multiply, divide, and modulus, binary AND and OR, integer equality, integer less than, and integer less than or equal to.

When a signal or exception is referenced, the value returned is the value of the signal in the current instant, and not presence/absence or raised/lowered information. For such accesses to be legal, the presence/absence of a signal must be established in an instant or the raised status of an exception must be known, either from context (The code run by a handle clause of a try obviously knows that the exception has been raised.) or through force (The require statement ensures that the value of a signal is known correctly.).

#### 3.3.2 Flow-of-Control Statements

The intermediate representation has a general branch instruction which either unconditionally branches to an instruction, checks for the zero/non-zero status of a register or variable, the presence/absence of a signal, or the raised/lowered status of an exception. It takes the following forms

| goto l              | Unconditional branch to instruction $l$                |

|---------------------|--------------------------------------------------------|

| if $s$ goto $l$     | If status of $s$ is "true," branch to instruction $l$  |

| if not $s$ goto $l$ | If status of $s$ is "false," branch to instruction $l$ |

#### 3.3.3 emit

The **emit** statement is very similar to its Esterel counterpart. It makes the given signal present in the current instant, and may set its value, if any. The two forms are

emit s Emit the signal semit s r Emit the signal s setting its value to register r

#### 3.3.4 exit

The exit statement, like its Esterel counterpart, can raise an exception and set its value. In the intermediate representation, it also serve to terminate a process (In Esterel, this action was implicit.) The three forms are

| exit                    | Terminate the process                           |

|-------------------------|-------------------------------------------------|

| $\texttt{exit} \ e$     | Terminate the process and raise exception $e$   |

| $\texttt{exit} \ e \ r$ | Terminate the process and raise exception $e$ , |

|                         | assigning it the value in register $r$ .        |

#### 3.3.5 halt

The halt statment, like its Esterel counterpart, prevents further execution of the process, but does not allow it to terminate. This is the only mechanism in the intermediate representation which consumes time. Between instants, each active process is either stopped at a halt or waiting on a halted subprocess.

#### 3.3.6 require

#### require $s_1 \ s_2 \ \dots \ s_k$

When the value of a signal is needed to evaluate an expression, the newest value of that signal is needed. Similarly, a conditional branch which depends on the presence or absence of a signal must know whether the signal is present or absent in an instant before proceeding. The **require** instruction ensures that the named signals are known before execution may proceed.

### 3.4 The try Instruction

The try instruction is responsible for parallel execution of processes and both kinds of preemption (signal- and exception-prompted). Its most general form is

```

try

call p_1

call p_2

:

call p_n

watching s_1 c_1 goto wl_1

watching s_2 c_2 goto wl_2

:

watching s_m c_m goto wl_m

handle e_1 goto el_1

handle e_2 goto el_2

:

handle e_p goto el_p

```

This calls subprocesses  $p_1$  through  $p_n$  while monitoring signals  $s_1$  through  $s_m$  and exceptions  $e_1$  through  $e_p$ . If one of these signals is present or an exception is raised, then the subprocesses are terminated and the handler pointed to by the **goto** is executed, otherwise the instruction terminates when all of its subprocesses have.

More specifically, if exception  $e_i$  is raised and exceptions  $e_1$  through  $e_{i-1}$  are not, then the subprocesses are terminated after they have completed for the instant and execution proceeds with instruction  $el_i$ . If signal  $s_i$  is present, then counter  $c_i$  is decremented. If counter  $c_i$  becomes zero and counters  $c_1$  through  $c_{i-1}$  are non-zero, then the subprocesses are terminated and execution proceeds with instruction  $wl_i$ . The signals are checked before any subprocesses execute in every instant except the first in which the try is executed.

The semantics of this instruction were chosen to capture Esterel's most difficult instruction, **await...case**. This can have a mixture of counted, uncounted, and immediate occurrences. Counters were introduced to handle the counted occurrences. Another approach would have been to introduce a separate process to count the signals. However, since the semantics require that when a preempting signal occurs, *none* of the processes will be executed in that instant, it was not clear how to do this.

In a previous version of this compiler, there were two varieties of the try instruction, one that dealt only with signals, and one that dealt only with exceptions. All instructions in Esterel can be represented by a nesting of such constructs, but since much of the code was the same (program counter initialization, subprocess calling, potential set calculation, and so forth), the two varieties were merged.

## 3.5 Translating Esterel

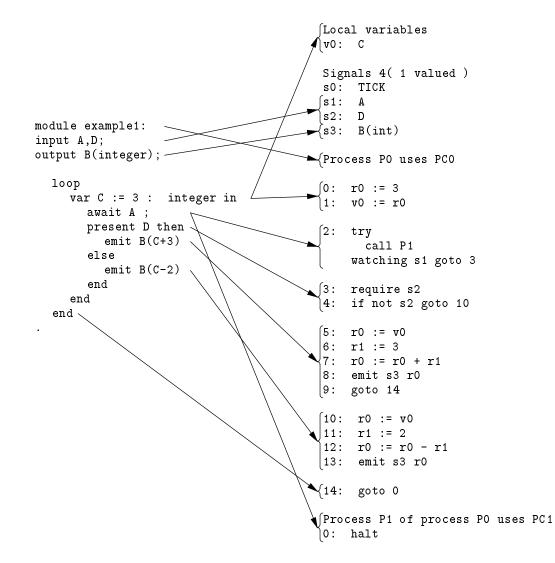

The translation of a small Esterel program into the intermediate format is shown in Figure 3.1 on page 30. The **await A** instruction turns into a **try** which calls a process containing a single **halt** while watching the awaited signal. The **present** instruction, since it needs to know about a signal to correctly check its condition, is composed of a **require** statement followed by a conditional branch.

In this simple example, there are three expressions: "3" in the initialization of variable C, "C + 3" in the first emit, and "C - 2" in the second. These expressions produce code in a RISC-like load-store manner. Values which reside in "memory" (i.e., non-registers) are loaded into registers before being manipulated.

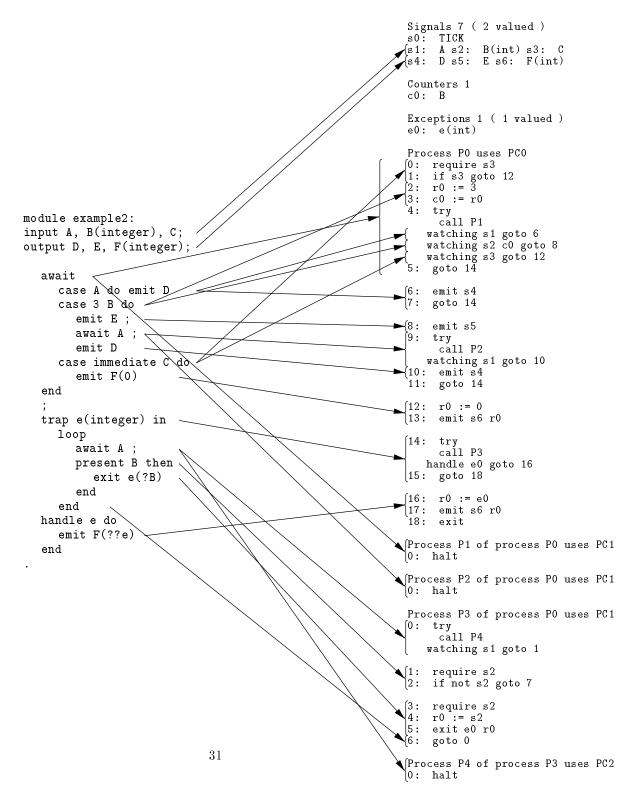

A more elaborate program and its translation are shown in Figure 3.2 on page 31. This example contains an await...case statement, which is the most complex in Esterel, employing the three types of occurrences (simple, counted, and immediate). The counted occurrence requires a counter to be loaded with the iteration count before the try instruction is entered (instructions 2 and 3 of process PO). The immediate occurrence is similar to a simple occurrence, but the presence of the signal is checked before the try instruction is entered (instructions 0 and 1 of process PO).

This example also illustrates the use of an exception. The statements which are observed for the exception are placed in a separate process (P3) and run by a try (instruction 14 of process P0) with a handle clause.

The value of signal B is read by the ? operator in the exit instruction. The exit instruction (instruction 5 of process P3) raises the exception and sets its value to the contents of register r0 which contains the value of signal s2. Note that this signal was required (in instruction 3) before the expression was evaluated. The value of the exception is loaded in the handler routine and emitted through signal F (instructions 12 and 13 of process P0).

Figure 3.1: A small example and its translation into the intermediate format. The local variables and signals are listed above the processes. Each instruction in each process is labeled with a small integer, and each process is introduced with a name and which program counter it uses.

Figure 3.2: A further example illustrating the translation from Esterel into the intermediate format.

## Chapter 4

# Execution

The intermediate format has been chosen so that virtually all instructions are easy to execute on a traditional processor. This compiler generates code for the SPARC architecture, although it could easily be retargeted to another. Arithmetic instructions translate, for the most part, into single assembly language instructions. **emit** simply stores a value in an array in memory, and a conditional branch consists of a test followed by an assembly-language branch.

The difficult part of executing the intermediate format (and hence, Esterel) is ensuring that the correct instructions execute in each instant in the right order. For example, the subprocesses of a **try** must not be executed if any of the watched signals are present in that instant. Also, if an expression reads the value of a signal, and if some other part of the program is going to emit that signal, the expression should get the new value, and not the old.

## 4.1 Causal Interleaving

The approach taken here turns the execution of the intermediate format into a fixed-point computation on the set of signals, both internal and external. The code generator produces a routine, hereafter referred to as the main process routine, that takes incomplete information about the presence or absence of signals and emits what signals it can, changing program counters, variables, counters, exceptions, and so forth in the process. Execution for each instant consists setting all signals except those global inputs that are known to be present or absence of each signal is known.

There is no instruction in the intermediate representation that "unemits" a signal, so something else must establish the absence of a signal. A conservative rule is used to decide which signals are absent:

If an internal or output signal could not be emitted in the current instant, then is marked as absent.

Much of the code produced is responsible for establishing which signals could still be emitted in the current instant. In particular, when the main process has executed what it can using the information it has, it returns the address of a routine that marks all the signals that still have the potential to be emitted in the current instant. The outer loop then marks all unknown signals which are *not* in this potential set as absent.

This technique causes the set of present and absent signals to grow monotonically and the set of unknown signals to shrink monotonically since once a signal is marked as present, it cannot be marked as absent (only unknown signals are marked as absent), and once it is marked as absent, it could not thereafter be emitted since all signals that could possibly be emitted are placed in the potential set.

## 4.2 Process Routines

Each process in the the intermediate representation is translated into a sequence of assembly-language instructions, which compose its process routine.

Each process routine, when called, executes as many instructions as it can, depending on the state of various signals, and returns with

- A program counter that points to the instruction to be executed the next time the process routine is called;

- A potential set calculator that points to a routine that marks those signals which could still be emitted in the current instant; and

- A status, one of

- **Terminated (0)** The process has hit an **exit** instruction and has terminated. In this case, the returned program counter points to this same **exit** instruction and the returned potential set calculator points to a null routine (this process could not emit any more signals this instant).

- Halted (1) The process has hit a halt instruction. In this case, the returned program counter points to this same halt and the returned potential set calculator points to a null routine.

- Waiting (-1) This indicates that the process needs information about more signals before it may proceed, but that it has more to do in the current instant. The returned potential set calculator points to a routine that marks the appropriate signals.

If the process exits or halts, the returned program counter points to the same **exit** or **halt** instruction. This simplifies the code that calls the process: rather than having to test a flag or the program counter against something that indicates the terminated or halted status of the process, it can always call the process regardless of whether it has terminated.

When a process routine contains a **try** instruction, it calls other process routines (i.e., those in **call** clauses of the **try** instruction). Potential set calculators also may call other potential set calculators with the relationships imposed by the **try** instruction.

Each process is assigned a unique program counter. In any program, it may not be possible for every process to be active simultaneously, so each program counter may not have a unique process. In particular, if a process contains two **try** instructions, the processes called by those **try** instructions may share program counters. The assignment of program counters is performed at compile time with a simple recursive rule which makes a worst-case estimate of the number of simultaneously-active processes.

## 4.3 **Processor Registers**

Processor registers are used to return the new program counter, the new potential set calculation routine, and the return status.

Intermediate representation registers are mapped directly onto processor registers.

One processor register stores the base address of all the arrays for addressing purposes.

Register use is shown in Table 4.2.

## 4.4 Simple Instructions

The compiler currently produces assembly code for the SPARC architecture. This is a modern RISC processor with 32 32-bit registers. Register **%g0** is special—it always returns a zero, and may be used as the destination for a result which is ignored.

The branch instructions on the SPARC have a single shadowed instruction following. This instruction is not executed only if the annul flag (part of the branch opcode) is set and the branch fails.

The one addressing mode used by the compiler adds a 12-bit immediate value to a register to form a full 32-bit address. By putting the high-order bits of the base address of the arrays in a register, this mode facilitates quick access to all the run-time data. The syntax

[%i5+%lo(\_V+12)]

| <b>D</b> |     |     |   |

|----------|-----|-----|---|

| Desc     | rip | tio | n |

${\sf C}$  definition

- Multiplicity

- **Program Counters** void (\*PC[])() one per active process point to process routines. These are function pointers.

- Potential Function Pointers void (\*PO[])() one per active process point to potential set calculation routines. These are function pointers.

- Halted Flags char H[] one per active process A process sets its halted flag to 1 when it is finished for the instant. At the beginning of each instant, these flags are all cleared to 0 to restart the processes for the instant. These flags are used by both the process routines and the potential set calculators.

- Signal Presence Flags char S[] one per signal Each signal is either present (1), absent (-1), or unknown (0). At the beginning of each instant, all but the input signals are set to unknown.

Signal Potential Flagschar P[]one per signalThe potential set routines set each signal with the potential to be emittedto 1.Those signals which have no potential (0), and are unknown aremarked as absent.

| Signal Values            | int SV[] | one per valued signal      |

|--------------------------|----------|----------------------------|

| Variable Values          | int V[]  | one per variable           |

| Counter Values           | int C[]  | one per counted occurrence |

| Exception Presence Flags | char E[] | one per exception          |

| Exception Values         | int EV[] | one per valued exception   |

Table 4.1: List of all runtime data structures.

The size of each of these is determined at compile time.

| name        | use                                        |

|-------------|--------------------------------------------|

| %g0         | Always zero                                |

| %00         | Temporary                                  |

| %o1         | Temporary                                  |

| %10         | r0                                         |

| %11         | r1                                         |

| :           | ÷                                          |

| %17         | r7                                         |

| <b>%i</b> 2 | Returned program counter                   |

| %i3         | Returned potential set calculation routine |

| %i4         | Returned status $(-1,0,1)$                 |

| %i5         | Base address of arrays                     |

Table 4.2: Register usage for the SPARC processor.

means "take the low-order bits of the address of \_V, an array, add twelve, and add this to the register %i5". %i5 contains the base address of the arrays, so this refers to the 12th byte of the \_V array. Such a scheme allows for a small, limited amount of data, but this has not presented a problem thus far.

#### 4.4.1 Assignment Statements

Simple assignment instructions translate into single instructions:

• A memory load instruction (array to register). e.g.,

r0 := v1  $\rightarrow$  ld [%i5+%lo(\_V+4)],%l0

- A memory store instruction (register to array)

- v3 := r1 → st %l1,[%i5+%lo(\_V+12)]

- A constant load (constant to register)

r2 := 5  $\rightarrow \text{mov } 5,\%$ 12

Assignment instructions with unary and binary operands only reference registers, so most translate to single instructions:

| r0 := not r1  | $\rightarrow$ xnor | 7 %g0,%l1,%l0 |

|---------------|--------------------|---------------|

| r1 := r2 + r3 | $\rightarrow$ add  | %12,%13,%11   |

The comparison operators use the SPARC's annul flag, which cancels the execution of the instruction in the branch delay slot if the branch is not taken. If the branch is taken, 1 is loaded, otherwise 0 is loaded.

#### 4.4.2 Flow-of-Control Statements

Each instruction is given a label like P5I3, which refers to instruction 3 of process 5.

• Unconditional branches translate directly.

ba POI1 goto 1  $\rightarrow$ nop • A register test translates to if r1 goto 5 tst %l1  $\rightarrow$ bne P3I5 nop • A signal presence test translates to if not s1 goto 3  $\rightarrow$  ldsb [%i5+%lo(\_S+1)],%o0 tst %00 bneg P2I3 nop

4.4.3 emit

```

emit simply stores the signal value, if any, and sets the signal to present:

emit s2 r1 → st %l1, [%i5+%lo(_SV+8)] ! store value

mov 1,%o0

stb %o0, [%i5+%lo(_S+2)] ! set to present

```

#### 4.4.4 exit

An exit with an exception stores the exception value, if any, raises its exception, sets the return PC to branch to the same exit instruction, and sets the return potential set routine to null. It then "returns" to the try instruction which called it, returning the halted status.

Returning the halted status in this case is done to get around a technical point. If all other processes were also to terminate, the innermost enclosing **try** would execute first. Since this **try** may *not* be watching for the given exception (i.e., another further out would be), it may erroneously execute further instructions. The halted status prevents this possibility and since we can be assured that some enclosing try is watching for the exception, it will be handled.

```

exit e1 r0 \rightarrow st %10,[%i5+%10(_EV+4)] ! store value

mov 1,%00 ! set to raised

stb %00,[%i5+%10(_E+1)]

LL1:

set LL1, %i2 ! Return PC

set PO1, %i3 ! Return PO

ba PR1

or %i4, 1 , %i4 ! return HALTED

```

When the **exit** does not refer to an exception, the generated code is similar, except that the terminated status is returned (implicitly) instead of the halted status.

```

exit → LL1:

set LL1, %i2 ! Return PC

set PO1, %i3 ! Return PO

ba PR1

nop

```

## 4.4.5 halt

halt is much like an exit. Naturally, the halted status is returned. halt → LL2: set LL2, %i2 ! Return PC set PO2, %i3 ! Return PO ba PR2 or %i4, 1, %i4 ! return HALTED

### 4.4.6 Require

**require** may force a process to return with the waiting status. First, it checks its signals and if none are unknown, it branches to the next instruction. Otherwise, it returns with the waiting status and returns a potential set calculation routine that marks those signals can be emitted.

```

1:

require s2 s3

\rightarrow

! check signals s2 and s3

2:

emit s0

POI1:

3:

emit s1

ldsb [%i5+%lo(_S+2)],%o0

tst %00

be LLO

ldsb [%i5+%lo(_S+3)],%o0

tst %00

be POI2

nop

! Return waiting

LLO:

set POI1,%i2 ! PC

set LL1,%i3 ! potential

ba PRO

or %i4,-1,%i4 ! return waiting

! Potential set calculator

! marks s0 and s1 as having potential

LL1:

stb %g0,[%i5+%lo(_P+0)]

stb %g0,[%i5+%lo(_P+1)]

ba POO

nop

1

! Code for emit

POI2:

÷

```

The potential set calculation for the **require** instruction is static, since we know which segments of code (in particular, the *first* instructions of the subprocesses of every **try**) may be executed in the current instant.

## 4.5 The try Instruction

try is the most complex of all the intermediate instructions, being responsible for parallel execution, preemption, and exception handling. Because of this, it also has significant responsibilities related to the potential set.

A try instruction's behavior changes with time. For example, it examines any watched signals only after the first instant. The change is accomplished by returning different program counters (i.e., not always pointing to the beginning of the code for the try) as appropriate, and through the use of the halt array.

Most of the information a try instruction needs is available at compile time. For example, it will always check the same signals and exceptions. This makes for very simple, loop-free code in the executable. A try instruction has the following structure:

$\mathbf{PC}_i \dots \mathbf{PC}_j = 0$ initialize subprocess program counters  $\mathbf{E}_k \ldots \mathbf{E}_l = 0$ lower our exceptions repeat A : waiting for processes to run call  $PC_i \dots PC_j$ call each of the subprocesses if any processes returned waiting a process has not completed return waiting, PC = Aif any exception was raised check the exceptions after completion branch to its handler if any process returned halted process is done for this instant, return halted. PC = Bbut is still active branch to the next instruction all subprocesses have terminated B: waiting for watching signals if this process has been halted halted in this instant **return** halted, PC = Bif any watched signals are unknown need to know about all **return** waiting, PC = Bwatched signals before proceeding decrement the counter of any counted occurrence whose signal is present if any occurrence elapsed counter became zero, or branch to its handler simple occurrence's signal present end repeat

end repeat

The full potential-set calculator routine for a try is much more elaborate than that used by require:

if process is not halted

call  $PO_i \dots PO_j$  potential set routines of subprocesses mark potential set of each watch handler mark potential set of each exception handler mark potential set of next instruction return

## 4.6 Example

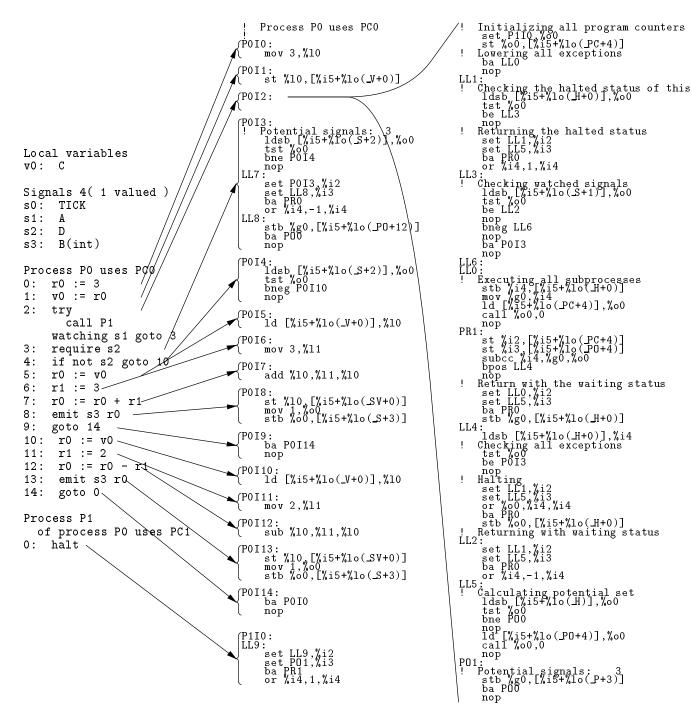

The SPARC translation of the program of Figure 3.1 on page 30 is shown in Figure 4.1 on page 41. The assembly code for the **try** instruction has been placed in the second column for clarity.

Each instruction is given a label such as  $\tt POI1,$  which indicates process zero, instruction one.

Figure 4.1: The translation of the Esterel program of Figure 3.1 from page 30.

The potential-set calculator routine for the try starting at LL5 first checks the status of the halted flag for the process, returning immediately if it is set, indicating that the process has halted. In this case, since the process has halted, it cannot emit any more signals in the current instant. However, at the beginning of the next instant, the halted flag will be cleared and when the potential set calculator is called again (even before it is known that the process can be executed), the potential set will be calcuated assuming that the process could be executed.

Because each subprocess can be called from exactly one try instruction, the return address of each subprocess is known at compile time. In this example, for instance, process P1 is called from the try in process P0. The return address of process P1 is given the label PR1. Similarly, the potential set calculator for process P1 is called from exactly one point, so its return address is explicit: P01.

## 4.7 Outer Loop

The outer loop calls the outermost process routine and its potential set calculator repeatedly to compute the program's response for an instant. The outer loop performs the following actions:

$\mathtt{H}_0\ldots\mathtt{H}_n:=0$ clear all halted flags  $S_0 \dots S_m := 0$ mark all signals as unknown  $S_i \dots S_j := 1$  or -1 as appropriate mark all input signals as present or absent repeat  $\mathbf{P}_0 \dots \mathbf{P}_l = 0$ mark signals as having no potential call PCO outermost process routine foreach signal i signal is unknown and has no potential if  $S_i = 0$  and  $P_i = 0$ mark signal as absent  $S_i = -1$ until outermost process routine returned halted

42

## Chapter 5

# Causality

In Esterel, as in any language, it is possible to write something nonsensical. Possible errors include the simple syntax error (misspelling a keyword, for example), and more elaborate semantic errors (e.g., trying to add an integer or a boolean, emitting an input-only signal, etc.). In Esterel, there is the fairly subtle concept of causality which can be violated.

A simple example of a causality error is the following paradox

#### present A else emit A end

Because of the instantaneous semantics of Esterel, this fragment means that if the signal **A** is absent in an instant, then it should be emitted in that instant, which is clearly nonsense since a signal is either present or absent, never both. Another, more common mistake is to make a do...watching preempt itself. For example,

do await A ; emit B ; emit C watching C

When A arrives, B and C are emitted in the same instant. However, when C is emitted, the enclosed instruction is not executed (the semantics of the do), so C could not have been emitted. (A way to get around this particular problem is to replace the do...watching with a trap instruction.)

These two errors would be fairly easy to catch at compile time—the rule is that any instruction whose execution depends on a signal cannot emit that signal. However, manifestation of these sorts of errors can be arbitrarily subtle. Consider the following sequence

```

await B ; present A else emit C end

||

await C ; emit D

||

await D ; emit E

||

await E ; emit A

```

Here, when B arrives, C is emitted if A is present. However, A is emitted if E is present, and E is emitted if D is present, and D is emitted if C is present. It is subtle, but this is the same sort of paradox as present A else emit A end.

To illustrate how subtle such violations can be, consider the following variation on this code:

```

await B ; present A else emit C end

||

await B ; await C ; emit D

||

await D ; emit E

||

await E ; emit A

```

This does *not* constitute a causality violation. Assuming B is the only input signal, when B occurs, D cannot be emitted because the **await** C will only start looking for C in the *next* instant. Thus, D is not emitted, so E and A are not emitted, so C is.

However, by adding one keyword, the fragment again becomes non-causal:

```

await B ; present A else emit C end

||

await B ; await immediate C ; emit D

||

await D ; emit E

||

await E ; emit A

Here is another paradox:

every A do

present C then emit D end

end

||

every A do

present D else emit C end

end

```

Here, when A is present, the first line says that C implies D, but the second says D implies not C, which is paradoxical.

However, the data-dependent actions make the problem even more subtle. Consider

```

var i := 0 : integer in

every A do

i := i + 1 ;

emit B(i)

end

every B do

if ?B mod 2 = 1 then

present C then emit D end

end

end

every B do

if ?B mod 2 = 0 then

present D else emit C end

end

end

end

```

This is actually causal since it is impossible for both ?B mod 2 = 0 and ?B mod 2 = 1 to be true in the same instant (the value returned by ?B is unique to an instant).<sup>1</sup>

So in general, exact causality checking is impractical. The Esterel V3 compiler simulates only the signal portion of the program as part of the compilation process (i.e., not the data portion), which accounts for its rapidly-growing compilation times. It can detect causality violations, but it is conservative and it requires excessively long compilation times.

Some causality checking is necessary, but the conservative approach taken by the Esterel V3 compiler requires too much time to perform.

<sup>&</sup>lt;sup>1</sup>Unsurprisingly, the Esterel V3 compiler flags this example as noncausal.

## Chapter 6

# **Results and Conclusions**

The compiler presented in this report was tested on the lengthy example (and variations thereon) presented in appendix C. For comparison, it was also tested with the production Esterel V3 compiler supported by CISI INGENIERIE[8]. These results are shown in Tables 6.1 and 6.2 on pages 47 and 47.

The examples watch1, watch2, watch3, and watch4 are stripped-down versions of the complete watch example, containing the first one, two, three, and four submodules respectively.

## 6.1 Results for The Esterel V3 Compiler

Please refer to Table 6.1. With the Esterel V3 compiler, the number of states in the finite-state machine starts small, but grows quickly with the size of the input file. The length of the *ic* file, which contains an intermediate representation similar to the one used here, is growing roughly linearly with the length of the input file, as is to be expected. However, the length of the *oc* file, which contains a description of the state machine used to produce the C source, is growing very rapidly—exponentially for this example.

The C source file produced is roughly the same size as the oc file, so the system's C compiler is presented with a challenge: C source files no smaller than 980K. Not surprisingly, the time required to produce the C source file is rapidly getting out of hand, starting at a minute and increasing by about a factor of four for each 200-line increase in the length of the source file.

The size of the executable produced by this compiler tracks the size of the C source file, and is also growing very rapidly. The one consolation is that the time required to simulate one thousand clock ticks is both small and growing slowly.

|                                                                                               | watch1 | watch2 | watch3 | watch4  | watch |

|-----------------------------------------------------------------------------------------------|--------|--------|--------|---------|-------|

| lines in source file                                                                          | 297    | 467    | 619    | 823     | 998   |

| number of states                                                                              | 7      | 22     | 32     | 128     | >206  |

| length of ic file (kilobytes)                                                                 | 16     | 25     | 35     | 45      | 52    |

| length of oc file (megabytes)                                                                 | 0.98   | 5.42   | 18.7   | 190     | >236  |

| time to create C source file (mm:ss)                                                          | 0:52   | 4:43   | 15:57  | >37:00† |       |

| time to compile C source (mm:ss)                                                              | 1:50   | 15:30  | 18:43† |         |       |

| size of MIPS executable (megabytes)                                                           | 0.87   | 3.7    | 12.2   |         |       |