# Hardware Acceleration of Market Order Decoding

Amandeep Chhabra, Adil Sadik, Manu Dhundi, Prabhat Godse

#### Outline

- What is Hardware Acceleration of Market Order Decoding (HAMOD)

- Motivation

- System Overview

- Hardware

- Read/Write, Multiplexer

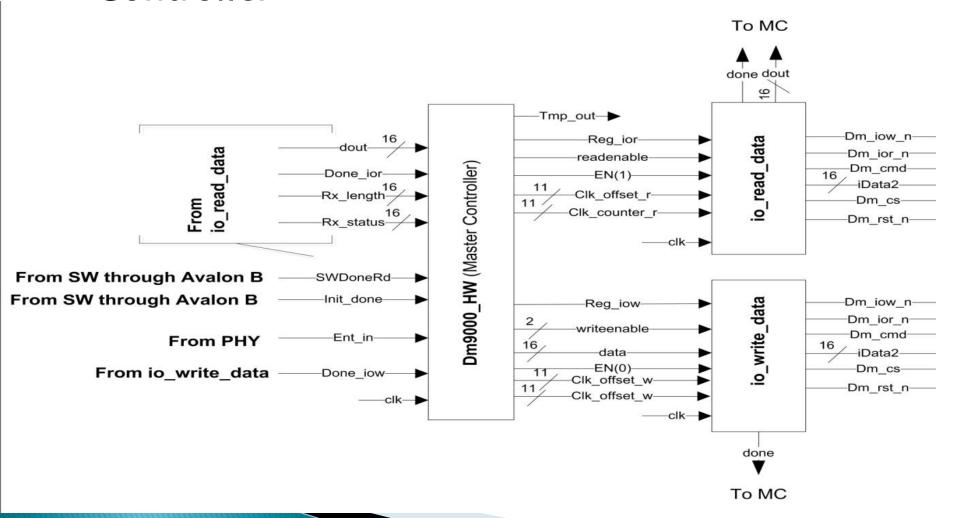

- Controller

- Software

- Results

- Acknowledgement

#### What is a HAMOD

- Accelerate the reading of Market Order Data using FPGA.

- Decrease the latency involved in reading data from Ethernet.

- Market data order similar to NASDAQ standard.

- UDP packets.

- Software processes orders and makes sample deals.

#### **Motivation**

- Low latency network systems

- Application in finance

- Data Centers

- Reconfigurable hardware systems

- Application in current industry.

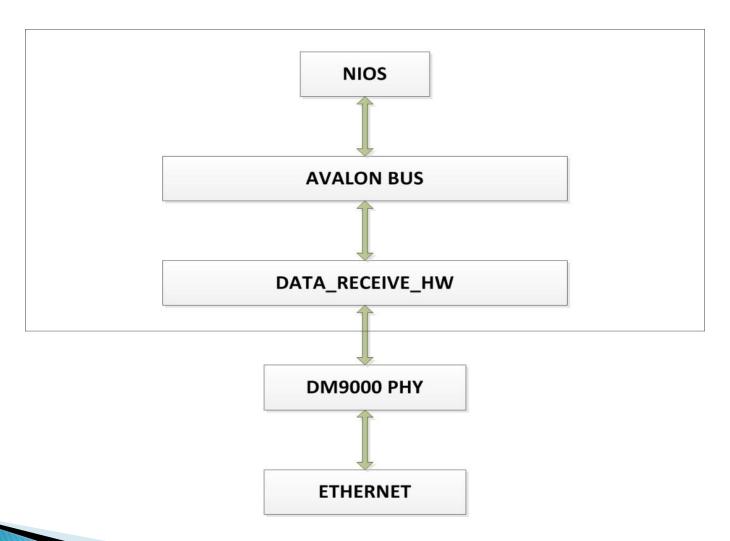

# System

System

NIOS

**AVALON BUS**

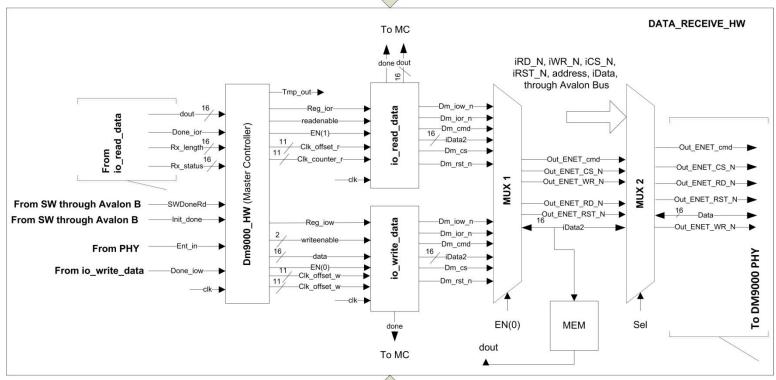

iRD\_N, iWR\_N, iCS\_N, iRST\_N, address, iData,

## System

#### Hardware

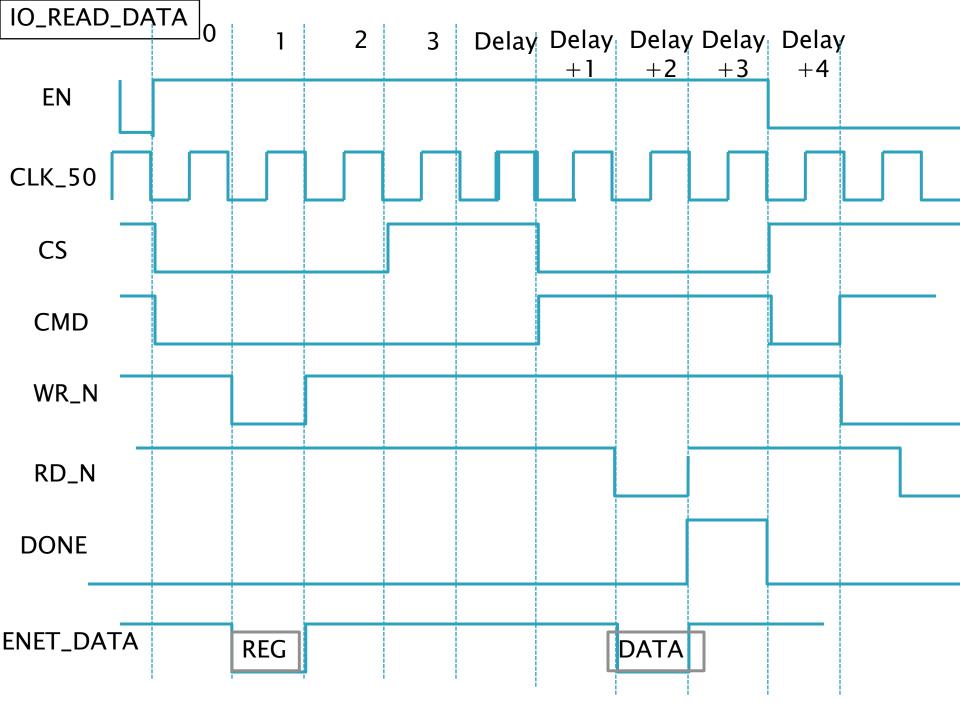

- ▶ IO\_Read with timing Diagram

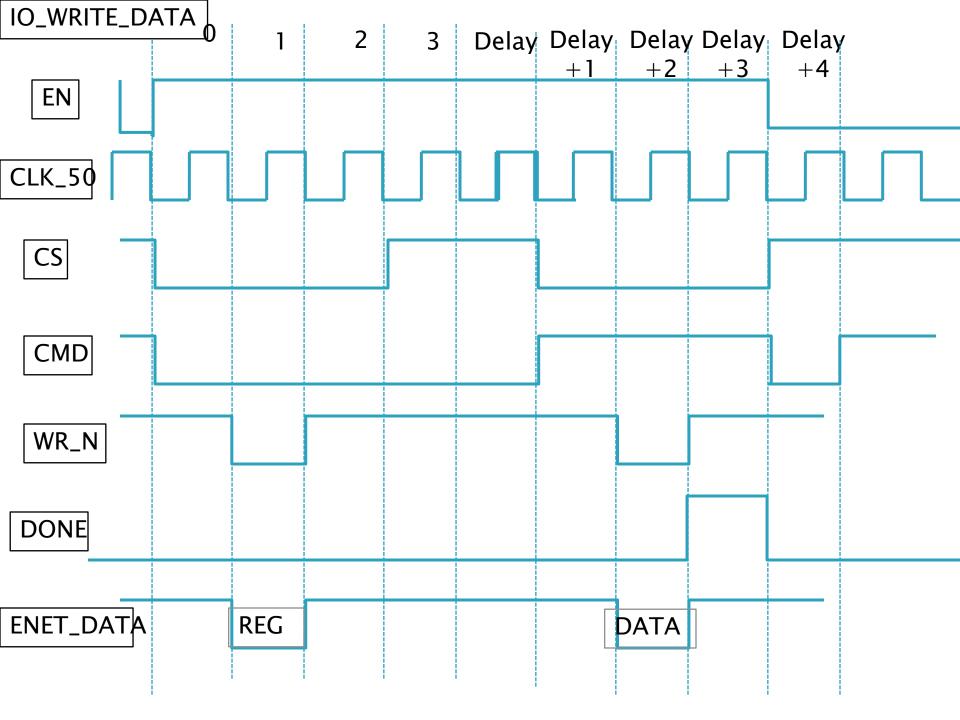

- ▶ IO\_Write with timing Digram

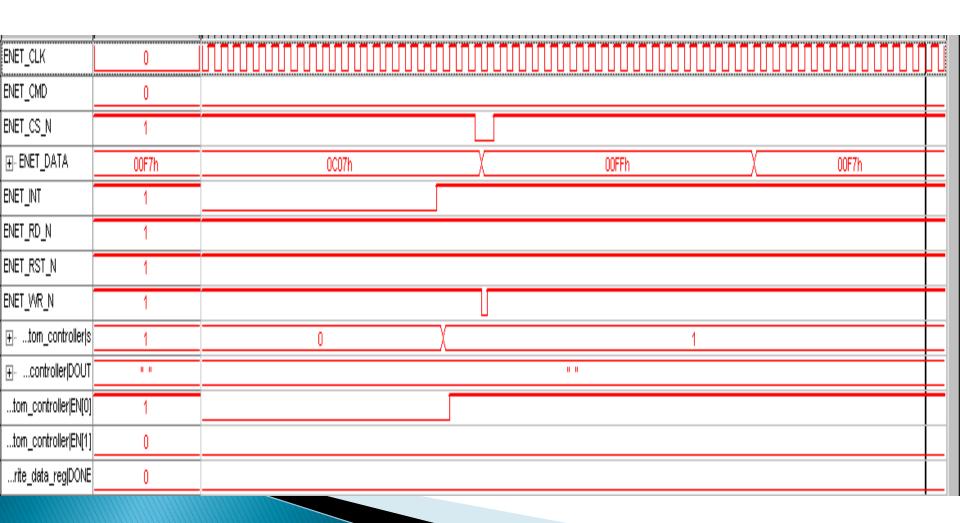

# SignalTap Analyzer

## Hardware(conti)

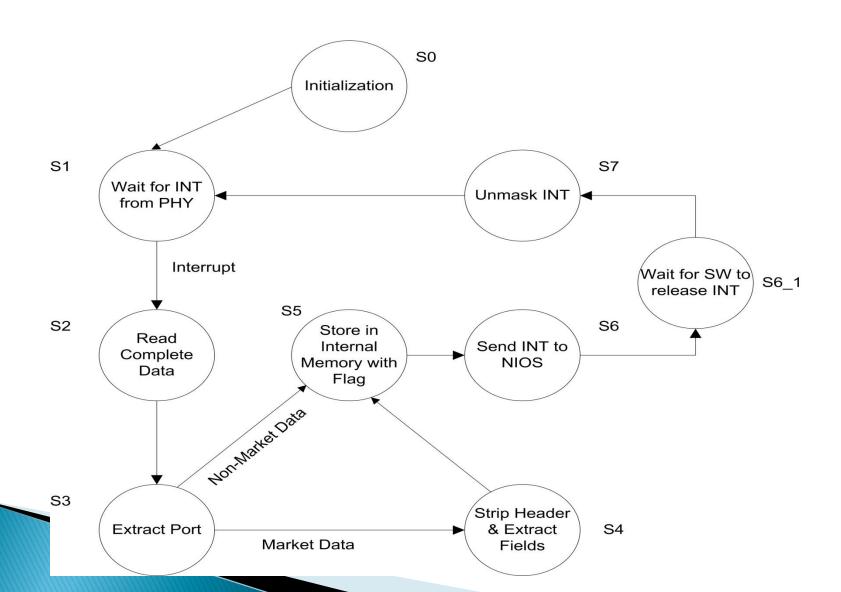

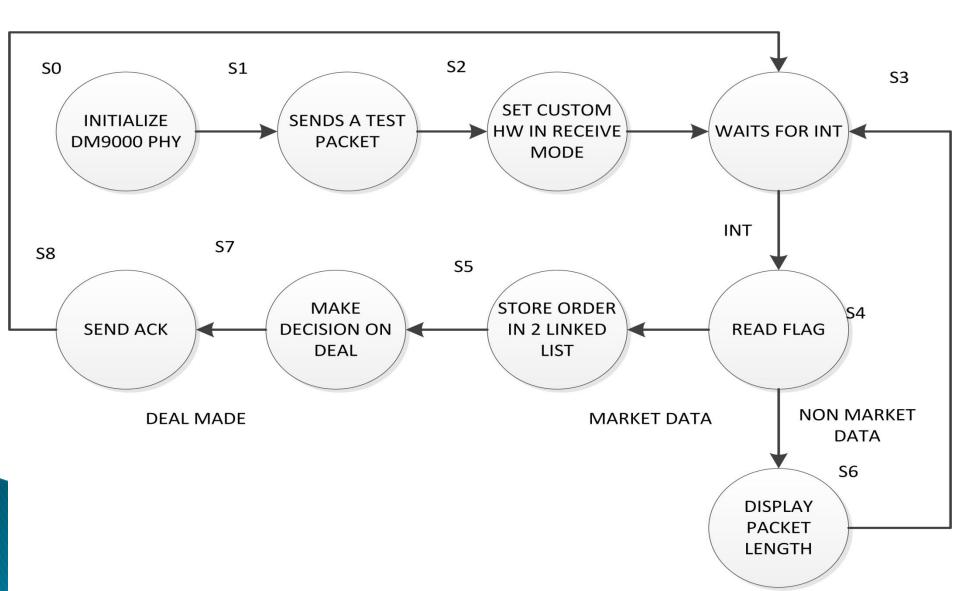

Controller

### Software

## Result/Performance Benchmark

- Successfully receive Market Order Packet and Extract the fields.

- Clock Cycles for HW read and decode=982

- Clock Cycles for HW + SW read and decode: 14562

- Clock Frequency 50MHz

- We are off-course better than lab2.

#### Hurdles

- On-chip debugging

- Interrupt management

- Software Memory Constraints

- Poor documentation of DM9000a PHY

## Special Thanks

- Professor Stephen Edwards

- David Lariviere (TA)

## Questions

???