# **Quartus II Version 7.2 Handbook Volume 1: Design and Synthesis**

101 Innovation Drive San Jose, CA 95134 www.altera.com

Copyright © 2007 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in

formation and before placing orders for products or services.

ii Altera Corporation

# **Contents**

|                                                                                                   | vii  |

|---------------------------------------------------------------------------------------------------|------|

| About this Handbook xv                                                                            | .vii |

| How to Contact Alterax                                                                            |      |

| Third-Party Software Product Informationx                                                         |      |

| Typographic Conventionsxv                                                                         |      |

|                                                                                                   |      |

| Section I. Design Flows                                                                           |      |

| Chapter 1. Design Planning with the Quartus II Software                                           | 1 1  |

| Introduction                                                                                      | 1-1  |

| Device and Programming/ Configuration Method Selection                                            | 1 2  |

| Device Selection                                                                                  |      |

| Device Migration Planning                                                                         |      |

| Programming/Configuration Method Selection                                                        | 1_4  |

| Early Planning Tools for Power and I/O                                                            | 1–5  |

| Early Power Estimation                                                                            |      |

| Early Pin Planning and I/O Analysis                                                               |      |

| Selecting Third-Party EDA Tool Flows                                                              |      |

| Synthesis Tools                                                                                   |      |

| Simulation Tools                                                                                  | -10  |

| Formal Verification Tools 1–                                                                      | -10  |

| Planning for On-Chip Debugging Options 1-                                                         | -11  |

| Planning for an Incremental Compilation Flow1-                                                    | -13  |

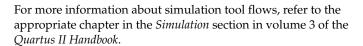

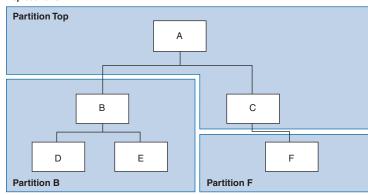

| Flat Compilation Flow with No Design Partitions 1-                                                |      |

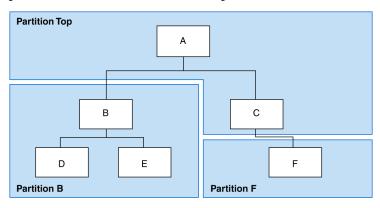

| Incremental Compilation with Design Partitions 1-                                                 |      |

| Top-Down Versus Bottom-Up Incremental Flows 1-                                                    |      |

| Planning Design Partitions 1-                                                                     |      |

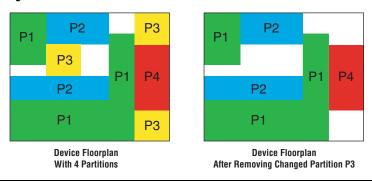

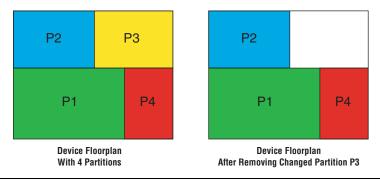

| Creating a Design Floorplan1-                                                                     |      |

| Early Timing Estimation                                                                           |      |

| Conclusion1-                                                                                      |      |

| Referenced Documents                                                                              |      |

| Document Revision History 1-                                                                      |      |

| Chapter 2. Quartus II Incremental Compilation for Hierarchical and Team-Based Design Introduction |      |

| Choosing a Quartus II Compilation Flow                                                            |      |

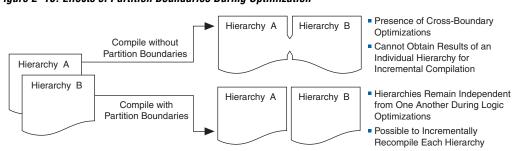

| Flat Compilation Flow with No Design Partitions                             | 2–3  |

|-----------------------------------------------------------------------------|------|

| Incremental Compilation Flow with Design Partitions                         | 2–5  |

| Top-Down versus Bottom-Up Compilation Flows                                 | 2–9  |

| Quick Start Guide - Summary of Steps for an Incremental Compilation Flow    | 2–11 |

| Top-Down Incremental Compilation Flow                                       | 2–11 |

| Bottom-Up Incremental Compilation                                           | 2–13 |

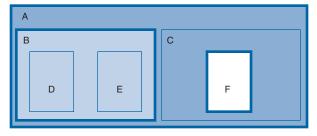

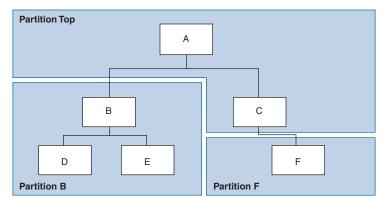

| Design Partitions                                                           | 2–17 |

| Design Partition Assignments Compared to Physical Placement Assignments     | 2–18 |

| Creating Design Partitions                                                  | 2–19 |

| Partition Name                                                              |      |

| Setting the Netlist Type for Design Partitions                              |      |

| Fitter Preservation Level                                                   |      |

| Empty Partitions                                                            |      |

| What Represents a Source Change for Incremental Compilation?                | 2–27 |

| Creating a Design Floorplan With LogicLock Location Assignments             | 2–29 |

| Taking Advantage of the Early Timing Estimator                              | 2–31 |

| Exporting and Importing Partitions for Bottom-Up Design Flows               | 2–32 |

| Quartus II Exported Partition File (.qxp)                                   | 2–32 |

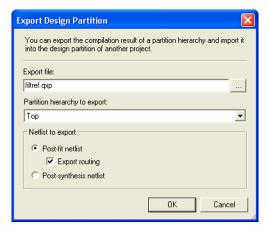

| Exporting a Lower-Level Partition to be Used in a Top-Level Project         | 2–33 |

| Exporting a Lower-Level Block within a Project                              | 2–35 |

| Importing a Lower-Level Partition Into the Top-Level Project                | 2–36 |

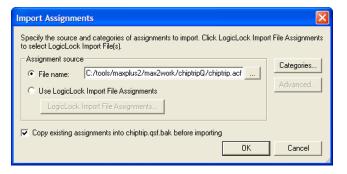

| Importing Assignments and Advanced Import Settings                          |      |

| Generating Bottom-Up Design Partition Scripts for Project Management        | 2–40 |

| Guidelines for Creating Good Design Partitions and LogicLock Regions        | 2–46 |

| Creating Good Design Partitions                                             | 2–47 |

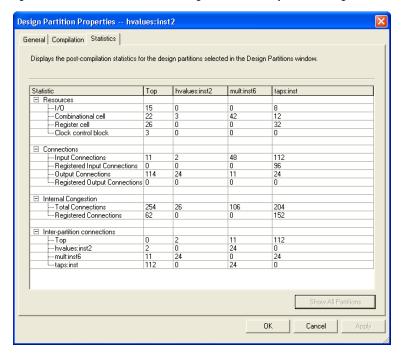

| Partition Statistics Reports                                                |      |

| Resource Balancing                                                          | 2–51 |

| Timing Budgeting                                                            |      |

| Methodology to Check Partition Quality during Partition Planning            |      |

| The Importance of Floorplan Location Assignments in Incremental Compilation |      |

| Creating Good Floorplan Location Assignments                                | 2–57 |

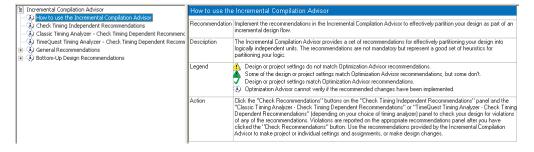

| Incremental Compilation Advisor                                             |      |

| Criteria for Successful Partition and Floorplan Schemes                     |      |

| Recommended Design Flows and Compilation Application Examples               |      |

| Top-Down Incremental Design Flows                                           |      |

| Bottom-Up Incremental Design Flows                                          |      |

| Incremental Compilation Restrictions                                        | 2–76 |

| Using Incremental Synthesis Only Instead of Full Incremental Compilation    |      |

| Preserving Exact Timing Performance                                         | 2–77 |

| Using Incremental Compilation with Quartus II Archive Files                 |      |

| Formal Verification Support                                                 | 2–78 |

| OpenCore Plus MegaCore Functions in Bottom-Up Flows                         |      |

| Importing Encrypted IP Cores in Bottom-Up Flows                             | 2–78 |

| SignalProbe Pins and Engineering Change Management with the Chip Planner    |      |

| SignalTap II Embedded Logic Analyzer in Bottom-Up Compilation Flows         |      |

| Logic Analyzer Interface in Bottom-Up Compilation Flows                     |      |

| Migrating Projects with Design Partitions to Different Devices              | 2–81 |

iv Altera Corporation

| HardCopy Compilation Flows                                                  | 2–82                 |

|-----------------------------------------------------------------------------|----------------------|

| Assignments Made in HDL Source Code in Bottom-Up Flows                      | 2–83                 |

| Compilation Time with Physical Synthesis Optimizations                      | 2–83                 |

| Restrictions on Megafunction Partitions                                     | 2–84                 |

| Routing Preservation in Bottom-Up Compilation Flows                         | 2–84                 |

| Bottom-Up Design Partition Script Limitations                               | 2–84                 |

| Register Packing and Partition Boundaries                                   | 2–87                 |

| I/O Register Packing                                                        | 2–87                 |

| Scripting Support                                                           | 2–99                 |

| Generate Incremental Compilation Tcl Script Command                         | 2–99                 |

| Preparing a Design for Incremental Compilation                              | 2–100                |

| Creating Design Partitions                                                  |                      |

| Setting Properties of Design Partitions                                     | 2–101                |

| Creating Good Floorplan Location Assignments—Excluding or Filtering Certain | n Device             |

| Elements (Such as RAM or DSP Blocks)                                        | 2–102                |

| Generating Bottom-Up Design Partition Scripts                               | 2–103                |

| Exporting a Partition to be Used in a Top-Level Project                     | 2–105                |

| Importing a Lower-Level Partition into the Top-Level Project                | 2–106                |

| Makefiles                                                                   | 2–106                |

| Recommended Design Flows and Compilation Application Examples               | 2–107                |

| Conclusion                                                                  | 2–109                |

| Referenced Documents                                                        | 2–109                |

| Document Revision History                                                   | 2–111                |

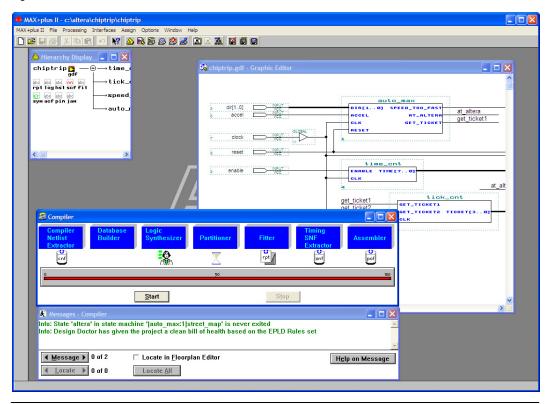

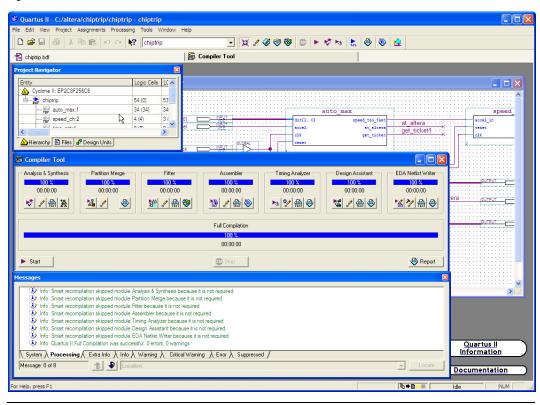

| Chapter 3. Quartus II Design Flow for MAX+PLUS II Users Introduction        | 3–1                  |

| Chapter Overview                                                            | 3–1                  |

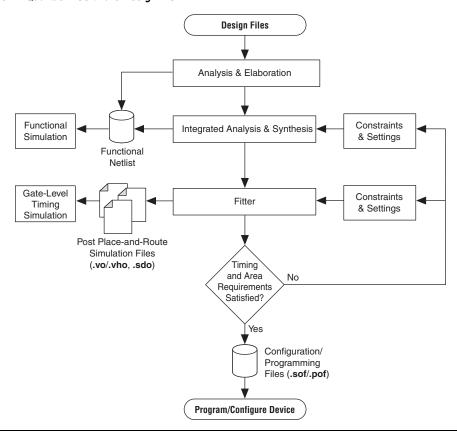

| Typical Design Flow                                                         | 3–2                  |

| Device Support                                                              | 3–3                  |

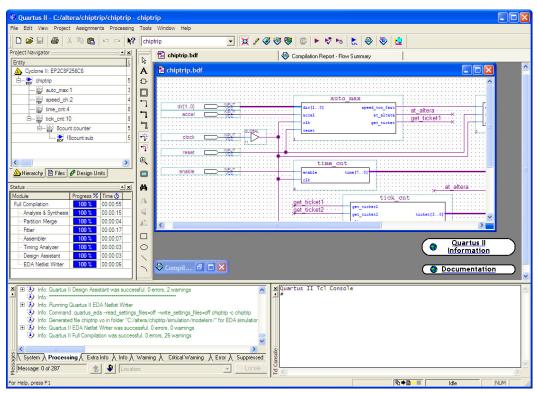

| Quartus II GUI Overview                                                     |                      |

| Project Navigator                                                           |                      |

| Node Finder                                                                 |                      |

| Tcl Console                                                                 |                      |

| Messages                                                                    |                      |

| Status                                                                      |                      |

| Setting Up MAX+PLUS II Look and Feel in Quartus II                          | 3–6                  |

| MAX+PLUS II Look and Feel                                                   |                      |

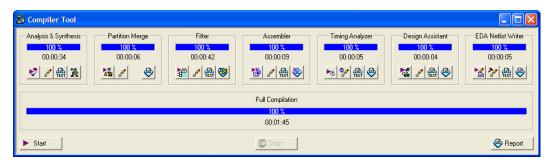

| Compiler Tool                                                               |                      |

| Analysis and Synthesis                                                      |                      |

| Partition Merge                                                             |                      |

| Fitter                                                                      |                      |

| Assembler                                                                   |                      |

| Timing Analyzer                                                             | 0 11                 |

| ED A Natiat Maitan                                                          |                      |

| EDA Netlist Writer                                                          | 3–11                 |

| Design Assistant                                                            | 3–11<br>3–11         |

|                                                                             | 3–11<br>3–11<br>3–12 |

Altera Corporation

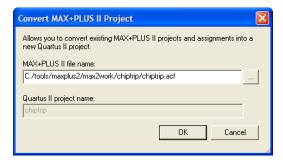

| Converting MAX+PLUS II Graphic Design Files                        | 3–13 |

|--------------------------------------------------------------------|------|

| Importing MAX+PLUS II Assignments                                  | 3–14 |

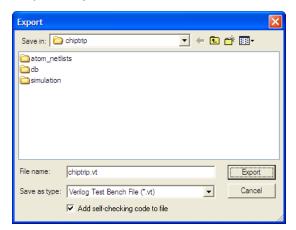

| Quartus II Design Flow                                             | 3–15 |

| Creating a New Project                                             | 3–16 |

| Design Entry                                                       | 3–16 |

| Making Assignments                                                 |      |

| Synthesis                                                          | 3–23 |

| Functional Simulation                                              | 3–24 |

| Place and Route                                                    | 3–26 |

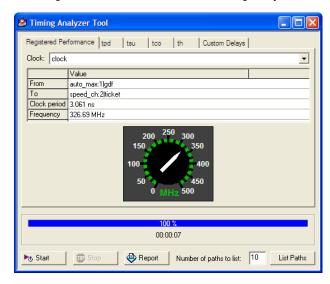

| Timing Analysis                                                    | 3–27 |

| Timing Closure Floorplan                                           | 3–29 |

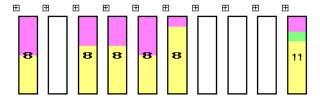

| Timing Simulation                                                  | 3–31 |

| Power Estimation                                                   | 3–33 |

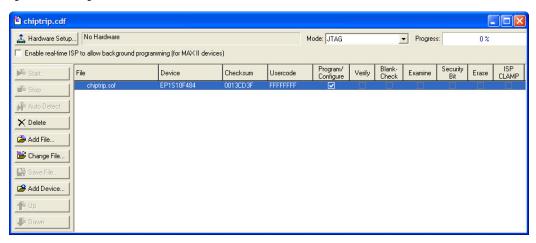

| Programming                                                        | 3–33 |

| Conclusion                                                         | 3–34 |

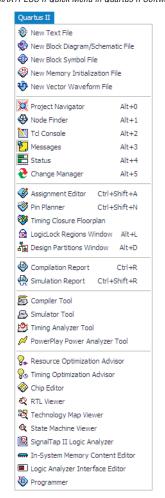

| Quick Menu Reference                                               | 3–35 |

| Quartus II Command Reference for MAX+PLUS II Users                 | 3–36 |

| Referenced Documents                                               |      |

| Document Revision History                                          | 3–46 |

| •                                                                  |      |

| Chapter 4. Quartus II Support for HardCopy Series Devices          |      |

| Introduction                                                       | 4–1  |

| HardCopy II Device Support                                         |      |

| HardCopy II Design Benefits                                        |      |

| Quartus II Features for HardCopy II Planning                       |      |

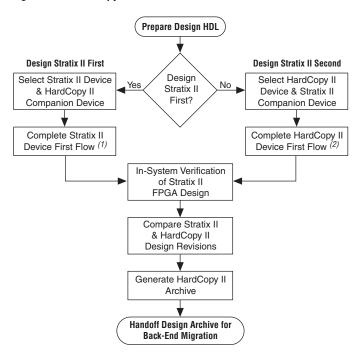

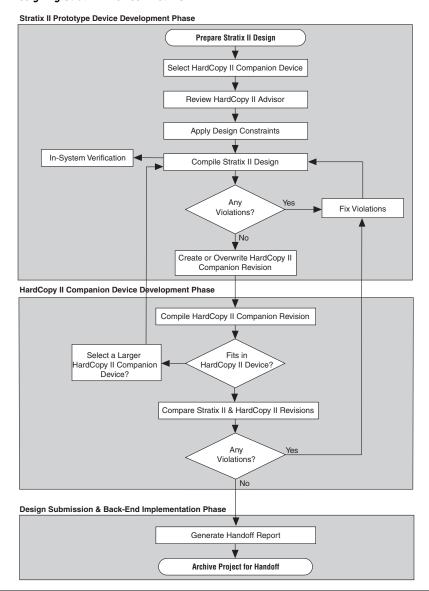

| HardCopy II Development Flow                                       | 4–3  |

| Designing the Stratix II FPGA First                                |      |

| Designing the HardCopy II Device First                             |      |

| HardCopy II Device Resource Guide                                  |      |

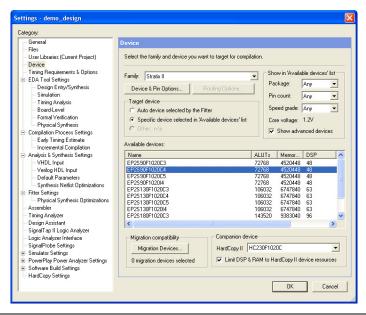

| HardCopy II Companion Device Selection                             |      |

| HardCopy II Recommended Settings in the Quartus II Software        |      |

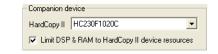

| Limit DSP and RAM to HardCopy II Device Resources                  |      |

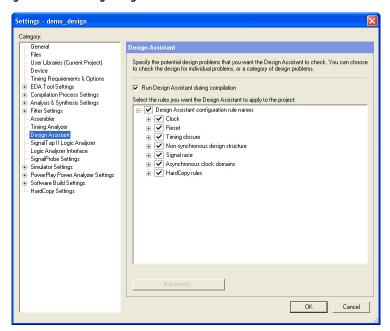

| Enable Design Assistant to Run During Compile                      |      |

| Timing Settings                                                    |      |

| Constraints for Clock Effect Characteristics                       |      |

| Quartus II Software Features Supported for HardCopy II Designs     |      |

| Performing ECOs with Quartus II Engineering Change Management with |      |

|                                                                    |      |

| Migrating One-to-One Changes                                       |      |

| Migrating Changes that Must be Implemented Differently             |      |

| Changes that Cannot be Migrated                                    |      |

| Overall Migration Flow                                             |      |

| Preparing the Revisions                                            |      |

| Applying ECO Changes                                               |      |

| Formal Verification of Stratix II and HardCopy II Revisions        |      |

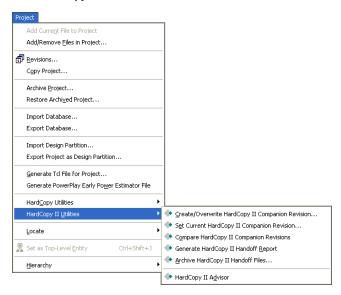

| HardCopy II Utilities Menu                                         |      |

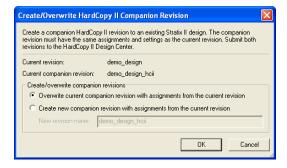

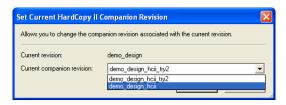

| Companion Revisions                                                |      |

| Compiling the HardCopy II Companion Revision                       |      |

|                                                                    |      |

vi Altera Corporation

| Comparing HardCopy II and Stratix II Companion Revisions            | 4–28         |

|---------------------------------------------------------------------|--------------|

| Generate a HardCopy II Handoff Report                               |              |

| Archive HardCopy II Handoff Files                                   | 4–29         |

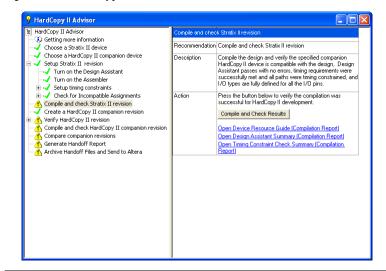

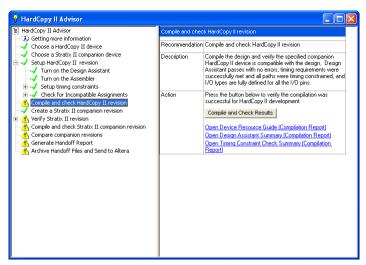

| HardCopy II Advisor                                                 | 4–30         |

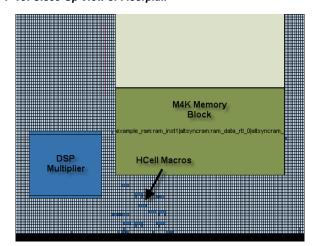

| HardCopy II Floorplan View                                          |              |

| HardCopy Stratix Device Support                                     | 4–34         |

| Features                                                            |              |

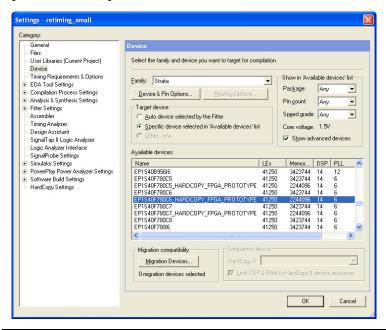

| HARDCOPY_FPGA_PROTOTYPE, HardCopy Stratix and Stratix Devices       | 4–36         |

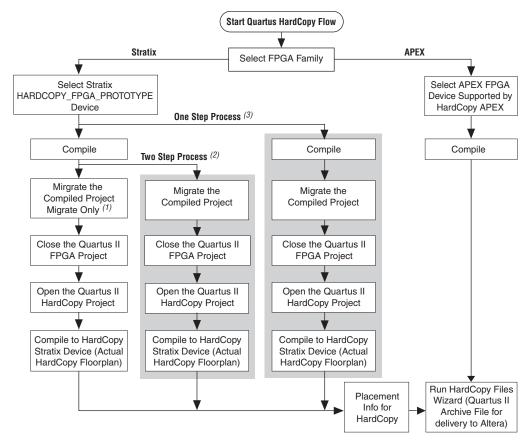

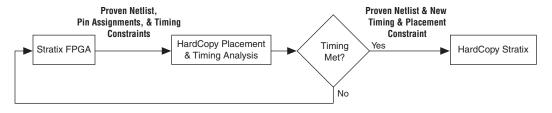

| HardCopy Design Flow                                                |              |

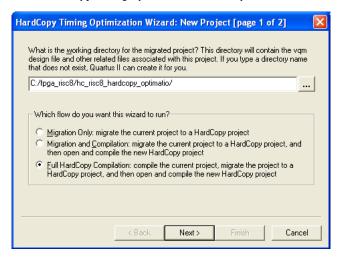

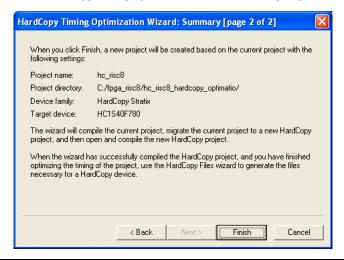

| The Design Flow Steps of the One-Step Process                       | 4–39         |

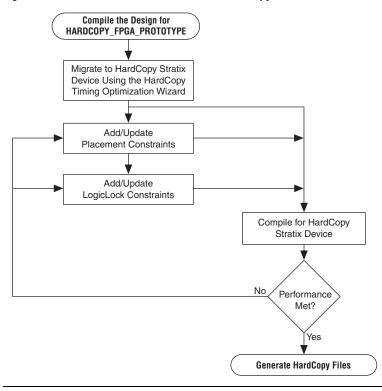

| How to Design HardCopy Stratix Devices                              | 4–40         |

| Tcl Support for HardCopy Migration                                  |              |

| Design Optimization and Performance Estimation                      |              |

| Design Optimization                                                 |              |

| Performance Estimation                                              | 4–45         |

| Buffer Insertion                                                    |              |

| Placement Constraints                                               | 4–48         |

| Location Constraints                                                |              |

| LAB Assignments                                                     | 4–49         |

| LogicLock Assignments                                               |              |

| Checking Designs for HardCopy Design Guidelines                     |              |

| Altera-Recommended HDL Coding Guidelines                            | 4–51         |

| Design Assistant                                                    |              |

| Reports and Summary                                                 |              |

| Generating the HardCopy Design Database                             |              |

| Static Timing Analysis                                              |              |

| Early Power Estimation                                              |              |

| HardCopy Stratix Early Power Estimation                             |              |

| HardCopy APEX Early Power Estimation                                |              |

| Tcl Support for HardCopy Stratix                                    | 4–56         |

| Targeting Designs to HardCopy APEX Devices                          |              |

| Conclusion                                                          |              |

| Referenced Documents                                                |              |

| Document Revision History                                           | 4–59         |

|                                                                     |              |

|                                                                     |              |

| Section II. Design Guidelines                                       |              |

|                                                                     |              |

| Chapter 5. Design Recommendations for Altera Devices and the Quarte | us II Design |

| Assistant                                                           | _            |

| Introduction                                                        | 5–1          |

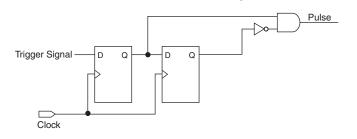

| Synchronous FPGA Design Practices                                   |              |

| Fundamentals of Synchronous Design                                  |              |

| Hazards of Asynchronous Design                                      |              |

| Design Guidelines                                                   |              |

| Combinational Logic Structures                                      |              |

| 0                                                                   |              |

Altera Corporation vii

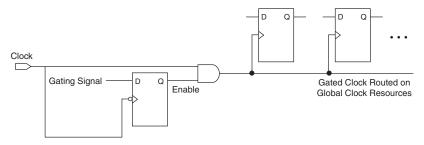

| Clocking Schemes                                                            | 5–9  |

|-----------------------------------------------------------------------------|------|

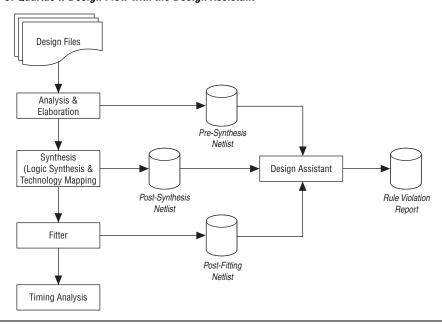

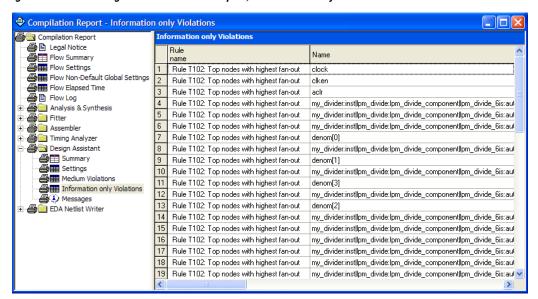

| Checking Design Violations Using the Design Assistant                       |      |

| Quartus II Design Flow with the Design Assistant                            |      |

| The Design Assistant Settings Page                                          |      |

| Message Severity Levels                                                     |      |

| Design Assistant Rules                                                      |      |

| Enabling and Disabling Design Assistant Rules                               |      |

| Viewing Design Assistant Results                                            | 5–40 |

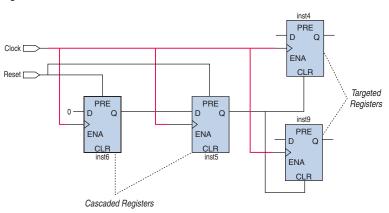

| Targeting Clock and Register-Control Architectural Features                 | 5–44 |

| Clock Network Resources                                                     | 5–44 |

| Reset Resources                                                             | 5–45 |

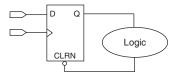

| Register Control Signals                                                    |      |

| Conclusion                                                                  |      |

| Referenced Documents                                                        | 5–46 |

| Document Revision History                                                   | 5–47 |

|                                                                             |      |

| Chapter 6. Recommended HDL Coding Styles                                    |      |

| Introduction                                                                |      |

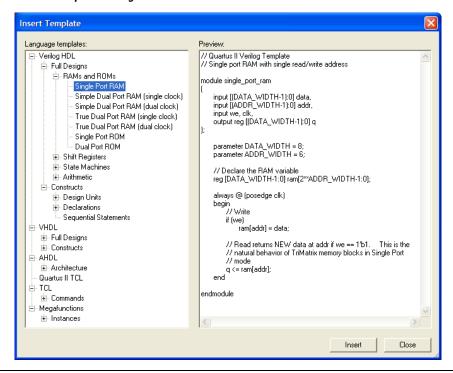

| Quartus II Language Templates                                               | 6–2  |

| Using Altera Megafunctions                                                  |      |

| Instantiating Altera Megafunctions in HDL Code                              |      |

| Instantiating Megafunctions Using the MegaWizard Plug-In Manager            |      |

| Creating a Netlist File for Other Synthesis Tools                           | 6–6  |

| Instantiating Megafunctions Using the Port and Parameter Definition         | 6–7  |

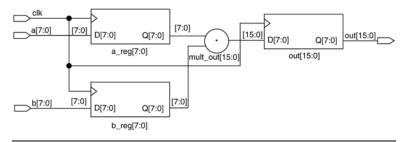

| Inferring Multiplier and DSP Functions from HDL Code                        |      |

| Multipliers—Inferring the lpm_mult Megafunction from HDL Code               |      |

| Multiply-Accumulators and Multiply-Adders—Inferring altmult_accum and altmu |      |

| Megafunctions from HDL Code                                                 |      |

| Inferring Memory Functions from HDL Code                                    |      |

| RAM Functions—Inferring altsyncram and altdpram Megafunctions from HDL Co   |      |

| ROM Functions—Inferring altsyncram and lpm_rom Megafunctions from HDL Co    |      |

| Shift Registers—Inferring the altshift_taps Megafunction from HDL Code      |      |

| Coding Guidelines for Registers and Latches                                 |      |

| Register Power-Up Values in Altera Devices                                  |      |

| Secondary Register Control Signals Such as Clear and Clock Enable           |      |

| Latches                                                                     |      |

| General Coding Guidelines                                                   |      |

| Tri-State Signals                                                           |      |

| Adder Trees                                                                 |      |

| State Machines                                                              |      |

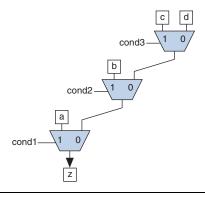

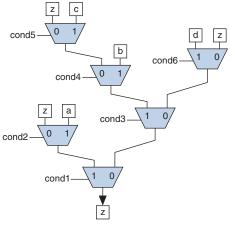

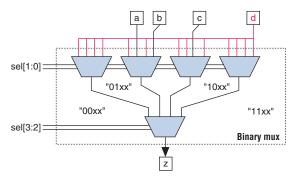

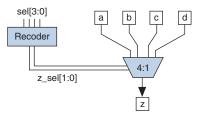

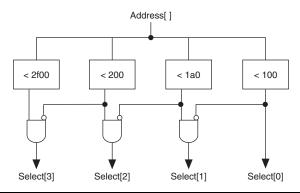

| Multiplexers                                                                |      |

| Cyclic Redundancy Check Functions                                           |      |

| Comparators                                                                 |      |

| Counters                                                                    |      |

| Designing with Low-Level Primitives                                         |      |

| Conclusion                                                                  |      |

| Referenced Documents                                                        |      |

| Document Revision History                                                   | 6-/5 |

viii Altera Corporation

# Section III. Synthesis

| Chapter 7. Synplicity Synplify and Synplify Pro Support                                |      |

|----------------------------------------------------------------------------------------|------|

| Introduction                                                                           | 7–1  |

| Altera Device Family Support                                                           | 7–2  |

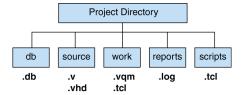

| Design Flow                                                                            | 7–3  |

| Output Netlist File Name and Result Format                                             | 7–7  |

| Synplify Optimization Strategies                                                       | 7–8  |

| Implementations in Synplify Pro                                                        | 7–8  |

| Timing-Driven Synthesis Settings                                                       | 7–9  |

| FSM Compiler                                                                           |      |

| Optimization Attributes and Options                                                    | 7–12 |

| Altera-Specific Attributes                                                             |      |

| Exporting Designs to the Quartus II Software Using NativeLink Integration              | 7–17 |

| Running the Quartus II Software from within the Synplify Software                      |      |

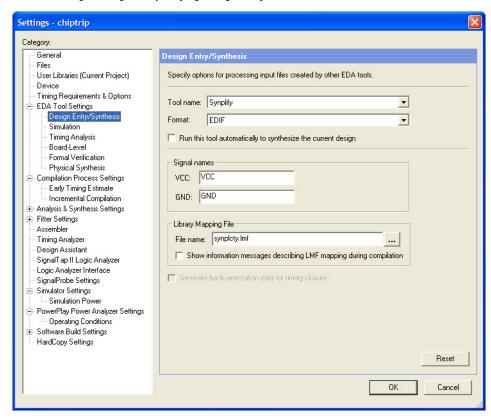

| Using the Quartus II Software to Run the Synplify Software                             | 7–19 |

| Running the Quartus II Software Manually Using the Synplify-Generated Tcl Script       | 7–19 |

| Passing TimeQuest SDC Timing Constraints to the Quartus II Software in the .scf File . | 7–20 |

| Passing Constraints to the Quartus II Software using Tcl Commands                      | 7–22 |

| Guidelines for Altera Megafunctions and Architecture-Specific Features                 |      |

| Instantiating Altera Megafunctions Using the MegaWizard Plug-In Manager                | 7–33 |

| Inferring Altera Megafunctions from HDL Code                                           | 7–37 |

| Incremental Compilation and Block-Based Design                                         | 7–44 |

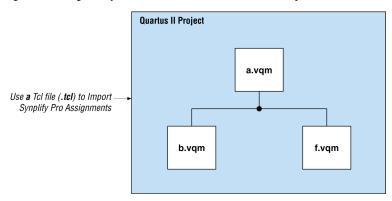

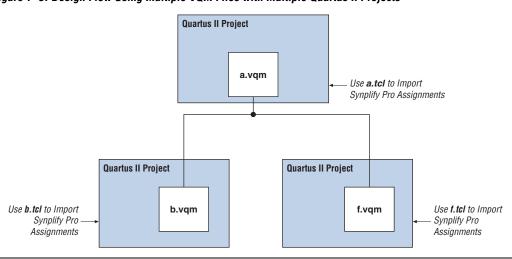

| Hierarchy and Design Considerations with Multiple VQM Files                            | 7–46 |

| Creating a Design with Separate Netlist Files                                          | 7–46 |

| Creating a Design with Multiple VQM Files Using Synplify Pro MultiPoint Synthesis      | 7–47 |

| Generating a Design with Multiple VQM Files Using Black Boxes                          | 7–54 |

| Conclusion                                                                             |      |

| Referenced Documents                                                                   | 7–61 |

| Document Revision History                                                              | 7–61 |

| Chapter 8. Quartus II Integrated Synthesis                                             |      |

| Introduction                                                                           | 8–1  |

| Design Flow                                                                            |      |

| Language Support                                                                       |      |

| Verilog HDL Support                                                                    |      |

| VHDL Support                                                                           |      |

| AHDL Support                                                                           |      |

| Schematic Design Entry Support                                                         |      |

| State Machine Editor                                                                   | 8–13 |

| Design Libraries                                                                       |      |

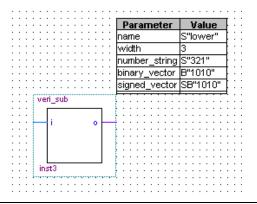

| Using Parameters/Generics                                                              |      |

| Incremental Synthesis and Incremental Compilation                                      |      |

| Partitions for Preserving Hierarchical Boundaries                                      |      |

| Quartus II Synthesis Options                                                           |      |

| Setting Synthesis Options                                                              |      |

Altera Corporation ix

| Optimization Technique                                                                                                                                                                                                              |                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Speed Optimization Technique for Clock Domains                                                                                                                                                                                      |                                      |

| PowerPlay Power Optimization                                                                                                                                                                                                        | 8–31                                 |

| Restructure Multiplexers                                                                                                                                                                                                            | 8–32                                 |

| State Machine Processing                                                                                                                                                                                                            |                                      |

| Manually Specifying State Assignments Using the syn_encoding Attribute                                                                                                                                                              | 8–35                                 |

| Manually Specifying Enumerated Types Using the enum_encoding Attribute                                                                                                                                                              |                                      |

| Safe State Machines                                                                                                                                                                                                                 |                                      |

| Power-Up Level                                                                                                                                                                                                                      | 8–42                                 |

| Power-Up Don't Care                                                                                                                                                                                                                 | 8–43                                 |

| Remove Duplicate Registers                                                                                                                                                                                                          | 8–44                                 |

| Remove Redundant Logic Cells                                                                                                                                                                                                        | 8–44                                 |

| Preserve Registers                                                                                                                                                                                                                  |                                      |

| Disable Register Merging/Don't Merge Register                                                                                                                                                                                       | 8–45                                 |

| Noprune Synthesis Attribute/Preserve Fan-out Free Register Node                                                                                                                                                                     | 8–46                                 |

| Keep Combinational Node/Implement as Output of Logic Cell                                                                                                                                                                           | 8–47                                 |

| Don't Retime, Disabling Synthesis Netlist Optimizations                                                                                                                                                                             | 8–48                                 |

| Don't Replicate, Disabling Synthesis Netlist Optimizations                                                                                                                                                                          | 8–49                                 |

| Maximum Fan-Out                                                                                                                                                                                                                     | 8–50                                 |

| Controlling Clock Enable Signals with Auto Clock Enable Replacement and dir                                                                                                                                                         |                                      |

|                                                                                                                                                                                                                                     |                                      |

| Megafunction Inference Control                                                                                                                                                                                                      |                                      |

| RAM Style and ROM Style—for Inferred Memory                                                                                                                                                                                         |                                      |

| Turning Off Add Pass-Through Logic to Inferred RAMs/ no_rw_check Attribu                                                                                                                                                            |                                      |

|                                                                                                                                                                                                                                     |                                      |

| RAM Initialization File—for Inferred Memory                                                                                                                                                                                         |                                      |

| Multiplier Style—for Inferred Multipliers                                                                                                                                                                                           |                                      |

| Full Case                                                                                                                                                                                                                           |                                      |

| Parallel Case                                                                                                                                                                                                                       |                                      |

| Translate Off and On / Synthesis Off and On                                                                                                                                                                                         |                                      |

| Ignore translate_off and synthesis_off Directives                                                                                                                                                                                   | 8–65                                 |

| Read Comments as HDL                                                                                                                                                                                                                |                                      |

| Use I/O Flipflops                                                                                                                                                                                                                   |                                      |

| Specifying Pin Locations with chip_pin                                                                                                                                                                                              |                                      |

| Using altera_attribute to Set Quartus II Logic Options                                                                                                                                                                              | 8–70                                 |

| Analyzing Synthesis Results                                                                                                                                                                                                         | 8–73                                 |

| Analysis and Synthesis Section of the Compilation Report                                                                                                                                                                            |                                      |

| Project Navigator                                                                                                                                                                                                                   |                                      |

| Analyzing and Controlling Synthesis Messages                                                                                                                                                                                        |                                      |

| Quartus II Messages                                                                                                                                                                                                                 | 8–74                                 |

|                                                                                                                                                                                                                                     | o ==                                 |

| VHDL and Verilog HDL Messages                                                                                                                                                                                                       |                                      |

| VHDL and Verilog HDL Messages                                                                                                                                                                                                       | 8–79                                 |

| VHDL and Verilog HDL Messages                                                                                                                                                                                                       | 8–79<br>8–79                         |

| VHDL and Verilog HDL Messages                                                                                                                                                                                                       | 8–79<br>8–79<br>8–80                 |

| VHDL and Verilog HDL Messages  Node-Naming Conventions in Quartus II Integrated Synthesis  Hierarchical Node-Naming Conventions  Node-Naming Conventions for Registers (DFF or D Flipflop Atoms)  Register Changes During Synthesis | 8–79<br>8–79<br>8–80<br>8–81         |

| VHDL and Verilog HDL Messages                                                                                                                                                                                                       | 8–79<br>8–79<br>8–80<br>8–81<br>8–84 |

x Altera Corporation

| Preserving Combinational Logic Names                        | 8–86  |

|-------------------------------------------------------------|-------|

| Scripting Support                                           | 8–86  |

| Adding an HDL File to a Project and Setting the HDL Version | 8–87  |

| Quartus II Synthesis Options                                |       |

| Assigning a Pin                                             |       |

| Creating Design Partitions for Incremental Compilation      | 8–90  |

| Conclusion                                                  |       |

| Referenced Documents                                        |       |

| Document Revision History                                   |       |

| Chapter 9. Mentor Graphics LeonardoSpectrum Support         |       |

| Introduction                                                | 9–1   |

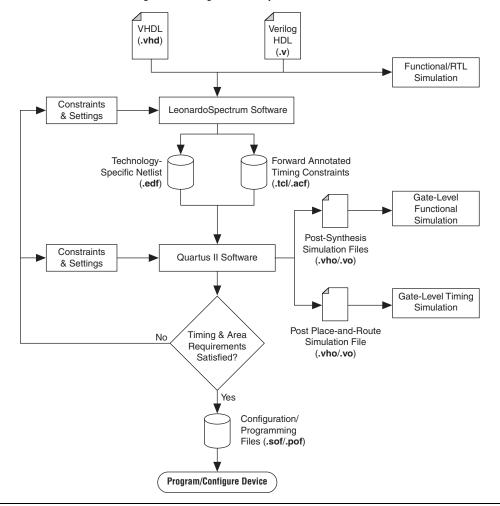

| Design Flow                                                 |       |

| Optimization Strategies                                     |       |

| Timing-Driven Synthesis                                     |       |

| Other Constraints                                           |       |

| Timing Analysis with the Leonardo-Spectrum Software         |       |

| Exporting Designs Using NativeLink Integration              | 9_9   |

| Generating Netlist Files                                    | 9_9   |

| Including Design Files for Black-Boxed Modules              | 9_0   |

| Passing Constraints with Scripts                            |       |

| Integration with the Quartus II Software                    |       |

| Guidelines for Altera Megafunctions and LPM Functions       |       |

| Inferring Multipliers and DSP Functions                     |       |

| Controlling DSP Block Inference                             |       |

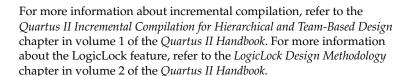

| Block-Based Design with the Quartus II Software             | 9–19  |

| Hierarchy and Design Considerations                         |       |

| Creating a Design with Multiple EDIF Files                  |       |

| Generating Multiple EDIF Files Using Black Boxes            | 9_25  |

| Incremental Synthesis Flow                                  |       |

| Conclusion                                                  |       |

| Referenced Documents                                        |       |

| Document Revision History                                   |       |

| Document Revision Photoly                                   |       |

| Chapter 10. Mentor Graphics Precision RTL Synthesis Support |       |

| Introduction                                                |       |

| Device Family Support                                       |       |

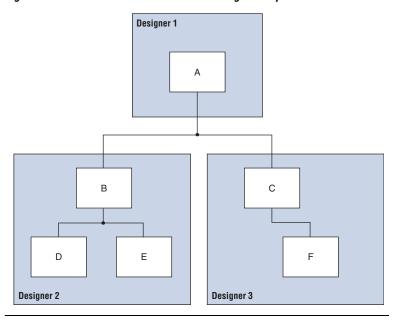

| Design Flow                                                 |       |

| Creating a Project and Compiling the Design                 |       |

| Creating a Project                                          |       |

| Compiling the Design                                        | 10–7  |

| Mapping the Precision Synthesis Design                      | 10–7  |

| Setting Timing Constraints                                  |       |

| Setting Mapping Constraints                                 | 10–9  |

| Assigning Pin Numbers and I/O Settings                      |       |

| Assigning I/O Registers                                     | 10–10 |

| Disabling I/O Pad Insertion                                 | 10 11 |

Altera Corporation xi

| Controlling Fan-Out on Data Nets                                             | 10–12 |

|------------------------------------------------------------------------------|-------|

| Synthesizing the Design and Evaluating the Results                           | 10–13 |

| Obtaining Accurate Logic Utilization and Timing Analysis Reports             | 10–13 |

| Exporting Designs to the Quartus II Software Using NativeLink Integration    |       |

| Running the Quartus II Software from within the Precision RTL Software       | 10–14 |

| Running the Quartus II Software Manually Using the Precision RTL Synthesis-C |       |

| Script                                                                       | 10–16 |

| Using Quartus II Software to Launch the Precision RTL Synthesis Software     | 10–17 |

| Passing Constraints to the Quartus II Software                               | 10–17 |

| Megafunctions and Architecture-Specific Features                             |       |

| Instantiating Altera Megafunctions Using the MegaWizard Plug-In Manager      | 10–24 |

| Inferring Altera Megafunctions from HDL Code                                 |       |

| Incremental Compilation and Block-Based Design                               |       |

| Hierarchy and Design Considerations                                          |       |

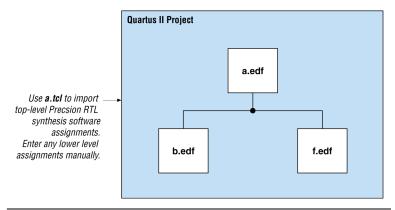

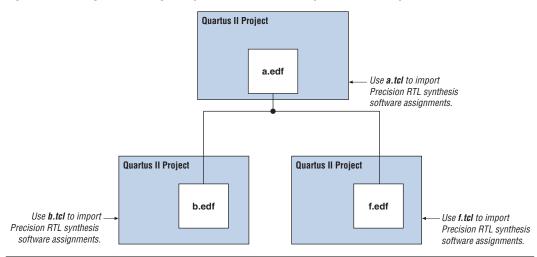

| Creating a Design with Separate Netlist Files                                |       |

| Creating Quartus II Projects for Multiple EDIF Files                         |       |

| Conclusion                                                                   |       |

| Referenced Documents                                                         | 10–42 |

| Document Revision History                                                    | 10–42 |

| ·                                                                            |       |

| Chapter 11. Synopsys Design Compiler FPGA Support                            |       |

| Introduction                                                                 | 11–1  |

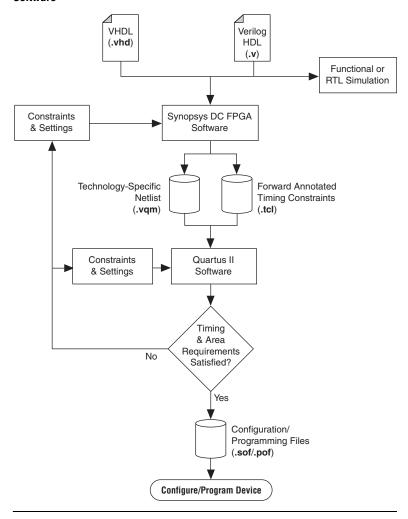

| Design Flow Using the DC FPGA Software and the Quartus II Software           | 11–2  |

| Setup of the DC FPGA Software Environment for Altera Device Families         | 11–3  |

| Megafunctions and Architecture-Specific Features                             | 11–5  |

| Instantiating Altera Megafunctions Using the MegaWizard Plug-In Manager      | 11–6  |

| Clear Box Methodology                                                        | 11–6  |

| Black Box Methodology                                                        |       |

| Inferring Altera Megafunctions from HDL Code                                 |       |

| Reading Design Files into the DC FPGA Software                               | 11–13 |

| Selecting a Target Device                                                    |       |

| Timing and Synthesis Constraints                                             | 11–16 |

| Compilation and Synthesis                                                    |       |

| Reporting Design Information                                                 |       |

| Saving Synthesis Results                                                     |       |

| Exporting Designs to the Quartus II Software                                 |       |

| write_fpga Command                                                           |       |

| write and write_par_constraint Commands                                      |       |

| Using Tcl Scripts with Quartus II Software                                   |       |

| Place and Route with the Quartus II Software                                 |       |

| Formality Software Support                                                   |       |

| Conclusion                                                                   |       |

| Referenced Documents                                                         |       |

| Document Revision History                                                    | 11–27 |

|                                                                              |       |

| Chapter 12. Analyzing Designs with Quartus II Netlist Viewers                |       |

| Introduction                                                                 | 12–1  |

xii Altera Corporation

| When to Use Viewers: Analyzing Design Problems                   | 12–2    |

|------------------------------------------------------------------|---------|

| Quartus II Design Flow with Netlist Viewers                      | 12–3    |

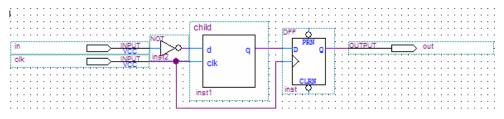

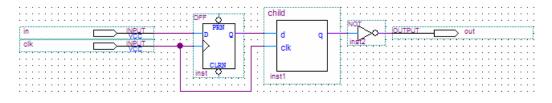

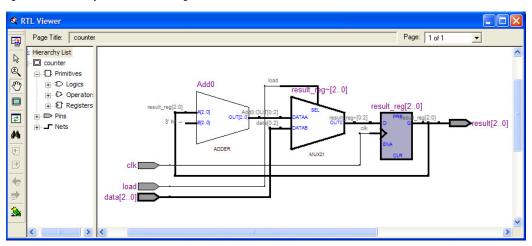

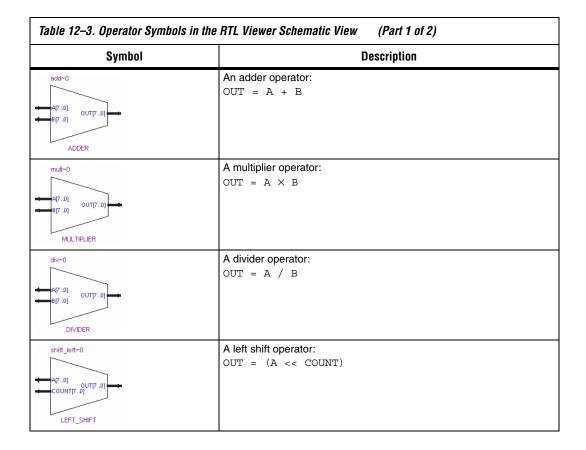

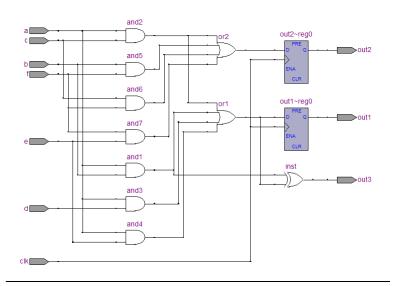

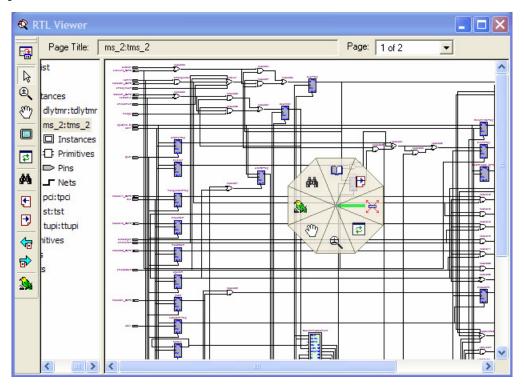

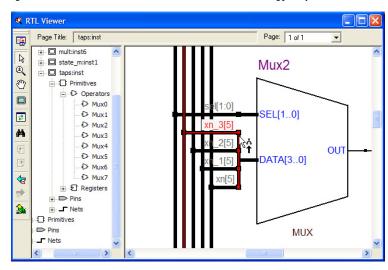

| RTL Viewer Overview                                              | 12–4    |

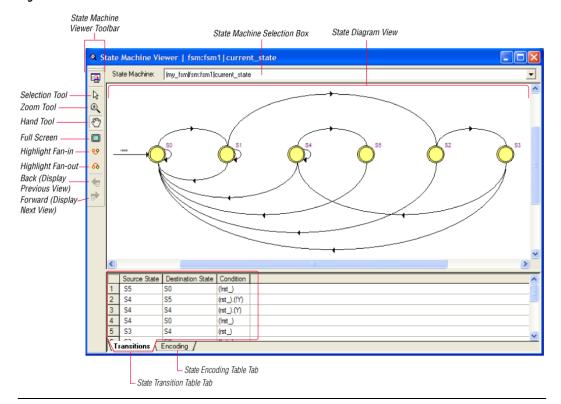

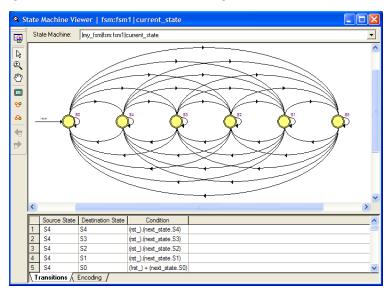

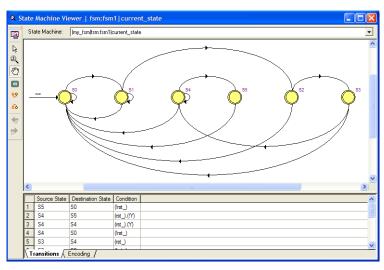

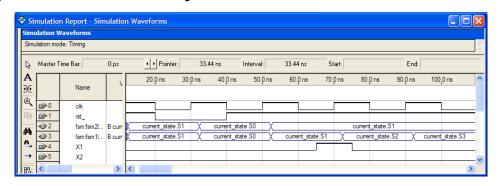

| State Machine Viewer Overview                                    | 12–6    |

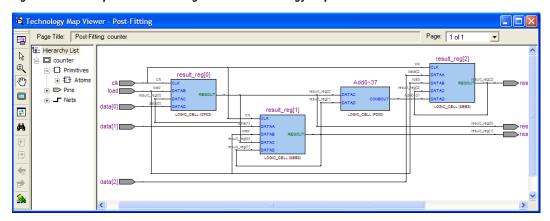

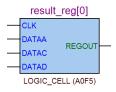

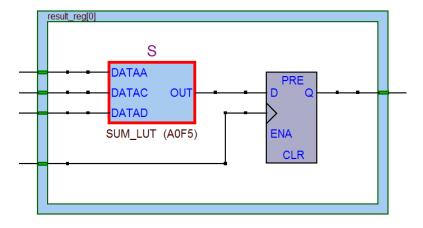

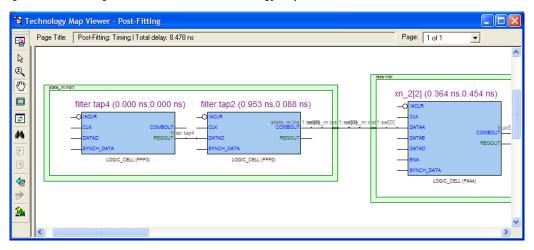

| Technology Map Viewer Overview                                   |         |

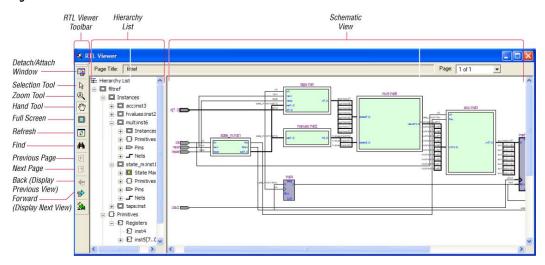

| Introduction to the User Interface                               | 12–7    |

| Schematic View                                                   | 12–8    |

| Hierarchy List                                                   | . 12–16 |

| State Machine Viewer                                             | . 12–18 |

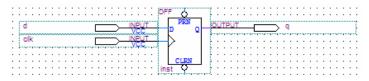

| Navigating the Schematic View                                    | . 12–21 |

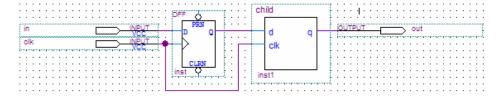

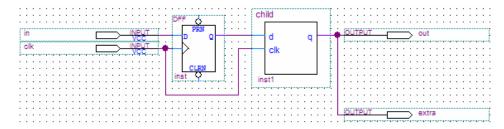

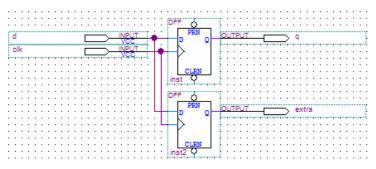

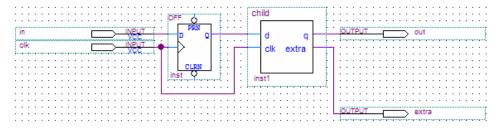

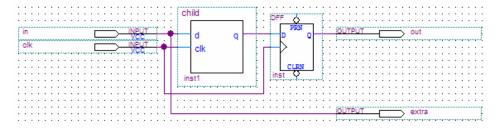

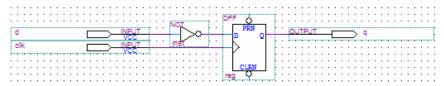

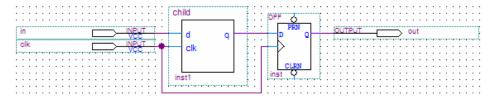

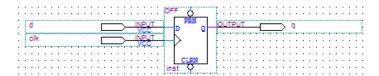

| Traversing and Viewing the Design Hierarchy                      | . 12–21 |

| Viewing Contents of Atom Primitives in the Technology Map Viewer |         |

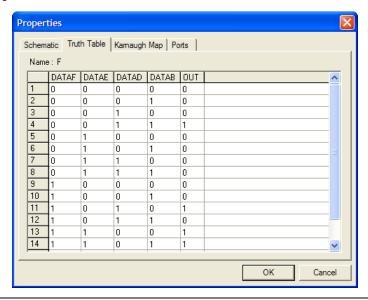

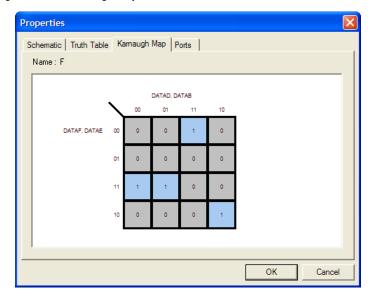

| Viewing the Properties of Instances and Primitives               | . 12–24 |

| Viewing LUT Representations in the Technology Map Viewer         | . 12–24 |

| Zooming and Magnification                                        |         |

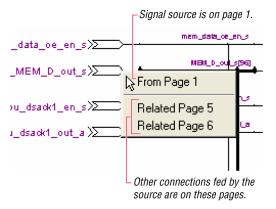

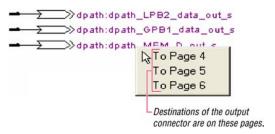

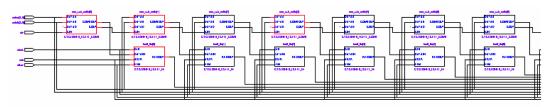

| Partitioning the Schematic into Pages                            | . 12–28 |

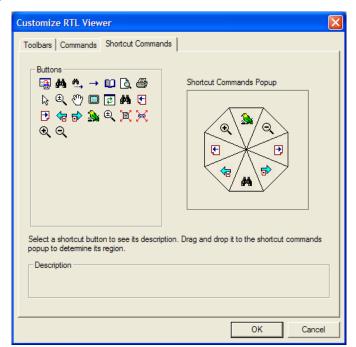

| Customizing the Schematic Display in the RTL Viewer              | . 12–31 |

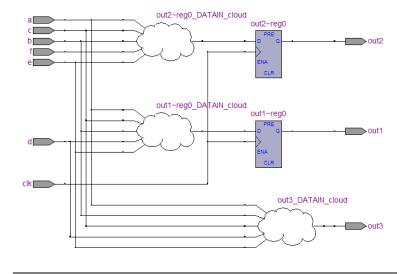

| Grouping Combinational Logic into Logic Clouds                   | . 12–32 |

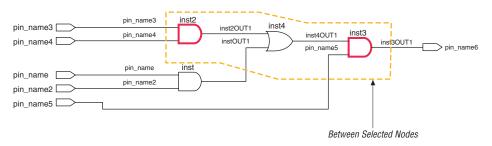

| Filtering in the Schematic View                                  | . 12–34 |

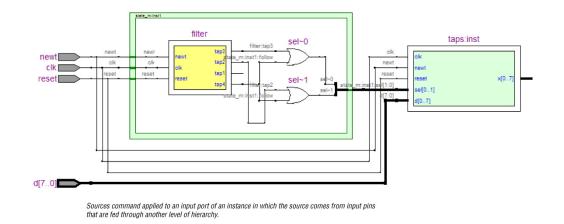

| Filter Sources Command                                           | . 12–35 |

| Filter Destinations Command                                      |         |

| Filter Sources and Destinations Command                          |         |

| Filter Between Selected Nodes Command                            |         |

| Filter Selected Nodes and Nets Command                           |         |

| Filter Bus Index Command                                         |         |

| Filter Command Processing                                        |         |

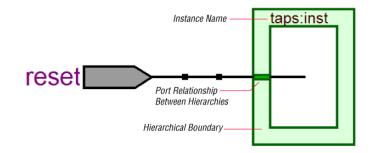

| Filtering Across Hierarchies                                     | . 12–38 |

| Expanding a Filtered Netlist                                     | . 12–40 |

| Reducing a Filtered Netlist                                      | . 12–41 |

| Probing to Source Design File and Other Quartus II Windows       |         |

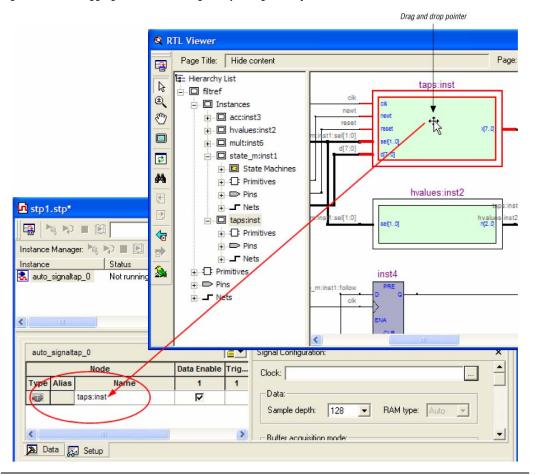

| Moving Selected Nodes to Other Quartus II Windows                |         |

| Probing to the Viewers from Other Quartus II Windows             |         |

| Viewing a Timing Path                                            |         |

| Other Features in the Schematic Viewer                           |         |

| Tooltips                                                         | . 12–47 |

| Radial Menu                                                      |         |

| Rollover                                                         |         |

| Displaying Net Names                                             |         |

| Displaying Node Names                                            |         |

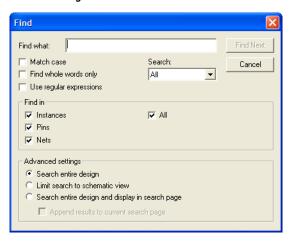

| Find Command                                                     |         |

| Exporting and Copying a Schematic Image                          |         |

| Printing                                                         |         |

| Debugging HDL Code with the State Machine Viewer                 |         |

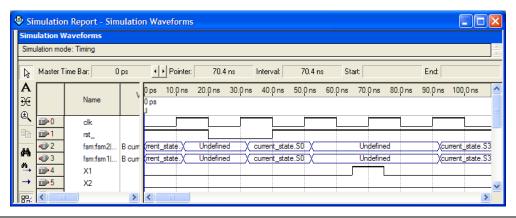

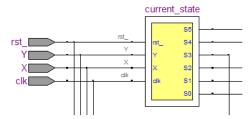

| Simulation of State Machine Gives Unexpected Results             | . 12–56 |

| Conclusion                                                       |         |

| Document Revision History                                        |         |

xiv Altera Corporation

# **Chapter Revision Dates**

The chapters in this book, *Quartus II Handbook*, *Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Design Planning with the Quartus II Software

Revised: October 2007 Part number: QII51016-7.2.0

Chapter 2. Quartus II Incremental Compilation for Hierarchical and Team-Based Design

Revised: October 2007 Part number: QII51015-7.2.0

Chapter 3. Quartus II Design Flow for MAX+PLUS II Users

Revised: October 2007 Part number: QII51002-7.2.0

Chapter 4. Quartus II Support for HardCopy Series Devices

Revised: October 2007 Part number: QII51004-7.2.0

Chapter 5. Design Recommendations for Altera Devices and the Quartus II Design Assistant

Revised: October 2007 Part number: QII51006-7.2.0

Chapter 6. Recommended HDL Coding Styles

Revised: October 2007 Part number: QII51007-7.2.0

Chapter 7. Synplicity Synplify and Synplify Pro Support

Revised: October 2007 Part number: QII51009-7.2.0

Chapter 8. Quartus II Integrated Synthesis

Revised: October 2007 Part number: QII51008-7.2.0

Chapter 9. Mentor Graphics LeonardoSpectrum Support

Revised: October 2007 Part number: QII51010-7.2.0

Altera Corporation xv

Chapter 10. Mentor Graphics Precision RTL Synthesis Support

Revised: October 2007 Part number: QII51011-7.2.0

Chapter 11. Synopsys Design Compiler FPGA Support

Revised: *October* 2007 Part number: *QII51014-7.2.0*

Chapter 12. Analyzing Designs with Quartus II Netlist Viewers

Revised: October 2007 Part number: QII51013-7.2.0

xvi Altera Corporation

# **About this Handbook**

This handbook provides comprehensive information about the Altera® Quartus® II design software, version 7.2.

### How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| Information Type           | Contact (1)                                     |

|----------------------------|-------------------------------------------------|

| Technical support          | www.altera.com/mysupport/                       |

| Technical training         | www.altera.com/training/<br>custrain@altera.com |

| Product literature         | www.altera.com/literature/                      |

| Altera literature services | literature@altera.com (1)                       |

| FTP site                   | ftp.altera.com                                  |

#### Note to table:

(1) You can also contact your local Altera sales office or sales representative.

# Third-Party Software Product Information

Third-party software products described in this handbook are not Altera products, are licensed by Altera from third parties, and are subject to change without notice. Updates to these third-party software products may not be concurrent with Quartus II software releases. Altera has assumed responsibility for the selection of such third-party software products and its use in the Quartus II 7.2 software release. To the extent that the software products described in this handbook are derived from third-party software, no third party warrants the software, assumes any liability regarding use of the software, or undertakes to furnish you any support or information relating to the software. EXCEPT AS EXPRESSLY SET FORTH IN THE APPLICABLE ALTERA PROGRAM LICENSE SUBSCRIPTION AGREEMENT UNDER WHICH THIS SOFTWARE WAS PROVDED TO YOU, ALTERA AND THIRD-PARTY LICENSORS DISCLAIM ALL WARRANTIES WITH RESPECT TO THE USE OF SUCH THIRD-PARTY SOFTWARE CODE OR DOCUMENTATION IN THE SOFTWARE, INCLUDING, WITHOUT LIMITATION, ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT. For more information, including the latest available version of specific third-party software products, refer to the documentation for the software in question.

Altera Corporation xvii

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file.                                                                         |

| Italic Type with Initial<br>Capital Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                                                                                         |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{P/A}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <project name="">.pof file.</project></file>                                                                                                                                                                     |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: $\mathtt{data1}$ , $\mathtt{tdi}$ , $\mathtt{input}$ . Active-low signals are denoted by suffix $\mathtt{n}$ , e.g., $\mathtt{resetn}$ .                                                                                                           |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| ✓, —, N/A                                   | Used in table cells to indicate the following: ✓ indicates a "Yes" or "Applicable" statement; — indicates a "No" or "Not Supported" statement; N/A indicates that the table cell entry is not applicable to the item of interest.                                                                                       |

| •••                                         | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                           | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| CAUTION                                     | A caution calls attention to a condition or possible situation that can damage or destroy the product or the user's work.                                                                                                                                                                                               |

| WARNING                                     | A warning calls attention to a condition or possible situation that can cause injury to the user.                                                                                                                                                                                                                       |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                         | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

xviii Altera Corporation

# **Section I. Design Flows**

The Altera® Quartus® II, version 7.2 design software provides a complete multi-platform design environment that easily adapts to your specific design needs. The Quartus II software also allows you to use the Quartus II graphical user interface, EDA tool interface, or command-line interface for each phase of the design flow. This section explains the Quartus II, version 7.2 software options that are available for each of these flows.

This section includes the following chapters:

- Chapter 1, Design Planning with the Quartus II Software

- Chapter 2, Quartus II Incremental Compilation for Hierarchical and Team-Based Design

- Chapter 3, Quartus II Design Flow for MAX+PLUS II Users

- Chapter 4, Quartus II Support for HardCopy Series Devices

For information about the revision history for chapters in this section, refer to each individual chapter for that chapter's revision history.

Altera Corporation Section I-i

Section I-ii Altera Corporation

# 1. Design Planning with the Quartus II Software

QII51016-7.2.0

#### Introduction

Due to the significant increase in FPGA device densities over the last few years, designs are increasingly complex and may involve multiple designers. The inherent flexibility of advanced FPGAs means that the pin layout, power consumption, and timing performance for each design block are all dependent on the final design implementation. The system architect must resolve these design issues when integrating design blocks, often leading to problems that affect the overall time to market and thereby increase cost. Many potential problems can be solved earlier in the design cycle by selecting the optimal device and programming method, properly planning I/O pin locations, estimating power consumption, selecting appropriate third-party tools, planning for in-system debugging options, performing good design partitioning for incremental compilation, and obtaining early timing estimates.

This chapter discusses these important FPGA design planning issues, provides recommendations, and describes various tools available for Altera® FPGAs to help you improve design productivity. This chapter contains the following sections:

- "Device and Programming/ Configuration Method Selection" on page 1–2

- "Early Planning Tools for Power and I/O" —"Early Power Estimation" on page 1–5

- "Early Pin Planning and I/O Analysis" on page 1–6

- "Selecting Third-Party EDA Tool Flows" on page 1–9

- "Planning for On-Chip Debugging Options" on page 1–11

- "Planning for an Incremental Compilation Flow" on page 1–13

- "Early Timing Estimation" on page 1–19

Before reading the design planning guidelines discussed in this chapter, consider your design priorities: What are the important factors for your design? More device features, density, or performance can increase system cost. Signal integrity and board issues may impact I/O pin locations. Power, timing performance, and area utilization affect each other, and compilation time is affected by optimizations for these factors. The Quartus® II software optimizes designs for the best average results, but you can change settings to focus on one aspect of the design results and trade off other aspects. Certain tools or debugging options can lead to restrictions in your design flow. If you know what is important in a particular design, this knowledge will help you choose the tools, features, and methodologies that you should use with the design. This chapter

cannot cover every possible consideration for planning a complex FPGA design, but once you understand your design priorities, you can use the design planning issues described here as a guide to help ensure a productive and successful FPGA design flow.

This chapter provides an introduction to various design and planning features in the Quartus<sup>®</sup> II software. For a general overview of the Quartus II design flow and features, refer to the *Introduction to Quartus II Manual*. For more details about specific Quartus II features and methodologies, this chapter provides references to other appropriate chapters in the *Quartus II Handbook*.

# Device and Programming/ Configuration Method Selection

The first stage in design planning is choosing the best device for your application and determining how you want to program or configure the device in your system. These factors affect the rest of your design cycle, including board specification and layout. Most of this planning is performed outside of the Quartus II software, but this section provides a few suggestions to aid in the planning process.

#### **Device Selection**

It is important to choose the device family that best suits your design needs. Different families offer different trade-offs, including cost, performance, logic and memory density, I/O density, power utilization, and packaging. You should also consider feature requirements such as I/O standards support, high-speed transceivers, and the number of phase-locked loops (PLLs) available in the device. You can review important features of each device family in the Selector Guides available on the Altera website (www.altera.com/literature/lit-sg.jsp). Each device family also has a device handbook or set of data sheets that documents the device features in detail.

Determining the required device density can be a challenging part of the design planning process. Devices with more logic resources and higher I/O counts can implement larger and potentially more complex designs, but may have a higher cost. Select a device that meets your design needs with some safety margin, in case you want to add more logic later in the design cycle or reserve logic and memory for on-chip debugging (refer to "Planning for On-Chip Debugging Options" on page 1–11). Consider needs for specific types of dedicated logic blocks, such as memory blocks of different sizes, or digital signal processing (DSP) blocks to implement certain arithmetic functions.

If you have prior designs targeting Altera devices, you can use their resource utilization as an estimate for your new design. You can compile existing designs in the Quartus II software with the device selection set to

Auto to review the resource utilization and find out which device density fits the design. Note that coding style, device architecture, and the optimization options used in the Quartus II software can significantly affect a design's resource utilization.

To obtain resource utilization estimates for certain configurations of Altera's intellectual property (IP) designs, refer to the User Guides for Altera Megafunctions and IP MegaCores on the IP Megafunctions page on the Altera website (www.altera.com/literature/lit-ip.jsp). You can use these numbers to help estimate the resource utilization of your design.

#### **Device Migration Planning**

Determine if you want the option of migrating your design to another device density to allow flexibility when the design nears completion, or if you want to migrate to a HardCopy® structured ASIC device when the design reaches volume production. In some cases, designers may target a smaller (and less expensive) device and then move to a larger device if necessary to fit their design. Other designers may prototype their design in a larger device to reduce optimization time and achieve timing closure more quickly, and then migrate to a final smaller device after prototyping. Similarly, many designers compile and optimize their design for an FPGA device before moving to a HardCopy structured ASIC when the design is complete and ready for higher-volume production. If you would like this flexibility, you should specify these migration options in the Quartus II software at the beginning of your design cycle. Specify the target migration devices in the Migration compatibility section of the Device page in the Settings dialog box.

Selecting a migration device has an impact on pin placement because some pins may serve different functions in different device densities or package sizes. When making pin assignments in the Quartus II software, the Pin Migration View in the Pin Planner highlights pins that change function between your migration devices. (Refer to "Early Pin Planning and I/O Analysis" on page 1–6 for more details.) Selecting a migration device may force you to restrict logic utilization to ensure that your design is compatible with a selected HardCopy device. Adding migration devices later in the design cycle is possible, but requires extra effort to check pin assignments, and may require design changes to fit into the new target device. It is much easier to consider these issues early in the design cycle than at the end, when the design is near completion and ready for migration.

In addition, if you are planning to use a HardCopy device, review HardCopy guidelines early in the design cycle for any Quartus II settings that should be used or other restrictions you should consider. It is especially important to use complete timing constraints if you want to migrate to a HardCopy device because of the rigorous verification requirements for structured ASICs.

For more information about timing requirements and analysis for HardCopy designs, refer to the *HardCopy Handbook*.

#### **Programming/Configuration Method Selection**

Choosing your programming or configuration method up-front allows system and board designers to determine what companion devices, if any, are needed for your system. Your board layout also depends on the type of programming or configuration method you plan to use for programmable devices. Many programming options use a JTAG interface to connect to the devices, so your design may require a JTAG chain be set up on the board.