# **Avalon Memory-Mapped**

# **Interface Specification**

101 Innovation Drive San Jose, CA 95134 www.altera.com

Document Version: Document Date: 3.3 May 2007

Copyright © 2005 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the ap-

plication or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

MNL-AVABUSREF-3.3

# **Table of Contents**

| How to Contact Altera                                |    |

|------------------------------------------------------|----|

| Typographic Conventions                              |    |

| Introduction                                         |    |

| Features                                             |    |

| Terms and Concepts                                   |    |

| Avalon-MM Peripherals and System Interconnect Fabric |    |

| Avalon-MM Signal Types: A Configurable Interface     |    |

| Master Ports and Slave Ports                         |    |

| Avalon-MM Peripherals                                |    |

| Transfer                                             | 13 |

| Master-Slave Pair                                    | 13 |

| Cycle                                                | 13 |

| Avalon-MM Signals                                    |    |

| Complete List of Signal Types                        |    |

| Signal Polarity                                      | 22 |

| Signal Naming Conventions                            | 22 |

| Signal Sequencing and Timing                         |    |

| Synchronous Interface                                | 23 |

| Interfacing to Asynchronous Peripherals              |    |

| Performance                                          |    |

| Electrical Characteristics                           | 24 |

| Transfer Properties                                  | 24 |

| Slave Transfers                                      |    |

| Slave Signal Details                                 |    |

| address                                              | 26 |

| readdata and writedata                               | 26 |

| chipselect, read, and write                          | 26 |

| byteenable and writebyteenable                       | 27 |

| begintransfer                                        | 28 |

| Slave Read Transfers                                 |    |

| Fundamental Slave Read Transfer                      | 28 |

| Wait-States                                          |    |

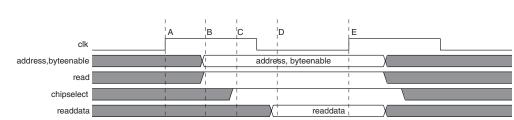

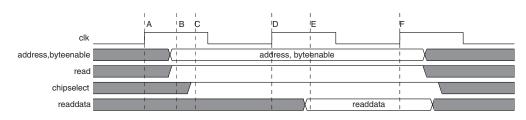

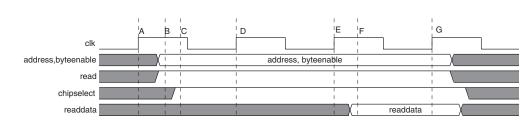

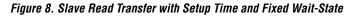

| Slave Read Transfer with Fixed Wait-States           | 30 |

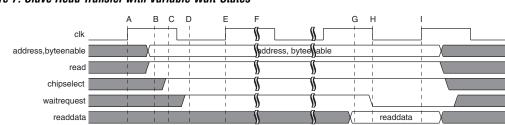

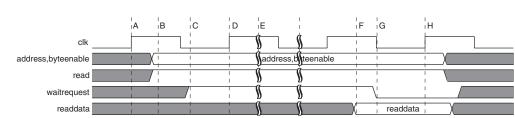

| Slave Read Transfer with Variable Wait-States        | 32 |

| Restrictions                                         | 33 |

| Setup Time                                           |    |

| Restrictions                                         | 34 |

| Hold Time                                            | 34 |

| Pipeline, Burst, and Tristate Properties             |    |

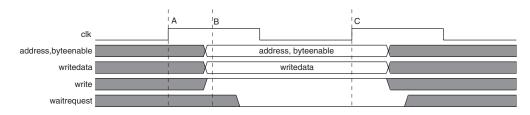

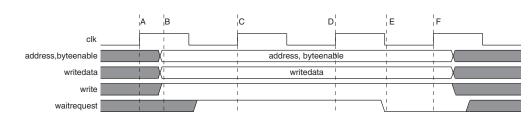

| Slave Write Transfers                                |    |

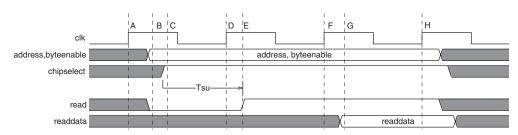

| Fundamental Slave Write Transfer                     | 35 |

| Wait-States                                                                                                                                                                                                                                                                |                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

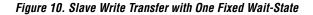

| Slave Write Transfer with Fixed Wait-States                                                                                                                                                                                                                                |                                                                                                                                                          |

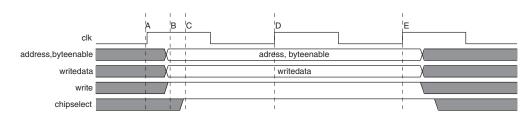

| Slave Write Transfer with Variable Wait-States                                                                                                                                                                                                                             | 37                                                                                                                                                       |

| Restrictions                                                                                                                                                                                                                                                               |                                                                                                                                                          |

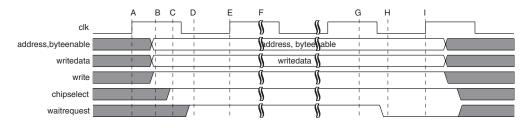

| Slave Write Transfer with Setup and Hold Times                                                                                                                                                                                                                             |                                                                                                                                                          |

| Restrictions                                                                                                                                                                                                                                                               | 40                                                                                                                                                       |

| Pipeline, Burst and Tristate Properties                                                                                                                                                                                                                                    |                                                                                                                                                          |

| Master Transfers                                                                                                                                                                                                                                                           |                                                                                                                                                          |

| Master Signal Details                                                                                                                                                                                                                                                      | 41                                                                                                                                                       |

| waitrequest                                                                                                                                                                                                                                                                | 42                                                                                                                                                       |

| address                                                                                                                                                                                                                                                                    | 42                                                                                                                                                       |

| readdata and writedata                                                                                                                                                                                                                                                     | 42                                                                                                                                                       |

| read and write                                                                                                                                                                                                                                                             |                                                                                                                                                          |

| byteenable                                                                                                                                                                                                                                                                 | 43                                                                                                                                                       |

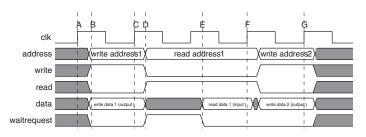

| Fundamental Master Read Transfers                                                                                                                                                                                                                                          | 43                                                                                                                                                       |

| Fundamental Master Write Transfers                                                                                                                                                                                                                                         |                                                                                                                                                          |

| Wait-State, Setup Time, and Hold Time Properties                                                                                                                                                                                                                           | 47                                                                                                                                                       |

| Pipeline, Burst, and Tristate Properties                                                                                                                                                                                                                                   | 47                                                                                                                                                       |

| Pipelined Transfers                                                                                                                                                                                                                                                        | 48                                                                                                                                                       |

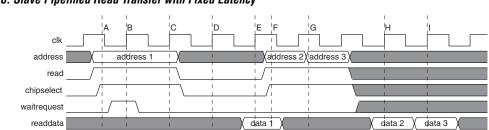

| Slave Pipelined Read Transfer with Fixed Latency                                                                                                                                                                                                                           | 48                                                                                                                                                       |

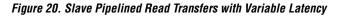

| Slave Pipelined Read Transfer with Variable Latency                                                                                                                                                                                                                        |                                                                                                                                                          |

| Restrictions                                                                                                                                                                                                                                                               |                                                                                                                                                          |

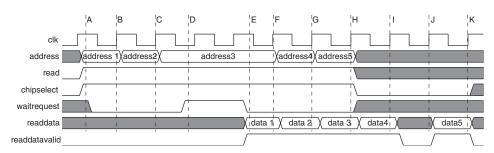

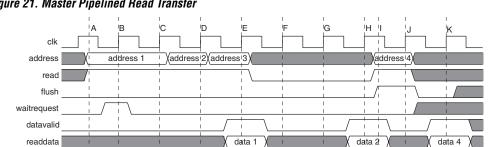

| Master Pipelined Read Transfer                                                                                                                                                                                                                                             | 53                                                                                                                                                       |

| Flow Control                                                                                                                                                                                                                                                               | 55                                                                                                                                                       |

|                                                                                                                                                                                                                                                                            |                                                                                                                                                          |

| Restrictions                                                                                                                                                                                                                                                               | 55                                                                                                                                                       |

| Restrictions<br>Slave Transfers with Flow Control                                                                                                                                                                                                                          | 55<br>55                                                                                                                                                 |

| Restrictions<br>Slave Transfers with Flow Control<br>Flow Control Signals                                                                                                                                                                                                  | 55<br>55<br>55                                                                                                                                           |

| Restrictions<br>Slave Transfers with Flow Control<br>Flow Control Signals<br>readyfordata and dataavailable                                                                                                                                                                | 55<br>55<br>55<br>55                                                                                                                                     |

| Restrictions<br>Slave Transfers with Flow Control<br>Flow Control Signals<br>readyfordata and dataavailable<br>endofpacket                                                                                                                                                 | 55<br>55<br>55<br>55<br>56                                                                                                                               |

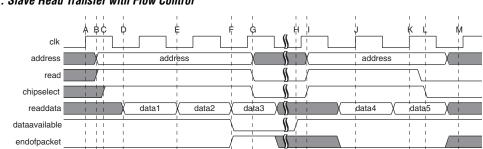

| Restrictions<br>Slave Transfers with Flow Control<br>Flow Control Signals<br>readyfordata and dataavailable<br>endofpacket<br>Slave Read Transfers with Flow Control                                                                                                       | 55<br>55<br>55<br>55<br>56<br>56                                                                                                                         |

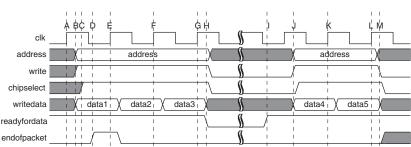

| Restrictions<br>Slave Transfers with Flow Control<br>Flow Control Signals<br>readyfordata and dataavailable<br>endofpacket<br>Slave Read Transfers with Flow Control<br>Slave Write Transfer with Flow Control                                                             | 55<br>55<br>55<br>56<br>56<br>58                                                                                                                         |

| Restrictions<br>Slave Transfers with Flow Control<br>Flow Control Signals<br>readyfordata and dataavailable<br>endofpacket<br>Slave Read Transfers with Flow Control<br>Slave Write Transfer with Flow Control<br>Master Transfers with Flow Control                       | 55<br>55<br>55<br>56<br>56<br>58<br>60                                                                                                                   |

| Restrictions<br>Slave Transfers with Flow Control<br>Flow Control Signals<br>readyfordata and dataavailable<br>endofpacket<br>Slave Read Transfers with Flow Control<br>Slave Write Transfer with Flow Control<br>Master Transfers with Flow Control<br>Tristate Transfers | 55<br>55<br>55<br>56<br>56<br>56<br>60<br>61                                                                                                             |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>58<br>60<br>61<br>62                                                                                                       |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>58<br>60<br>61<br>62<br>62                                                                                                 |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>56<br>56<br>60<br>61<br>62<br>62<br>62                                                                                     |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>58<br>60<br>61<br>62<br>62<br>62<br>62<br>63                                                                               |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>56<br>56<br>58<br>60<br>61<br>62<br>62<br>62<br>63<br>63                                                                   |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>56<br>56<br>56<br>60<br>61<br>62<br>62<br>62<br>63<br>63<br>64                                                             |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>56<br>56<br>56<br>60<br>61<br>62<br>62<br>62<br>62<br>63<br>63<br>64<br>65                                                 |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>56<br>60<br>61<br>62<br>62<br>62<br>63<br>63<br>64<br>65<br>66                                                             |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>56<br>56<br>60<br>61<br>62<br>62<br>62<br>63<br>63<br>63<br>64<br>65<br>66                                                 |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>56<br>56<br>56<br>56<br>60<br>61<br>62<br>62<br>63<br>63<br>63<br>64<br>65<br>66<br>66<br>67                                           |

| Restrictions                                                                                                                                                                                                                                                               |                                                                                                                                                          |

| Restrictions                                                                                                                                                                                                                                                               |                                                                                                                                                          |

| Restrictions                                                                                                                                                                                                                                                               | 55<br>55<br>55<br>55<br>56<br>56<br>56<br>56<br>56<br>60<br>61<br>62<br>62<br>62<br>62<br>62<br>63<br>63<br>64<br>65<br>66<br>66<br>67<br>67<br>68<br>69 |

| Restrictions                                | 70 |

|---------------------------------------------|----|

| Example                                     | 71 |

| Burst Transfers                             |    |

| Restrictions                                | 72 |

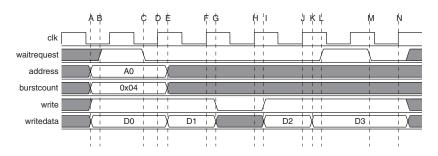

| Master Burst                                | 72 |

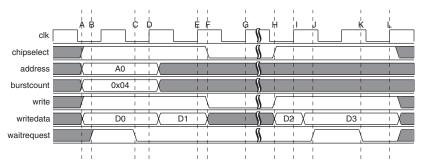

| Master Write Bursts                         | 73 |

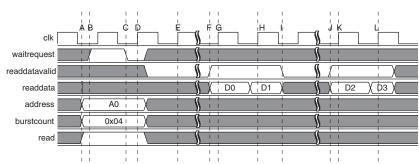

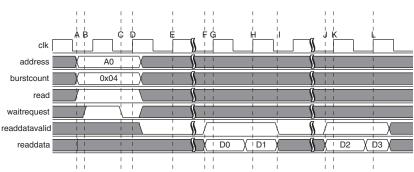

| Master Read Bursts                          | 74 |

| Slave Bursts                                | 76 |

| Slave Write Bursts                          | 77 |

| Slave Read Bursts                           | 79 |

| Non-Transfer Related Signals                | 80 |

| Interrupt Request Signals                   |    |

| Slave Interrupt Signal: irq                 | 81 |

| Master Interrupt Signals: irq and irqnumber |    |

| Software Priority                           | 81 |

| Hardware Priority                           | 81 |

| Reset Control Signals                       |    |

| reset Signal                                | 82 |

| resetrequest Signal                         | 82 |

| Address Alignment                           |    |

| Native Address Alignment                    |    |

| Dynamic Bus Sizing                          | 84 |

This specification provides comprehensive specification for the Avalon® Memory-Mapped Interface Specification, version 3.3.

# How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| ebsite<br>ebsite<br>nail<br>ebsite | www.altera.com/support<br>www.altera.com/training<br>custrain@altera.com<br>www.altera.com/literature |

|------------------------------------|-------------------------------------------------------------------------------------------------------|

| nail                               | custrain@altera.com                                                                                   |

|                                    |                                                                                                       |

| ebsite                             | www.eltere.com/litereture                                                                             |

|                                    | www.altera.com/ilterature                                                                             |

| nail                               | literature@altera.com                                                                                 |

| nail                               | nacomp@altera.com                                                                                     |

| nail                               | authorization@altera.com                                                                              |

| י<br>ו                             | ail                                                                                                   |

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                | Meaning                                                                                                                                                                                                                                                                     |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                  |

| bold type                                 | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file. |

| Italic Type with Initial Capital Letters  | Document titles are shown in italic type with initial capital letters. Example: <i>AN 75: High-Speed Board Design.</i>                                                                                                                                                      |

| Italic type                               | Internal timing parameters and variables are shown in italic type.<br>Examples: $t_{PIA}$ , $n + 1$ .<br>Variable names are enclosed in angle brackets (< >) and shown in italic type.                                                                                      |

| Initial Capital Latters                   | Example: <i><file name=""></file></i> , <i><project name=""></project></i> . <b>pof</b> file.                                                                                                                                                                               |

| Initial Capital Letters                   | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                |

| "Subheading Title"                        | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                |

| Visual Cue                          | Meaning                                                                                                                                                                                                                                                                                                             |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Courier type                        | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                   |

|                                     | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the VHDL keyword BEGIN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc. | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                    |

| ••                                  | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                |

| $\checkmark$                        | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                 |

| IP                                  | The hand points to information that requires special attention.                                                                                                                                                                                                                                                     |

| CAUTION                             | The caution indicates required information that needs special consideration and understanding and should be read prior to starting or continuing with the procedure or process.                                                                                                                                     |

| WARNING                             | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                                                                                                                                                    |

| ۲                                   | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                          |

| ••••                                | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                      |

# Avalon Memory-Mapped Interface Specification

# 1. Introduction

The Avalon Memory-Mapped (Avalon-MM) interface specification is designed to accommodate peripheral development for the system-on-aprogrammable-chip (SOPC) environment. The specification provides peripheral designers with a basis for describing the address-based read/write interface found on master and slave peripherals, such as microprocessors, memory, UART, timer, etc.

The specification defines transfers between a peripheral and an interconnect structure. The specification's interconnect strategy allows system designers to connect any master-type peripheral to any slave-type peripheral, without *a priori* knowledge of either the master or slave interface. The Avalon-MM interface specification describes a configurable interconnect strategy that allows a peripheral designer to limit the signal types needed to support the specific type(s) of transfers desired.

The Avalon-MM interface defines:

- A set of signal types

- The behavior of these signals

- The types of transfers supported by these signals

For example, the Avalon-MM interface can be used to describe a traditional peripheral interface, such as SRAM, that supports only simple, fixed-cycle read/write transfers. On the other hand, the Avalon-MM interface can also be used to describe a more complex pipelined interface capable of burst transfers.

# 1.1. Features

Some of the prominent features of the Avalon-MM interface are:

- Separate Address, Data and Control Lines Provides the simplest interface to on-chip logic. By using dedicated address and data paths, Avalon-MM peripherals do not need to decode data and address cycles.

- Up to 1024-bit Data Width Supports data paths up to 1024 bits. The Avalon-MM interface supports arbitrary data widths, including widths that are not an even power of two.

- Synchronous Operation Provides an interface optimized for synchronous, on-chip peripherals. Synchronous operation simplifies the timing behavior of the Avalon-MM interface, and facilitates integration with high-speed peripherals.

- Dynamic Bus Sizing Handles the details of transferring data between peripherals with different data widths. Avalon-MM peripherals with differing data widths can interface easily with no special design considerations.

- Simplicity Provides an easy-to-understand interface protocol with a short learning curve.

- Low resource utilization Provides an interface architecture that conserves on-chip logic resources.

- High performance Provides performance up to one-transfer-perclock.

The Avalon-MM interface is an open standard. No license is required to produce and distribute custom peripherals using the Avalon-MM interface.

# 1.2. Terms and Concepts

This section defines terms and concepts upon which the Avalon-MM interface specification is based.

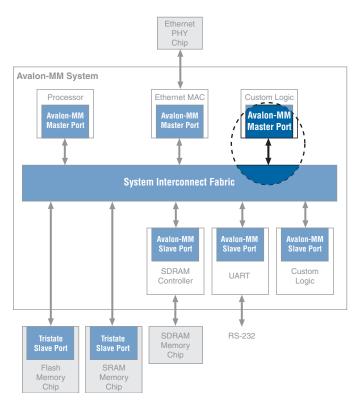

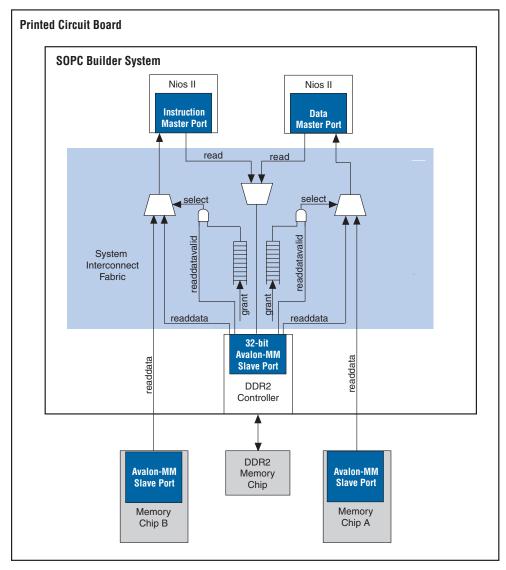

## 1.2.1. Avalon-MM Peripherals and System Interconnect Fabric

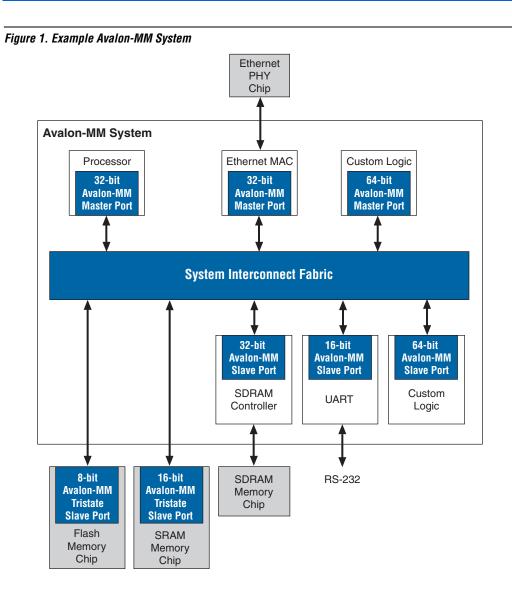

A typical system based on the Avalon-MM interface combines multiple functional modules, called *Avalon-MM peripherals*. *System interconnect fabric* is on-chip interconnect logic that connects the Avalon-MM peripherals together, forming a larger system. Figure 1 shows an example Avalon system with multiple Avalon-MM peripherals connected via system interconnect fabric.

The Avalon-MM interface defines the point of connection between Avalon-MM peripherals and the system interconnect fabric. This document focuses on the interfaces between the peripheral and the fabric. The Avalon-MM interface specification also defines the behavior of system interconnect fabric at the interface level, but does not specify the internal implementation.

### 1.2.2. Avalon-MM Signal Types: A Configurable Interface

The Avalon-MM interface defines a set of signal types (chip select, read enable, write enable, address, data, etc.) that describe the address-based read/write interfaces found on typical master and slave modules. An Avalon-MM peripheral uses exactly the signals required to interface to the peripheral's core logic, and excludes signals that would add unnecessary overhead. "Avalon-MM Slave Port Signals" on page 15 for the complete list of Avalon-MM signal types.

This configurability is one of the key differences between the Avalon-MM interface and traditional bus interfaces. Avalon-MM peripherals can use a small set of signals to support simple transfer types, or use more signals to support complex transfer types. For example, a ROM interface may require only address, read-data and select signals, while a high-speed memory controller may require additional signals to support pipelined bursts.

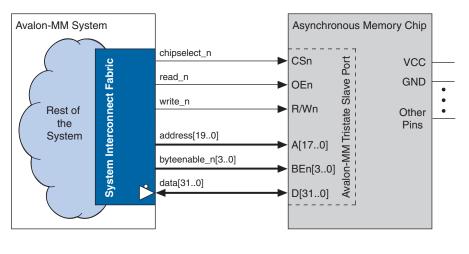

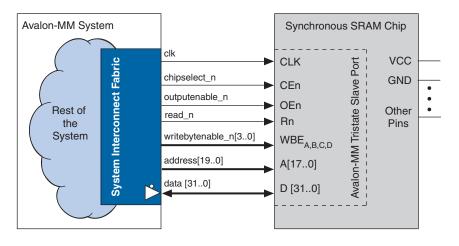

The Avalon-MM signal types provide a superset of several other bus interfaces. For example, the pins on most discrete SRAM, ROM and flash chips can be mapped to Avalon-MM signal types, allowing Avalon-MM systems to interface directly to these chips. Similarly, most Wishbone interface signals can be mapped to Avalon-MM signal types, making it easy to include Wishbone cores into Avalon-MM systems.

#### 1.2.3. Master Ports and Slave Ports

An *Avalon-MM port* is a group of Avalon-MM signals used collectively as a single interface. The role of an Avalon-MM port is categorized as either slave or master. A *master port* is the collection of Avalon-MM signal types used to initiate transfers. A *slave port* is the collection of Avalon-MM signal types used to respond to transfer requests.

Avalon-MM master and slave ports do not connect together directly. Instead, Avalon-MM ports connect to system interconnect fabric and the system interconnect fabric translates signals between master ports and slave ports, as shown in Figure 1 on page 11. During a transfer, the signals exchanged between a master port and the system interconnect fabric might be very different than the signals that the system interconnect fabric uses to communicate with the target slave port. For this reason, when discussing Avalon-MM transfers it is important to distinguish which port is the focus, master or slave.

#### 1.2.4. Avalon-MM Peripherals

An Avalon-MM peripheral is a logical device—either on-chip or offchip—that performs some system-level task, and communicates with other peripherals through one or more Avalon-MM port(s). A peripheral can have any combination of Avalon-MM ports: One slave port, one master port, multiple slave ports, multiple master ports, or a combination of master and slave ports.

### 1.2.5. Transfer

A transfer is a read or write operation of a unit of data, transmitted between an Avalon-MM port and the system interconnect fabric. Avalon-MM transfers transmit up to 1024 bits at a time, and take one or more clock cycles to complete. After a transfer completes, the Avalon-MM port is available for another transaction on the next clock.

Avalon-MM transfers are separated into two fundamental categories: master and slave. Avalon-MM maser ports initiate master transfers to the system interconnect fabric. Avalon-MM slave ports respond to slave transfer requests from the system interconnect fabric. The perspective of a transfer is always with respect to the Avalon-MM port: Master ports only perform master transfers, and slave ports only perform slave transfers.

# 1.2.6. Master-Slave Pair

A master-slave pair refers to a master port and a slave port connected via the system interconnect fabric during a data transfer. During a transfer, the master port's control and data signals pass through the system interconnect fabric and interact with the slave port.

## 1.2.7. Cycle

A cycle is a basic unit of one clock period, which is defined from risingedge to rising-edge of the clock associated with the particular port. The shortest duration of an Avalon-MM transfer is one cycle.

# 2. Avalon-MM Signals

This section defines the signals used by the Avalon-MM interface. The Avalon-MM interface specification defines the possible types of signals that an Avalon-MM peripheral can use, such as address, data, chipselect, etc. An Avalon-MM peripheral design can include any signal type, depending on the requirements for the interface to the peripheral logic.

The Avalon-MM interface specification defines the behavior of the Avalon-MM signal types. Each signal in an Avalon-MM master or slave port corresponds to exactly one Avalon-MM signal type. An Avalon-MM port can use only one instance of each signal type. Avalon-MM signal types are classified as either slave signals or master signals, depending on whether the Avalon-MM port is a master or slave. Certain signal types exist in both master and slave port interfaces, but their behavior is different, depending on the port type.

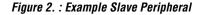

For example, consider the 16-bit output-only general-purpose I/O peripheral shown in Figure 2. This simple Avalon-MM peripheral needs only to respond to transfer requests to receive data. Therefore, it uses only Avalon-MM slave signals for write transfers, and no signals for read transfers.

An Avalon-MM peripheral can also include custom, application-specific signals that are not associated with an Avalon-MM interface, such as the pio\_out signal shown in Figure 2. Application-specific signals connect to logic outside the Avalon-MM system and do not directly interface to system interconnect fabric.

# 2.1. Complete List of Signal Types

Table 1 on page 15 lists the signal types that comprise the Avalon-MM interface for slave ports. Table 2 on page 19 lists the signal types that comprise the Avalon-MM interface for master ports. For each available signal type the tables provide:

The signal type name

- The possible widths of the signal

- The direction of the signal from the perspective of the peripheral

- Whether or not the signal type is required on an Avalon-MM port

- A brief description of the purpose and function of the signal type, and any special usage requirements

Table 1 and Table 2 categorize each signal by the transfer property that uses the signal. For details, refer to Transfer Properties on page 26.

| Signal Type | Width         | Direction      | Required | Description                                                                                                                                                         |

|-------------|---------------|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Fund          | lamental Signa | ls       | ·                                                                                                                                                                   |

| clk         | 1             | In             | No       | Synchronization clock for<br>the Avalon-MM slave<br>interface. All signals are<br>synchronous to clk.<br>Asynchronous slave ports<br>can omit clk.                  |

| chipselect  | 1             | In             | No       | Chip-select signal to the<br>slave port. The slave port<br>ignores all other Avalon-<br>MM signal inputs unless<br>chipselect is asserted.                          |

| address     | 1-32          | In             | No       | Address lines from the<br>system interconnect fabric<br>to the slave port. Specifies<br>a word offset into the slave<br>address space.                              |

| read        | 1             | In             | No       | Read-request signal to the<br>slave port. Not required if<br>the slave port never<br>outputs data.<br>If used, readdata or<br>data must also be used.               |

| readdata    | 1-1024 (1)(2) | Out            | No       | Data lines to the system<br>interconnect fabric for read<br>transfers. Not required if<br>the slave port never<br>outputs data.<br>If used, data cannot be<br>used. |

| Signal Type     | Width                     | Direction      | Required | Description                                                                                                                                                                                                                   |

|-----------------|---------------------------|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Fund                      | damental Signa | ls       |                                                                                                                                                                                                                               |

| write           | 1                         | In             | No       | Write-request signal to the<br>slave port. Not required if<br>the slave port never<br>receives data from a<br>master.<br>If used, writedata or<br>data must also be used,<br>and writebyteenable<br>cannot be used.           |

| writedata       | 1-1024 (1)(2)             | In             | Νο       | Data lines from the system<br>interconnect fabric for write<br>transfers. Not required if<br>the slave port never<br>receives data.<br>If used, write or<br>writebyteenable<br>must also be used, and<br>data cannot be used. |

| byteenable      | 2,4,8, 16, 32,<br>64, 128 | In             | No       | Byte-enable signals to<br>enable specific byte lane(s)<br>during transfers on ports of<br>width greater than 8 bits.<br>If used, writedata must<br>also be used, and<br>writebyteenable<br>cannot be used.                    |

| writebyteenable | 2,4,8,16, 32,<br>64, 128  | In             | No       | Equivalent to the logical<br>AND of the byteenable<br>and write signals.<br>If used, writedata must<br>also be used. write and<br>byteenable cannot be<br>used.                                                               |

| begintransfer   | 1                         | In             | No       | Asserted during the first<br>cycle of every transfer.<br>Usage is peripheral-<br>specific.                                                                                                                                    |

| Signal Type        | Width | Direction        | Required | Description                                                                                                                                                         |

|--------------------|-------|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | Fu    | ndamental Signa  | ls       |                                                                                                                                                                     |

| waitrequest        | 1     | Out              | No       | Used to stall the system<br>interconnect fabric when<br>the slave port is not able to<br>respond immediately.                                                       |

|                    |       | Pipeline Signals |          |                                                                                                                                                                     |

| readdatavalid      | 1     | Out              | No       | Used for pipelined read<br>transfers with variable<br>latency. Marks the rising<br>clock edge when the slave<br>asserts valid readdata.                             |

|                    |       | Burst Signals    |          |                                                                                                                                                                     |

| burstcount         | 2-32  | In               | No       | Used for burst transfers.<br>Indicates the number of<br>transfers in a burst.<br>When used,<br>waitrequest must also<br>be used.                                    |

| beginbursttransfer | 1     | In               | No       | Asserted for the first cycle<br>of a burst to indicate when<br>a burst transfer is starting.<br>Usage is peripheral-<br>specific.                                   |

|                    | Flo   | ow Control Signa | ls       |                                                                                                                                                                     |

| readyfordata       | 1     | Out              | No       | Used for transfers with flow<br>control. Indicates that the<br>peripheral is ready for a<br>write transfer.                                                         |

| dataavailable      | 1     | Out              | No       | Used for transfers with flow<br>control. Indicates that the<br>peripheral is ready for a<br>read transfer.                                                          |

| endofpacket        | 1     | Out              | No       | Used for transfers with flow<br>control. Indicates an end-<br>of-packet condition to the<br>system interconnect fabric<br>Implementation is<br>peripheral specific. |

| Signal Type  | Width      | Direction        | Required | Description                                                                                                                                                     |

|--------------|------------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Fu         | ndamental Signa  | ls       |                                                                                                                                                                 |

|              |            | Tristate Signals |          |                                                                                                                                                                 |

| data         | 1-1024 (1) | Bi-directional   | No       | Bidirectional read and write<br>data for tristate slave ports<br>If used, readdata and<br>writedata cannot be<br>used.                                          |

| outputenable | 1          | In               | No       | Output-enable signal for<br>the data lines. When<br>deasserted, tristate slave<br>port must not drive its<br>data lines.<br>If used, data must also be<br>used. |

|              |            | Other Signals    |          |                                                                                                                                                                 |

| irq          | 1          | Out              | No       | Interrupt request. A slave<br>port asserts irq when it<br>needs to be serviced by a<br>master.                                                                  |

| reset        | 1          | In               | No       | Peripheral reset signal.<br>When asserted, slave<br>peripheral must enter a<br>deterministic reset state.                                                       |

| resetrequest | 1          | Out              | No       | Allows the peripheral to<br>reset the entire Avalon-MM<br>system. The result is<br>immediate.                                                                   |

(A) If the slave port uses dynamic bus sizing, this signal's width must be a power of two.

(B) If a slave port uses both readdata and writedata, the width of both signals must be equal.

The Avalon-MM interface specification does not mandate the presence of any particular signal in an Avalon-MM slave port.

| Signal Type         | Width                                     | Direction | Required | Description                                                                                                                                                                                                      |  |  |

|---------------------|-------------------------------------------|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Fundamental Signals |                                           |           |          |                                                                                                                                                                                                                  |  |  |

| clk                 | 1                                         | In        | Yes      | Synchronization clock for<br>the Avalon-MM slave<br>interface. All signals are<br>synchronous to clk.                                                                                                            |  |  |

| waitrequest         | 1                                         | In        | Yes      | Forces the master port to<br>wait until the system<br>interconnect fabric is ready<br>to proceed with the transfer                                                                                               |  |  |

| address             | 1-32                                      | Out       | Yes      | Address lines from the<br>master port to the system<br>interconnect fabric.<br>The address signal<br>represents a byte address.<br>However, the master port<br>must assert address on<br>word boundaries only.   |  |  |

| read                | 1                                         | Out       | No       | Read request signal from<br>master port. Not required if<br>master port never performs<br>read transfers.<br>If used, readdata or data<br>must also be used.                                                     |  |  |

| readdata            | 8,16,32,64,<br>128, 256, 512,<br>1024 (1) | In        | No       | Data lines from the system<br>interconnect fabric for read<br>transfers. Not required if the<br>master port never performs<br>read transfers.<br>If used, read must also be<br>used, and data cannot be<br>used. |  |  |

| write               | 1                                         | Out       | No       | Write request signal from<br>master port. Not required if<br>the master port never<br>performs write transfers.<br>If used, writedata or<br>data must also be used.                                              |  |  |

| Signal Type   | Width                                     | Direction     | Required | Description                                                                                                                                                                                                       |

|---------------|-------------------------------------------|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Funda                                     | mental Signa  | als      |                                                                                                                                                                                                                   |

| writedata     | 8,16,32,64,<br>128, 256, 512,<br>1024 (1) | Out           | No       | Data lines to the system<br>interconnect fabric for write<br>transfers. Not required if the<br>master port never performs<br>write transfers.<br>If used, write must also<br>be used, and data cannot be<br>used. |

| byteenable    | 2,4,8, 16, 32,<br>64, 128                 | Out           | No       | Byte-enable signals to<br>enable specific byte lane(s)<br>during transfers on ports of<br>width greater than 8 bits.<br>The master port must assert<br>all byteenable lines<br>during read transfers.             |

|               | Pipe                                      | eline Signals |          |                                                                                                                                                                                                                   |

| readdatavalid | 1                                         | In            | No       | Used for pipelined read<br>transfers with latency.<br>Indicates that valid data<br>from the system<br>interconnect fabric is<br>present on the readdata<br>lines. Required if the master<br>is pipelined.         |

| flush         | 1                                         | Out           | No       | Used for pipelined read<br>transfers. The master port<br>asserts flush to clear any<br>pending transfers in the<br>pipeline.                                                                                      |

|               | Bu                                        | ırst Signals  | 1        | 1                                                                                                                                                                                                                 |

| burstcount    | 2-32                                      | Out           | No       | Used for burst transfers.<br>Indicates the number of<br>transfers in a burst.                                                                                                                                     |

| Signal Type | Width                                 | Direction     | Required | Description                                                                                                                                                                                                                                                                                                                                                            |

|-------------|---------------------------------------|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Funda                                 | mental Signa  | als      |                                                                                                                                                                                                                                                                                                                                                                        |

| endofpacket | 1                                     | In            | No       | Used for transfers with flow<br>control. Indicates an end-of<br>packet condition from the<br>system interconnect fabric.<br>Implementation is<br>peripheral specific.                                                                                                                                                                                                  |

|             | Tris                                  | state Signals |          |                                                                                                                                                                                                                                                                                                                                                                        |

| data        | 8,16,32,64,<br>128, 256, 512,<br>1024 |               |          | Bidirectional read and write<br>data for tristate master<br>ports.<br>If used, readdata and<br>writedata cannot be<br>used.                                                                                                                                                                                                                                            |

|             | Ot                                    | her Signals   |          |                                                                                                                                                                                                                                                                                                                                                                        |

| irq         | 1, 32                                 | In            | No       | Indicates when one or more<br>slave ports have requested<br>an interrupt. If irq is a 32-<br>bit vector, each line<br>corresponds directly to the<br>irq signal on a slave port,<br>with no inherent assumption<br>of priority. If irq is one bit<br>wide, it is the logical OR of<br>all slave irq signals, and<br>the interrupt priority is<br>encoded on irqnumber. |

| irqnumber   | 6                                     | In            | No       | Indicates the interrupt<br>priority of a slave port<br>asserting its interrupt<br>request. Lower value means<br>higher priority. Used only<br>when the irg signal is one<br>bit wide.                                                                                                                                                                                  |

| reset       | 1                                     | In            | No       | Global reset signal.<br>Implementation is<br>peripheral specific.                                                                                                                                                                                                                                                                                                      |

| Signal Type  | Width | Direction      | Required | Description                                                                                   |

|--------------|-------|----------------|----------|-----------------------------------------------------------------------------------------------|

|              | Fund  | lamental Signa | als      |                                                                                               |

| resetrequest | 1     | Out            | No       | Allows the peripheral to<br>reset the entire Avalon-MM<br>system. The result is<br>immediate. |

(A) If a master port uses both readdata and writedata, the width of both signals must be equal.

The Avalon-MM interface specification only mandates the existence of three signals on an Avalon-MM master port: clk, address, and waitrequest.

# 2.2. Signal Polarity

The signal types listed in Table 1 and Table 2 are active high. The Avalon-MM interface also offers the negated version of each signal type, indicated by appending \_n to the signal type name (e.g., irq\_n, read\_n). This is useful for interfacing to off-chip peripherals that use active-low logic.

# 2.3. Signal Naming Conventions

The Avalon-MM interface specification does not dictate a naming convention for the signals that appear on Avalon-MM peripherals. A signal in an Avalon-MM port can be named the same as its signal type, or it can be named differently to comply with a system-wide naming convention. For example, an Avalon-MM peripheral may have an Avalon-MM slave port with an input signal named clock\_100mhz of type clk.

In the discussion of Avalon-MM transfers in this document, the signal names are the same as the signal type, but this naming convention is not part of the Avalon-MM interface specification.

# 2.4. Signal Sequencing and Timing

This section describes issues related to timing and sequencing of Avalon-MM signals.

#### 2.4.1. Synchronous Interface

The Avalon-MM interface is a synchronous protocol. Each Avalon-MM port is synchronized to a clock provided by the system interconnect fabric. All transfers occur synchronous to the system interconnect fabric clock. All transfers start on a rising clock edge.

A synchronous interface does not necessarily mean that all Avalon-MM signals are registered. Signals may be combinatorial, based on the outputs of registers that are synchronous to the system interconnect fabric clock. Therefore, an Avalon-MM peripheral must not be edge-sensitive to any Avalon-MM signal besides clk. As with any synchronous design, Avalon-MM peripherals must act only in response to signals that are stable at the rising edge of clk, and must produce stable output signals at the rising edge of clk. The Avalon-MM interface specification does not dictate how or when signals transition between clock edges. For this reason, the system interconnect fabric timing diagrams in this document are devoid of explicit timing information.

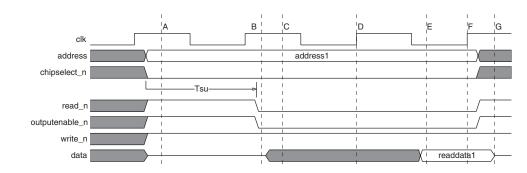

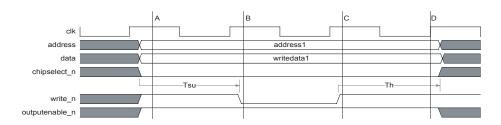

## 2.4.2. Interfacing to Asynchronous Peripherals

It is possible to interface asynchronous peripherals, such as off-chip memory devices, to the system interconnect fabric, but there are a few design considerations. Due to the synchronous operation of the system interconnect fabric, Avalon-MM signals toggle only at intervals equal to the period of the Avalon-MM interface clock. Furthermore, if asynchronous signals are connected directly to system interconnect fabric inputs, the designer must make sure that the signals are stable at the rising edge of clk.

#### 2.4.3. Performance

There is no fixed or maximum performance of the Avalon-MM interface. The interface is synchronous and can be driven at any frequency provided by the system interconnect fabric. The maximum performance is dependent on peripheral design and system implementation.

## 2.4.4. Electrical Characteristics

The Avalon-MM interface specification does not specify any electrical or physical characteristics traditionally required by shared bus implementations.

# 2.5. Transfer Properties

Different Avalon-MM ports have different transfer capabilities, because not all Avalon-MM master or slave ports use the same signal types. The Avalon-MM interface specification defines a set of properties that transfers can exhibit. A specific Avalon-MM master or slave port may support one or more of these properties, depending on the peripheral design. The transfer properties supported by an Avalon-MM peripheral are determined at design time, and do not change from transfer-totransfer.

The Avalon-MM interface specification defines the following transfer properties that Avalon-MM ports can support:

- Wait-states: Fixed or variable (slave only)

- Pipeline: Fixed or variable latency

- Setup and hold time (slave only)

- Burst

- Tristate

Each transfer property is discussed in detail in Slave Transfers on page 27 and Master Transfers on page 42.

The basis for all Avalon-MM transfers is the fundamental read or fundamental write transfer. The fundamental transfer is a transfer that does not exhibit any of the properties listed above. It provides a reference point for describing how each transfer property affects the port and the behavior of the Avalon-MM signals. Using a specific property has one or all of the following effects:

- Changes the behavior of certain signal types

- Requires the use of one or more signal types to implement the property

Avalon-MM ports can support multiple properties simultaneously. For example, a particular Avalon-MM slave port might support pipelined transfers with variable wait-states. Some properties cannot be used in conjunction with other properties; such restrictions are noted in the discussion of each transfer property.

The master and slave ports in a master-slave pair can have different transfer properties. The system interconnect fabric communicates with each port using the port's specified properties, and translates properties from master port to slave port when necessary. In this way, Avalon-MM peripherals can be designed independently of the properties of the rest of the peripherals in the system.

# 3. Slave Transfers

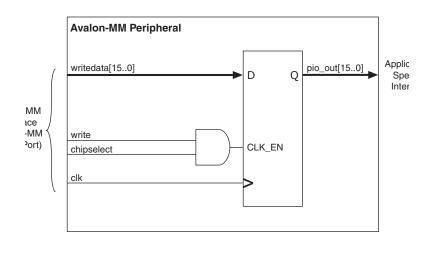

This section defines the behavior of Avalon-MM slave transfers between a slave port and the system interconnect fabric. The interface between the system interconnect fabric and the slave port is the exclusive focus of this section, as shown in Figure 3.

# 3.1. Slave Signal Details

This section describes noteworthy signal behavior that is true for all slave transfers. This section also highlights the flexibility a designer has in choosing Avalon-MM signals to meet the needs of a particular peripheral.

When a transfer is not occurring, the system interconnect fabric ignores all transfer-related output signals from the slave port. For exceptions, refer to Non-Transfer Related Signals on page 84.

#### 3.1.1. address

The address signal for Avalon-MM slave ports is word addressable, specifying a word offset into the slave port's address space. Each slave address value accesses a full unit of data, based on the width of the slave port's readdata and/or writedata signals.

#### 3.1.2. readdata and writedata

readdata and writedata are slave signals that carry the data associated with a transfer. A slave port can use one, none, or both of these signals. The width of these signals can be from 1 to 1024 bits wide. Slave ports must have data width of 8, 16, 32, 64, 128, 256, 512 or 1024. If a slave port uses both readdata and writedata, the widths must be equal for both signals.

### 3.1.3. chipselect, read, and write

The chipselect, read, and write signals are 1-bit inputs to the slave port that indicate when a new read or write transfer begins. These signals have different behavior, depending on what combination of these signals a slave port uses:

Ports with chipselect – If a port uses chipselect, the port must accept a transfer whenever the system interconnect fabric asserts chipselect, and ignore cycles when chipselect is deasserted. The system interconnect fabric always asserts chipselect in combination with read or write.

For a slave port with chipselect, the behavior of read and write depends on the following:

- If the port uses either the read or write signal alone, then the signal has additional significance. In this case, read also means write\_n (i.e. not write), and write also means read\_n (i.e. not read).

- If the port uses chipselect, and both read and write, then chipselect simply acts as a qualifier for the read and write signals. The slave port ignores any cycles while the system interconnect fabric is not asserting chipselect, regardless of the status of read or write.

- Ports without chipselect If a slave port does not use chipselect, then it uses read and/or write alone to determine when a new transfer begins. The system interconnect fabric asserts either read or write to initiate a transfer. The system interconnect fabric deasserts both signals to indicate an idle cycle. The system interconnect fabric never asserts both signals simultaneously.

The timing diagrams of transfers below demonstrate each transfer as an isolated event, while under realistic circumstances transfers can occur in succession. For example, after one read transfer terminates, chipselect and read might remain asserted if another transfer with this slave port follows on the next cycle.

When chipselect is deasserted, a slave port can ignore all input signals, except for reset.

#### 3.1.4. byteenable and writebyteenable

The byteenable signal is a vector signal with one line for every byte lane in writedata. During write transfers to a slave port greater than 8 bits wide, the system interconnect fabric asserts the byteenable signal to specify which byte lane(s) to write. During read transfers to a slave port greater than 8 bits wide, the system interconnect fabric might assert different byteenable lines, indicating which specific bytes the requesting master will use. The slave port can return valid data on just the requested byte lane(s) or on all byte lanes.

When more than one byte lane is asserted, all asserted lanes are guaranteed to be adjacent. The number of adjacent lines must be a power of two, and the specified bytes must be aligned on an address boundary for the size of the data.

Table 3 shows all possible cases of byteenable during write transfers for a 32-bit slave port.

| Table 3. Byte-Enable Example for a 32-Bit Slave Port |                      |  |  |  |

|------------------------------------------------------|----------------------|--|--|--|

| Byteenable [30]                                      | Write Action         |  |  |  |

| 1111                                                 | Write full 32-bits   |  |  |  |

| 0011                                                 | Writes lower 2 bytes |  |  |  |

| 1100                                                 | Writes upper 2 bytes |  |  |  |

| 0001                                                 | Write byte 0 only    |  |  |  |

| 0010                                                 | Write byte 1 only    |  |  |  |

| 0100                                                 | Write byte 2 only    |  |  |  |

| 1000                                                 | Write byte 3 only    |  |  |  |

For example, in the case of a 32-bit port, the valid byteenable combinations are: 0001, 0010, 0100, 1000, 0011, 1100, 1111. The following combinations are not valid: 0000, 0101, 0110, 0111, 1001, 1010, 1011, 1101, 1110.

The writebyteenable signal is the logical AND of the write and byteenable signals. A slave port can use writebyteenable instead of the separate write and byteenable signals to determine when and which byte(s) to write.

### 3.1.5. begintransfer

The begintransfer input signal can be used by any slave port, and provides an easy-to-understand indicator that a new slave transfer has been initiated. The system interconnect fabric asserts the begintransfer signal during the first cycle of each slave transfer. Usage is peripheral-specific. For example, a peripheral's core logic may use begintransfer to determine exactly when an Avalon-MM slave transfer begins, because the address, readenable, writeenable, and chipselect signals do not necessarily change at the start of each data transfer.

# 3.2. Slave Read Transfers

This section defines and demonstrates various Avalon-MM slave read transfers.

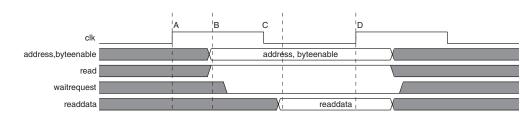

### 3.2.1. Fundamental Slave Read Transfer

The fundamental slave read transfer is the reference point for all other Avalon-MM slave read transfers. It is a read transfer absent any of the transfer properties allowed by the Avalon-MM specification.

The fundamental slave read transfer is initiated by the system interconnect fabric, and transfers one unit of data, the full width of the peripheral's data port, from the slave port to the system interconnect fabric. The transfer completes in a single clock cycle.

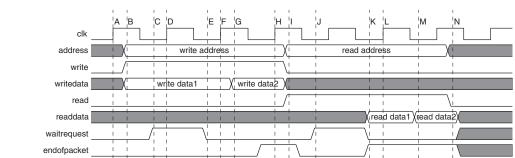

Figure 4 shows an example of the fundamental read transfer. The transfer starts on a rising clock edge, and the read transfer completes on the next rising clock edge. On the first rising edge of clk, the system interconnect fabric passes the address, byteenable, and read signals to the slave port. The system interconnect fabric decodes address internally, and drives the chipselect signal to the slave port. Once chipselect is asserted, the slave port drives readdata as soon as it is available. The system interconnect fabric captures readdata on the next rising edge of clk. For the transfer to complete in a single cycle, the slave port must immediately output the addressed content to the system interconnect fabric before the next rising edge of clk.

Figure 4. Fundamental Slave Read Transfer