# Embedded Image Capture

Alex Glass Albert Jimenez Nektarios Georgios Tsoutsos

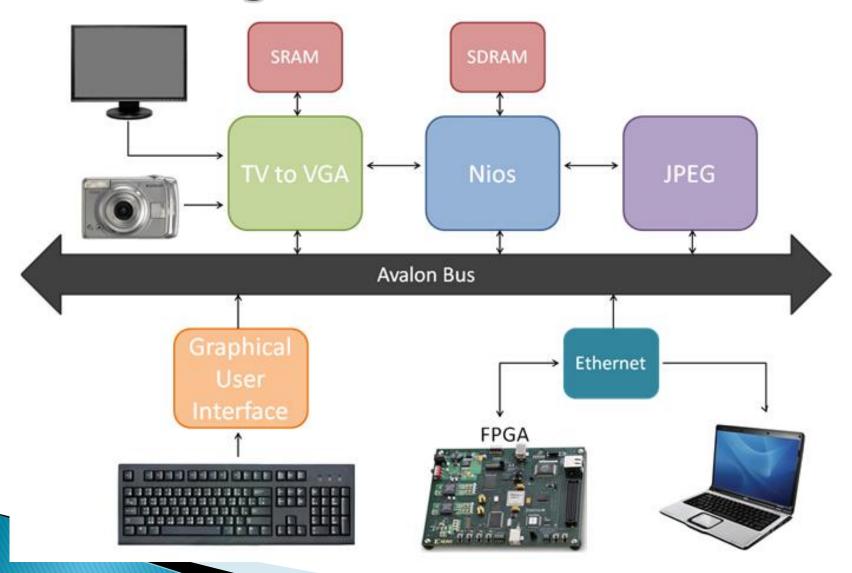

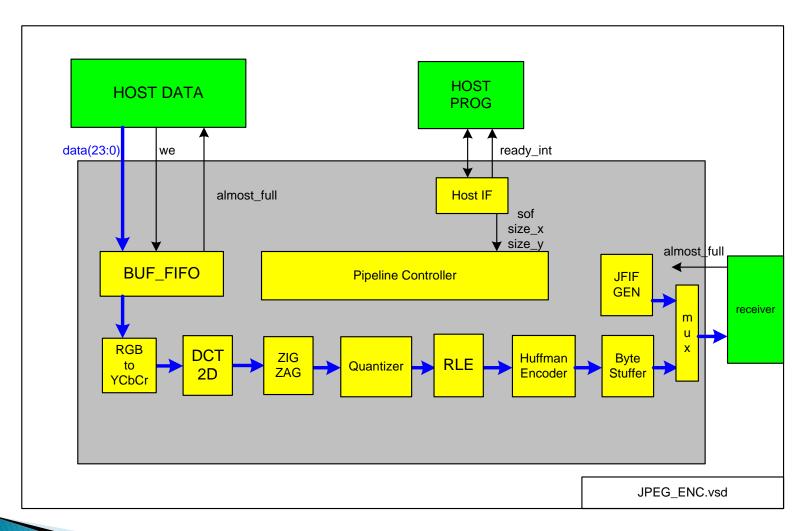

## **Block Diagram**

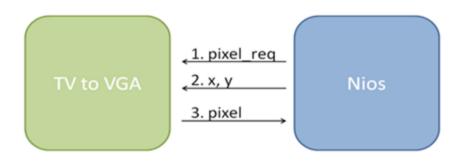

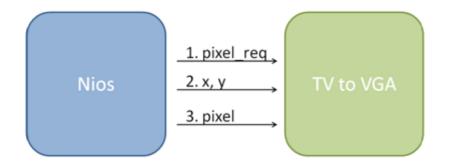

# **Control Signals**

| Keyboard Button   | Functionality                     |

|-------------------|-----------------------------------|

| Spacebar          | Freeze image                      |

| Up and down keys  | Change screen mode                |

| Delete            | Request image deletion            |

| Left key          | Move to next image                |

| Right key         | Move to previous image            |

| Enter             | Save image                        |

| Right Shift Enter | Send image to remote board        |

| Left Shift Enter  | Send compressed image to computer |

# Block Diagram

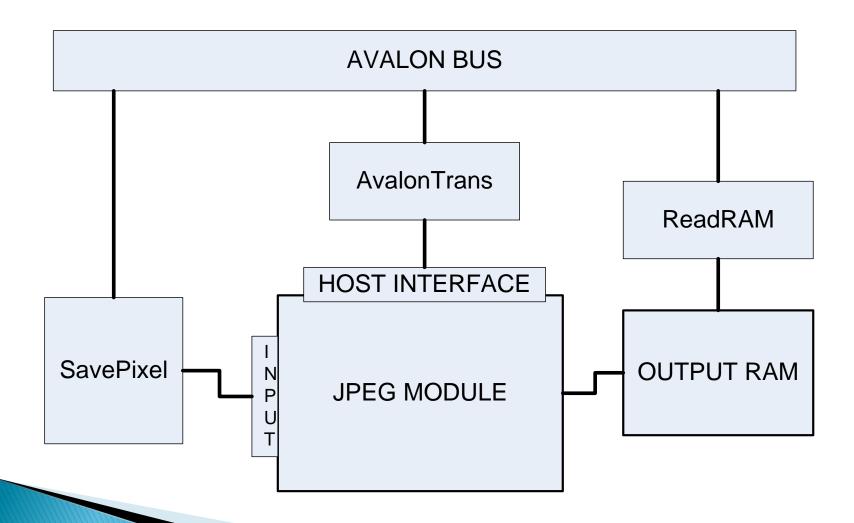

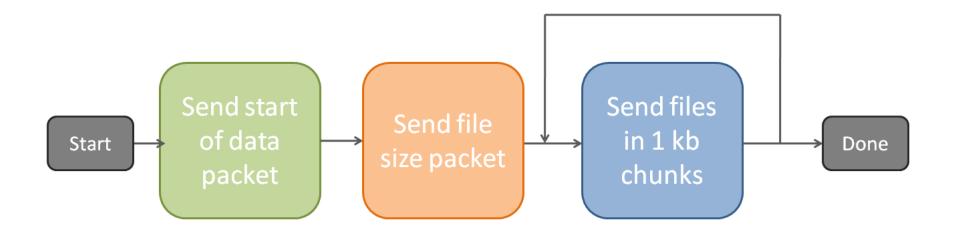

# Sending Images

| 0 | Send x position |

|---|-----------------|

| 1 | Send y position |

| 2 | Send request    |

| 3 | Receive pixel   |

| Address | Functionality   |

|---------|-----------------|

| Number  |                 |

|         |                 |

| 21      | Send x position |

|         |                 |

| 22      | Send y position |

|         |                 |

| 24      | Send request    |

|         |                 |

| 24      | Send pixel      |

|         |                 |

### Image Data Structures

```

unsigned char saved_images[MAX_NUM_IMAGES][3] [IMG_X_SIZE] [IMG_Y_SIZE];

// data structure for linking images

struct image

{

struct image *prev;

int is_taken

int image_num;

struct image *next;

};

```

## **JPEG**

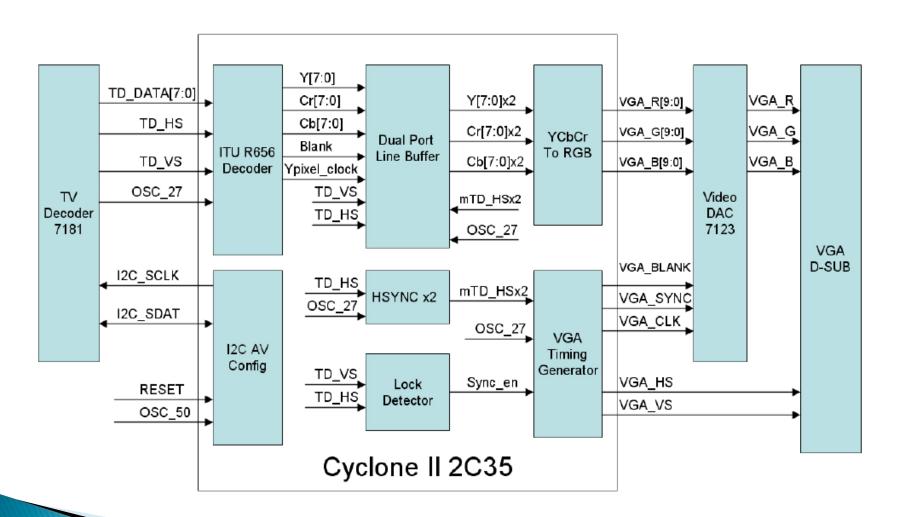

# **Block Diagram**

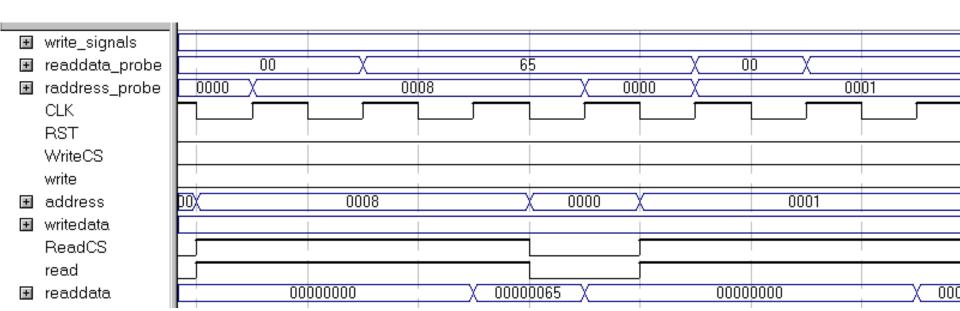

# **Timing**

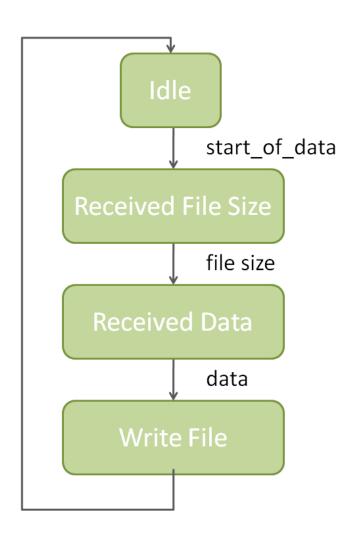

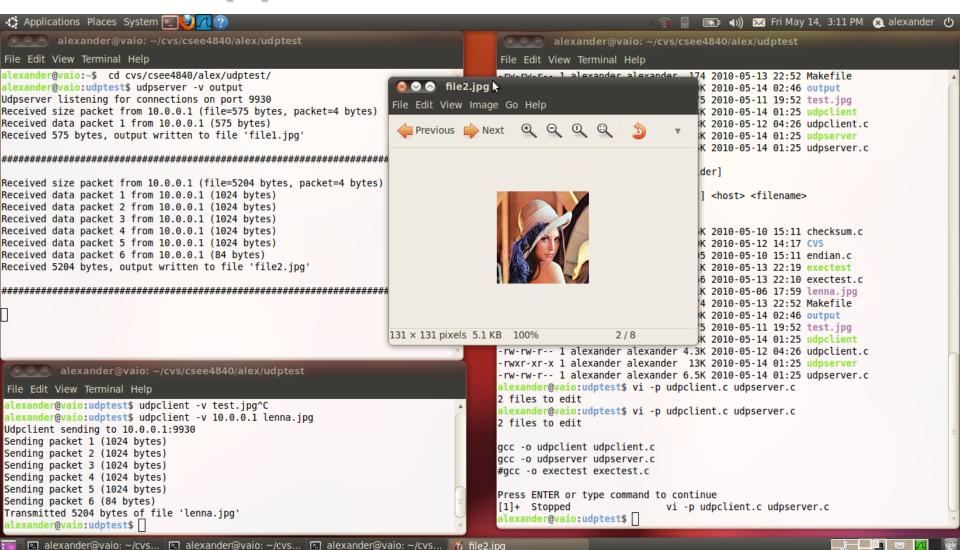

#### **UDP Server**

#### **UDP Client**

### **UDP** Apps

#### Who did what

- Albert -> Capture Master

- Nektarios -> Jpeg Master

- Alex -> Ethernet Master

#### Lessons Learned

- Hardware design is hard

- You cannot debug without simulators

- Jpeg encoding is really tricky

- UDP packets should have checksum and minimum size

- Refreshed our Verilog and gained new VHDL knowledge

- Murphy's law