| Why HDLs?                                                                            |                                                |

|--------------------------------------------------------------------------------------|------------------------------------------------|

| 1970s: SPICE transistor-le                                                           | evel netlists                                  |

| An XOR built from four NAND gates                                                    | Vdd                                            |

| .MODEL P PMOS<br>.MODEL N NMOS                                                       | ┍╼┇ <mark>╺╼</mark> ┇<br>┌╴┇ <mark>╴┍╴┇</mark> |

| .SUBCKT NAND A B Y Vdd Vss<br>ML Y A Vdd Vdd P<br>M2 Y B Vdd Vdd P<br>M3 Y A X Vss N |                                                |

| M4 X B VSS VSS N<br>.ENDS                                                            | B                                              |

| X1 A B I1 Vdd O NAND                                                                 | V35                                            |

| X2 A II IZ Vdd 0 NAND<br>X3 B II II Vdd 0 NAND<br>X4 IZ I3 Y Vdd 0 NAND              |                                                |

|                                                                                      | Digital Design with Synthesizable VHDL – p.    |

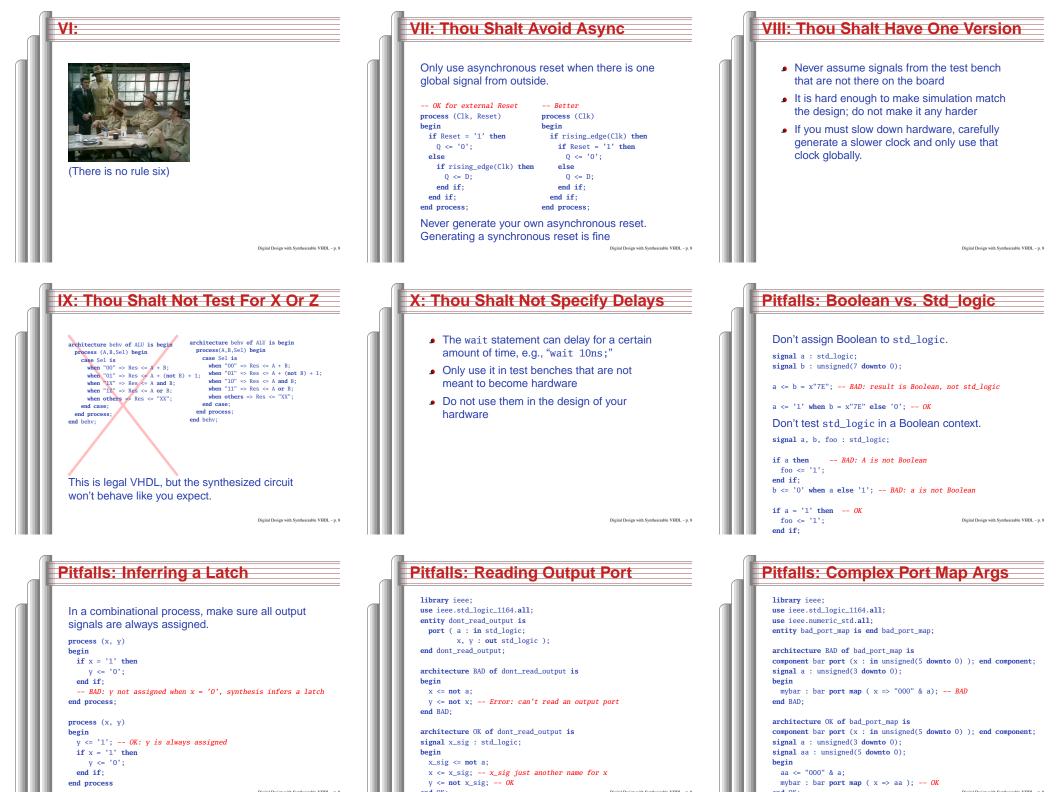

Two Separate but Equal Languages

# Why HDLs?

### **Basic Lexical Rules of VHDL**

- Free-form: space only separates tokens.

- Case-insensitive: "VHDL," "vHdL," and "vhdl" are equivalent.

- Comments: from "---" to the end of the line.

Digital Design with Synthesizable VHDL - p

> Identifiers: [a-zA-Z](\_?[a-zA-Z0-9])\*

Examples: X X\_or\_Y ADDR addr

Illegal: 14M CLK\_4 F00\_

Literals in VHDL

- Decimal integers\*: 1 42 153\_1203

- Based integers\*: 2#1\_0010# 16#F001D#

- Characters: '0' '1' 'X'

- Strings: "101011" "XXXXXX"

- Bit string literals\*: B"1001\_0101" X"95" mean "10010101"

- \*Underscores added for readability are ignored

Verilog and VHDL Verilog: More succinct, less flexible, really messy VHDL: Verbose, very (too?) flexible, fairly messy Part of languages people actually use identical. Every synthesis system supports both.

Digital Design with Synthesizable VHDL - p

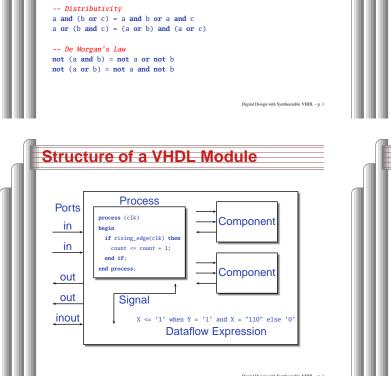

Combinational Logic in a Dataflow Style

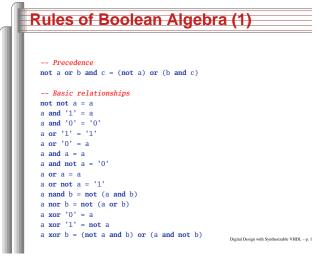

Rules of Boolean Algebra (2)

-- Commutativity

$a \mathbf{or} b = b \mathbf{or} a$

-- Associativity

a and (b and c) = (a and b) and c

$a \mathbf{or} (b \mathbf{or} c) = (a \mathbf{or} b) \mathbf{or} c$

a and b = b and a

### Vectors of Bits

end entity;

s

z

begin

end comb;

| Туре             | Library       | Logic        | Arith.       | Neg. |

|------------------|---------------|--------------|--------------|------|

| std_logic_vector | ieee_std_1164 | $\checkmark$ |              |      |

| unsigned         | numeric_std   | $\checkmark$ | $\checkmark$ |      |

| signed           | numeric_std   |              |              |      |

### Endianness

HE F

The perpetual battle: Is "0" most or least significant?

Little Endian 3210 unsigned(3 downto 0) Big Endian 0123 unsigned(0 to 3)

A Hex-to-seven-segment Decoder

g

Digital Design with Synthesizable VHDL - p. 2

Digital Design with Synthesizable VHDL - p. 2

Arguments on both sides will continue forever.

I suggest using Little Endian for vectors.

| Bina   | ry a     | nd H  | exadecimal in VHDL                                      |

|--------|----------|-------|---------------------------------------------------------|

| Decima | l Binary | Hex   |                                                         |

| 0      | "0"      | x"0"  |                                                         |

| 1      | "1"      | x"1"  | Vector types are arrays of                              |

| 2      | "10"     | x"2"  | std_logic                                               |

| 3      | "11"     |       | otu_iogic                                               |

| 4      | "100"    | x"4"  | Literals are therefore strings                          |

| 5      | "101"    | x"5"  | of 0's and 1's                                          |

| 6      | "110"    | x"6"  | 01 0 5 810 1 5                                          |

| 7      | "111"    |       | from std_logic_1164                                     |

| 8      | "1000"   | x"8"  | <pre>type std_logic_vector is</pre>                     |

| 9      | "1001"   | x"9"  | <pre>array (natural range &lt;&gt;) of std_logic;</pre> |

| 10     | "1010"   | x"A"  |                                                         |

| 11     | "1011"   | x"B"  | from numeric_std                                        |

| 12     | "1100"   | x"C"  | type unsigned is                                        |

| 13     | "1101"   | x"D"  | <pre>array (natural range &lt;&gt;) of std_logic;</pre> |

| 14     | "1110"   | x"E"  |                                                         |

| 15     | "1111"   | x"F"  | type signed is                                          |

| 16     | "10000"  | x"10" | <pre>array (natural range &lt;&gt;) of std_logic;</pre> |

| 17     | "10001"  | x"11" |                                                         |

| 18     | "10010"  | x"12" | Digital Design with Synthesizable VHDL - p. 2           |

| 19     | "10011"  | x"13" | organi teksiyi wan oyuncatanoo (1102 - p. 2             |

|    | library ieee;                                                    |

|----|------------------------------------------------------------------|

| н. | use ieee.std_logic_1164.all;                                     |

| н. | use ieee.numeric_std.all; Provides the unsigned type             |

| н. | entity hex7seg is                                                |

| н. | <pre>port ( input : in unsigned(3 downto 0); A number</pre>      |

| н. | <pre>output : out std_logic_vector(6 downto 0)); Just bits</pre> |

| н. | end hex7seg;                                                     |

| ш. | architecture combinational of hex7seg is                         |

|    | begin                                                            |

|    | <pre>with input select output &lt;=</pre>                        |

| н. | "0111111" when x"0", "0000110" when x"1", Bad style              |

|    | "1011011" when x"2", "1001111" when x"3", one case               |

|    | "1100110" when x"4", "1101101" when x"5", per line               |

|    | "1111101" when x"6", "0000111" when x"7", preferred              |

|    | "1111111" when x"8", "1101111" when x"9",                        |

|    | "1110111" when x"A", "1111100" when x"B",                        |

|    | "0111001" when x"C", "1011110" when x"D",                        |

|    | "1111001" when x"E", "1110001" when x"F",                        |

|    | "XXXXXXX" when others;                                           |

|    | end combinational; Digital Design with Synthesizable VHDL -      |

| Th  | ree-to-eight Decoder                    |

|-----|-----------------------------------------|

|     |                                         |

|     |                                         |

| lik | prary ieee;                             |

| use | e ieee.std_logic_1164. <b>all</b> ;     |

| use | e ieee.numeric_std. <b>all</b> ;        |

| ent | tity dec1_8 is                          |

| рот | rt (                                    |

| 5   | sel : in unsigned(2 downto 0);          |

| r   | ces : out unsigned(7 downto 0));        |

| end | dec1 8:                                 |

|     |                                         |

| arc | chitecture comb of dec1_8 is            |

| beg | zin                                     |

|     | res <= "00000001" when sel = "000" else |

|     | "00000010" when sel = "001" else        |

|     | "00000100" when sel = "010" else        |

|     | "00001000" when sel = "011" else        |

|     | "00010000" when set = 011 else          |

|     | "00100000" when set = 100 erse          |

|     | "01000000 when sel = "10" else          |

|     |                                         |

|     | "10000000";                             |

|     |                                         |

| Two                  | 's Co                                | omp                          | lement                                                                                              |

|----------------------|--------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------|

| Decima<br>-8         | al Binary<br>"1000"                  | Hex<br>x"8"                  | How do you represent negative numbers?                                                              |

| -7<br>-6<br>-5       | "1001"<br>"1010"<br>"1011"           | x"9"<br>x"A"<br>x"B"         | Two's complement produces simpler logic than sign bit alone.                                        |

| -4<br>-3<br>-2<br>-1 | "1100"<br>"1101"<br>"1110"<br>"1111" | x"C"<br>x"D"<br>x"E"<br>x"F" | Idea: Add constant 2 <sup>n</sup> to<br>negative numbers. Simply<br>discard overflow after addition |

| 0<br>1<br>2<br>3     | "0000"<br>"0001"<br>"0010"<br>"0011" | x"0"<br>x"1"<br>x"2"<br>x"3" | or subtraction.<br>An <i>n</i> -bit number represents                                               |

| 4<br>5<br>6          | "0100"<br>"0101"<br>"0110"           | x"4"<br>x"5"<br>x"6"         | $-2^{n-1}$ to $2^{n-1}-1$ .<br>The signed type in                                                   |

| 7                    | "0111"                               | x"7"                         | numeric_std uses this                                                                               |

sign : out unsigned(15 downto 0));

Digital Design with Synthesizable VHDL - p. 1

### Four-to-one mux: when .. else library ieee; use ieee.std\_logic\_1164.all; use ieee.numeric\_std.all; entity multiplexer\_4\_1 is port(in0, in1, in2, in3 : in unsigned(15 downto 0); : in unsigned(1 downto 0); : **out** unsigned(15 **downto** 0)); end multiplexer\_4\_1; architecture comb of multiplexer\_4\_1 is $z \le in0$ when s = "00" else in1 when s = "01" else in2 when s = "10" else in3 when s = "11" else (others => 'X'); -- Shorthand for "all X's"

Digital Design with Synthesizable VHDL - p. 2

| ou    | r-to-one mux: withselect                               |

|-------|--------------------------------------------------------|

|       |                                                        |

|       | ry ieee;                                               |

|       | eee.std_logic_1164. <b>all</b> ;                       |

| use 1 | <pre>eee.numeric_std.all;</pre>                        |

| entit | y multiplexer_4_1 is                                   |

|       | t(in0, in1, in2, in3 : in unsigned(15 downto 0);       |

|       | s0, s1 : in std_logic;                                 |

|       | z : out unsigned(15 downto 0));                        |

| end m | ultiplexer_4_1;                                        |

|       |                                                        |

|       | tecture comb of multiplexer_4_1 is                     |

|       | <pre>l sels : unsigned(1 downto 0);</pre>              |

| begin |                                                        |

|       | s <= s1 & s0; "&" is vector concatenation              |

|       | h sels select would not resolve type if "s1 & s0" here |

| Z     | <= in0 when "00",                                      |

|       | in1 when "01",                                         |

|       | in2 when "10",                                         |

|       | in3 when "11",                                         |

### **Summary of Dataflow Modeling**

• Conditional signal assignment (when...else)

target <=

(expr when expr else)\*

expr ;</pre>

Selected signal assignment (with...select)

with expr select

target <=

(expr when choice (| choice)\*,)\*

expr when choice (| choice)\*;

A choice is a simple expression (i.e., not

logical or comparison) or others.</li>

Note: when does not nest (i.e., it's not an *expr*).

```

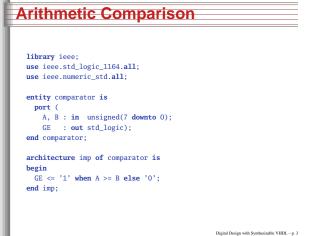

Integer Arithmetic

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity adder is

port (

A, B : in unsigned(7 downto 0);

CI : in std_logic;

SUM : out unsigned(7 downto 0);

C0 : out std_logic);

end adder;

architecture imp of adder is

signal tmp : unsigned(8 downto 0);

begin

tmp <= A + B + ("0" & ci); -- trick to promote ci to unsigned</pre>

SUM <= tmp(7 downto 0);</pre>

CO <= tmp(8);

end imp;

Digital Design with Synthesizable VHDL - p. 2

```

### Tri-state drivers

How to use a pin as both an input and output. Not for internal FPGA signals.

library ieee; use ieee.std\_logic\_1164.all; use ieee.numeric\_std.all;

entity tri\_demo is

port(addr : out unsigned(15 downto 0); -- output only

data : inout unsigned(7 downto 0)); -- bidirectional

end tri\_demo;

architecture rtl of tri\_demo is signal oe : std\_logic; -- output enable: control direction of data signal d\_out : unsigned(7 downto 0); begin

data <= d\_out when oe = '1' else -- Drive data to chip

(others => 'Z'); -- Read data from external chip

end rtl;

Dignal Design with Symbolizable VHDL-p.3

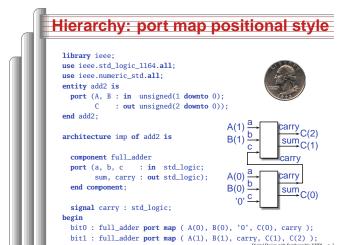

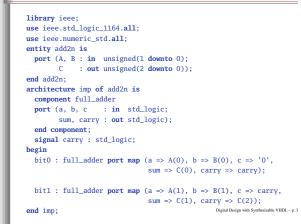

Hierarchy: Instantiating

components (entities)

```

A Very Simple ALU

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity alu is

port (

A, B : in unsigned(7 downto 0);

ADD : in std_logic;

RES : out unsigned(7 downto 0));

end alu:

architecture imp of alu is

begin

RES <= A + B when ADD = '1' else

A - B;

end imp:

Digital Design with Synthesizable VHDL - p. 3

```

### Syntax of Expressions

Logical operators: and or xor nand nor Relational operators: = /= < <= > >= Additive operators: + - & (concatenation) Multiplicative operators: \* / mod rem Others: abs not \*\* (exponentiation) Primaries: identifier literal name(expr to expr) name(expr downto expr) ( choice ( | choice )\* => expr )

Digital Design with Synthesizable VHDL - p. 3

### Hierarchy: port map by-name style

# Combinational Logic in a Procedural Style

Digital Design with Synthesizable VHDL - p. 4

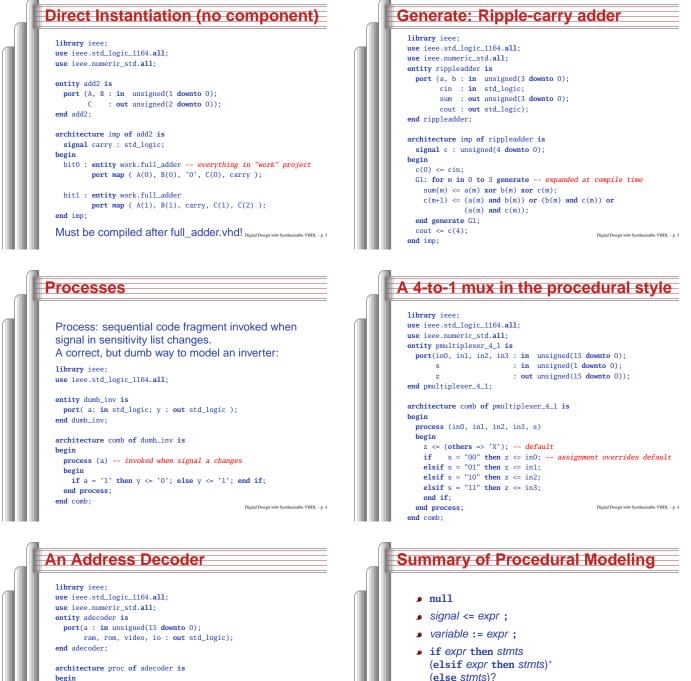

## A 4-to-1 mux using case

library jeee: use ieee.std\_logic\_1164.all; use ieee.numeric\_std.all; entity cmultiplexer\_4\_1 is port(in0, in1, in2, in3 : in unsigned(15 downto 0); : in unsigned(1 downto 0); s : out unsigned(15 downto 0)); Z end cmultiplexer\_4\_1; architecture comb of cmultiplexer\_4\_1 is begin process (in0, in1, in2, in3, s) begin case s is when "00" => z <= in0;</pre> when "01" => z <= in1;</pre> when "10" => z <= in2;</pre> when "11" => z <= in3;</pre> when others  $\Rightarrow z \le (others \Rightarrow 'X');$ end case:

end if;

• case expr is

end case:

(when choices => stmts)\*

Note: when...else and with...select not allowed

architecture proc of adecoder is

begin

process (a)

begin

ram <= '0'; rom <= '0'; video <= '0'; io <= '0';

if a(15) = '0' then ram <= '1'; -- 0000-7FFF

elsif a(14 downto 13) = "00" then video <= '1'; -- 8000-9FFF

elsif a(14 downto 12) = "101" then io <= '1'; -- 8000-PFFF

elsif a(14 downto 13) = "11" then rom <= '1'; -- 8000-FFFF

end if;

end process:</pre>

end if

end process:

| TT 10 | - u |    | chen   | IUL  | ( <b>T</b> | -TI4 | TLOI | $m(uuur)) \leftarrow u$ |

|-------|-----|----|--------|------|------------|------|------|-------------------------|

|       |     |    |        | do   | <=         | di;  |      | write-through           |

| else  | do  | <= | RAM(TO | 0_II | NTE        | GER( | addı | c));                    |

end if end if

end if

end process:

### Variables vs. Signals

| Property   | Variables                                        | Signals                                                           |

|------------|--------------------------------------------------|-------------------------------------------------------------------|

| Scope      | Local to process                                 | Visible throughout architecture                                   |

| Assignment | Felt immediately<br>(e.g., in next<br>statement) | Only visible after<br>clock rises (i.e., pro-<br>cess terminates) |

Lesson: use variables to hold temporary results and state to be hidden within a process. Otherwise, use signals.

Digital Design with Synthesizable VHDL - p. 5

**Coding Moore State Machines** library ieee; use ieee.std\_logic\_1164.all; entity threecount is port(clk, reset, count : in std\_logic; at0 : out std\_logic); end threecount; architecture moore of threecount is type states is (ZERO, ONE, TWO); -- States encoded automatically begin process (clk) variable state : states; begin if rising\_edge(clk) then if reset = '1' then state := ZERO; else case state is when ZERO => if count = '1' then state := ONE; end if; when ONE => if count = '1' then state := TWO: end if: when TWO => if count = '1' then state := ZERO; end if; end case; end if; if state = ZERO then at0 <= '1'; else at0 <= '0'; end if;</pre> end if: Digital Design with Synthesizable VHDL - p. 5 end process; end moore;

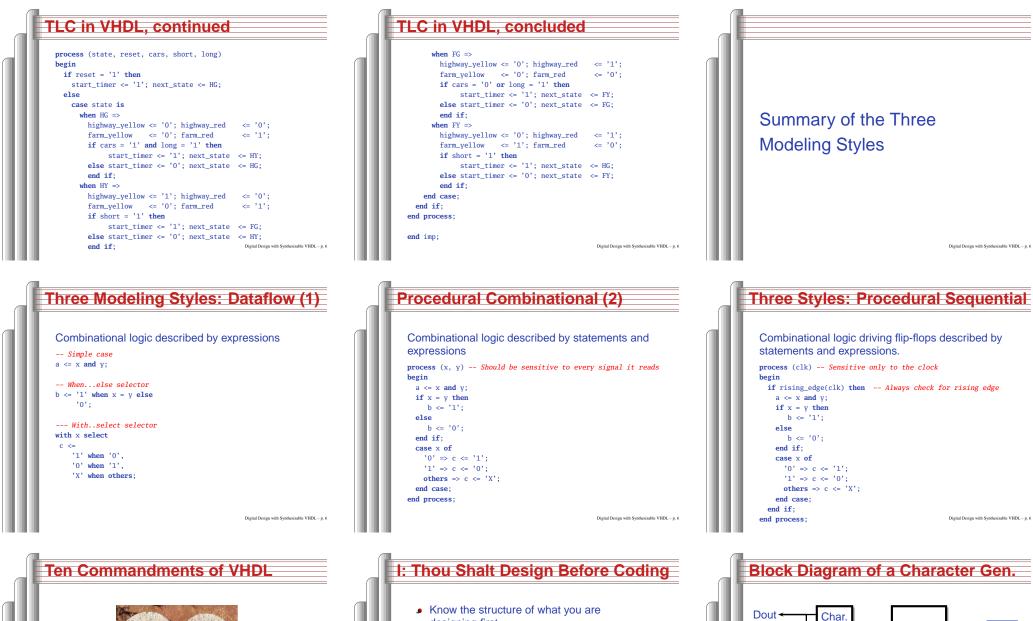

| Coding Mealy State Machines                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>architecture mealy of is<br/>type states is (IDLE, STATE1,);<br/>signal state, next_state : states;<br/>begin<br/>process (clk) Sequential process<br/>begin<br/>if rising_edge(clk) then state &lt;= next_state; end if;<br/>end process;</pre>                                                                         |

| <pre>process (reset, state, i1, i2, ) Combinational process<br/>begin<br/>next_state &lt;= state; Default: hold<br/>if reset = '1' then<br/>next_state &lt;= IDLE;<br/>else<br/>case state is<br/>when IDLE =&gt;<br/>if i1 = '1' then<br/>next_state &lt;= STATE1;<br/>end if;<br/>Dipid Design with Symbolic VUEL-p.6</pre> |

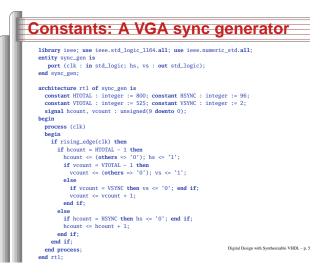

| <pre>when STATE1 =&gt;<br/>Traffic Light Controller in VHDL<br/>library ieee; use ieee.std_logic_1164.all; entity tlc is port (clk, reset : in std_logic; cars, short, long : in std_logic;</pre>                                                                                                                             |

| library ieee;                                     |     |     |                               |        |

|---------------------------------------------------|-----|-----|-------------------------------|--------|

| <br><pre>use ieee.std_logic_1164.all;</pre>       |     |     |                               |        |

| <br>entity tlc is                                 |     |     |                               |        |

| <br>port (clk, reset                              | 1   | in  | <pre>std_logic;</pre>         |        |

| <br>cars, short, long                             | 1   | in  | <pre>std_logic;</pre>         |        |

| <br>highway_yellow, highway_red                   | 1   | out | <pre>std_logic;</pre>         |        |

| <br><pre>farm_yellow, farm_red</pre>              | ÷   | out | <pre>std_logic;</pre>         |        |

| <br>start_timer                                   | ÷   | out | <pre>std_logic);</pre>        |        |

| <br>end tlc;                                      |     |     |                               |        |

|                                                   |     |     |                               |        |

| <br>architecture imp of tlc is                    |     |     |                               |        |

| <br><pre>type states is (HG, HY, FY, FG);</pre>   |     |     |                               |        |

| <br><pre>signal state, next_state : states;</pre> |     |     |                               |        |

| <br>begin                                         |     |     |                               |        |

| <br><pre>process (clk) Sequential pre</pre>       | oce | ess |                               |        |

| <br>begin                                         |     |     |                               |        |

| <br><pre>if rising_edge(clk) then</pre>           |     |     |                               |        |

| <br><pre>state &lt;= next_state;</pre>            |     |     |                               |        |

| end if;                                           |     |     |                               |        |

|                                                   |     |     | Disited Design with Southerin | AL VUD |

The Traffic Light Controller

...

**1**

\_ \_ \_ \_ \_

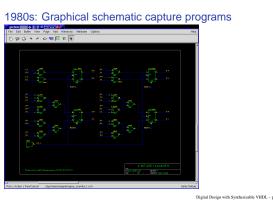

This controls a traffic light at the intersection of a busy highway and a farm road. Normally, the highway light is green but if a sensor detects a car on the farm

road, the highway light turns yellow then red. The farm road light then turns green until there are no cars or after a long timeout. Then, the farm road light turns yellow then red, and the highway light returns to green. The inputs to the machine are the car sensor, a short timeout signal, and a long timeout signal. The outputs are a timer start signal and the colors of the highway and farm road lights.

Source: Mead and Conway, Introduction to VLSI Systems, 1980, p. 85.

M pe targit des aux evands III VШ IV IX IN PROPERTY. VT

- designing first.

- Draw a block diagram of the datapath

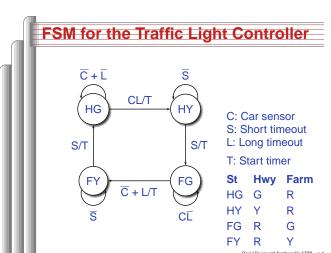

VSYNC

HSYNC

Video

Controller

Load/Shift

Shift Register

BLANK

RAM

2.5K

Font

RAM

1.5K

Din-

Addr-

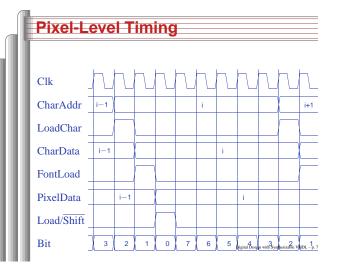

- Understand the timing (draw diagrams)

- Draw bubble-and-arc diagrams for FSMs

- Only once you have a design should you start coding in VHDL

- VHDL is only a way to ask for component

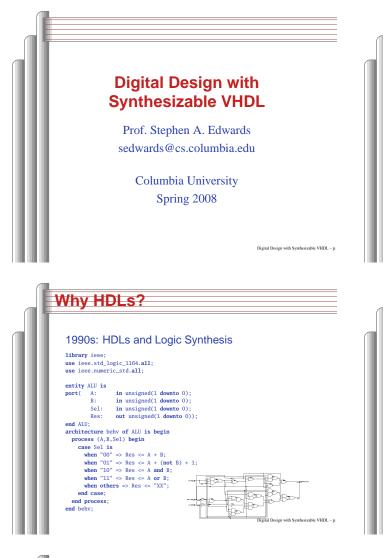

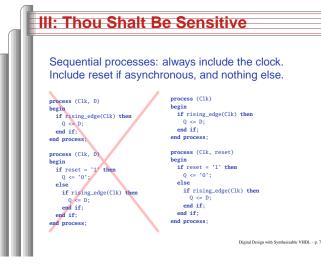

### II: Thou Shalt be Synchronous

- One global clock

- Flip-flops generate inputs to combinational logic, which computes inputs to flip-flops

- Exactly one value per signal per clock cycle

- Do not generate asynchronous reset signals; only use them if they are external

- Edge-triggered flip-flops only. Do not use level-sensitive logic.

- Do not generate clock signals. Use multiplexers to create "load enable" signals on flip-flops.

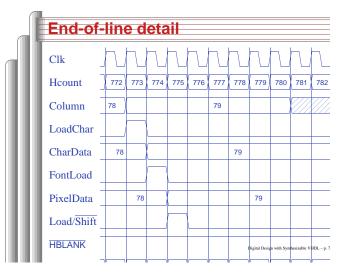

### Start-of-line Detail Clk 140 141 142 143 144 145 146 147 148 149 Hcount 150 Column 0 1 LoadChai CharData 0 FontLoad **PixelData** 0 Load/Shift HBLANK IDL – p. 7

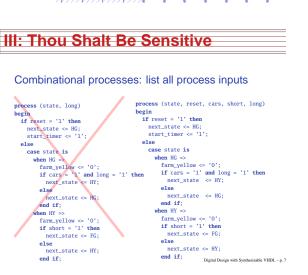

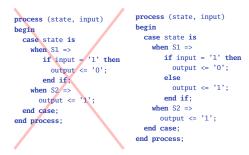

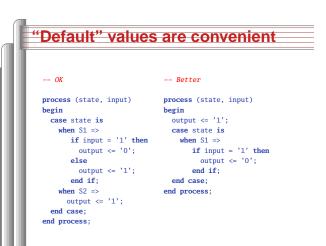

### IV: Thou Shalt Assign All Outputs

Digital Design with Synthesizable VHDL - p. 7

Synthesis infers level-sensitive latches if sometimes you do not assign an output.

# V: Thou Shalt Enumerate States Better to use an enumeration to encode states: type states is (START, RUN, IDLE, ZAPHOD); signal current, next : states; process (current) begin case current is when START => ... when START => ... when START => ... when DLE => ... end case; end process; Running this produces a helpful error: Compiling vhd1 file "/home/cristi/cs4840/lab/main.vhd" in Library work. Entity csysteme compiled. ENUM Process 2012

ccmpiiing vnui life /nome/crist/c54540/la04/main.vnd in Library work Entity csystem> compiled. ERROR:HDLParsers:813 - "/home/cristi/cs4840/lab4/main.vhd" Line 80. Enumerated value zaphod is missing in case. ->